(5k) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| Устройство для анализа структурной характеристики показателя преломления атмосферы | 1991 |

|

SU1800426A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

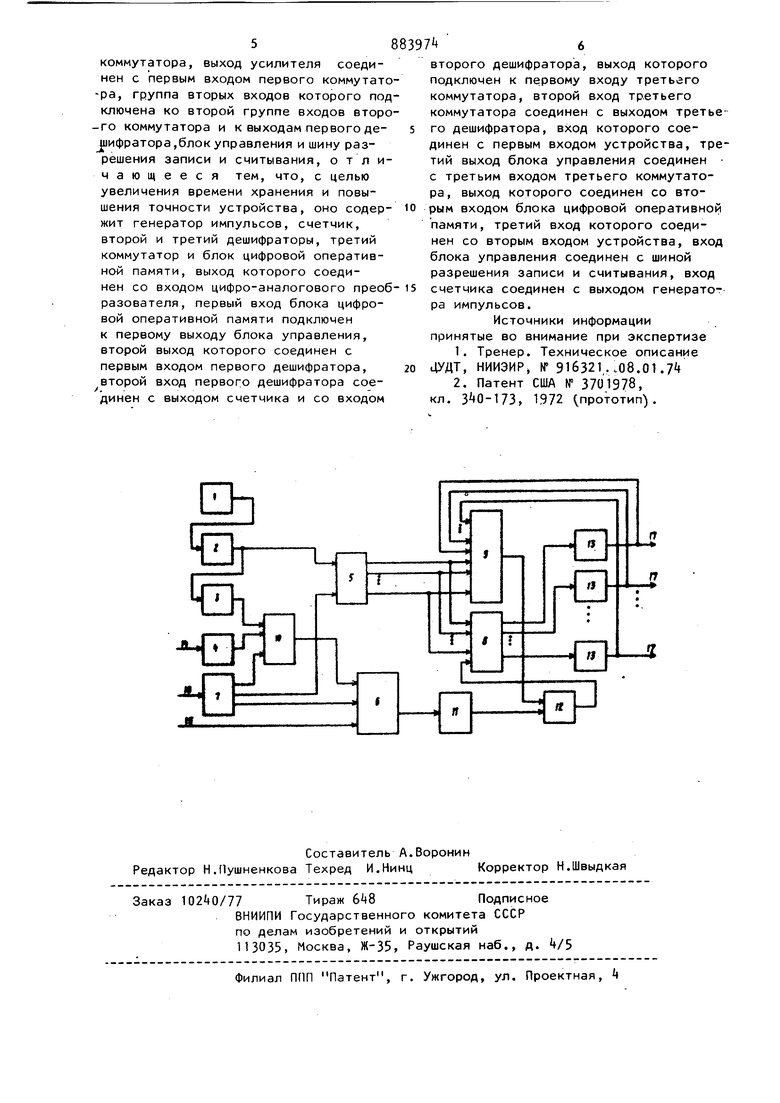

Изобретение относится к гибридной вычислительной технике и предназначено для сопряжения цифровых устройств с аналоговыми.. Известно устройство, которое соде жит буферный регистр, цифро-аналоговый преобразователь и усилитель в каждом канале 01. Однако при большом количестве каналов устройство становится громоз ким. Наиболее близким из известных по технической сущности является аналоговое запоминающее устройство, которое содержит накопительный регистр цифро-аналоговый преобразователь, схему управления коммутаторами, усил тель, аналоговые запоминающие устрой ства, включающие в себя цепи фиксации, модуляторы, возбудители, коммутаторы аналоговых запоминающих устройств и обратных связей (выполнены герконах), источник эталонного напря жения 2. Однако такое устройство не позволяет хранить аналоговые сигналы в течение длительного времени без потери точности из-за разряда конденсаторов в аналоговых запоминающих устройствах. Недостатком устройства является также применение сложных в управлении герконов. Цель изобретения - увеличение времени хранения и повышение точности устройств. Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее блоки аналоговой памяти, входы которых соединены с выходами первого коммутатора, цифро-аналоговый преобразователь, выход которого подключен к первому входу усилителя, второй коммутатор, первая группа входов которого соединена с выходами блоков аналоговой памяти и с выходами устройства, второй вход усилителя соединен с выходом второго коммутатора, выход усилителя соединен с первым входом первого ком мутатора, группа вторых входов котор го подключена ко второй группе входов второго коммутатора и к выходам первого дешифратора, блок управления и шину разрешения записи и считывания, содержит генератор импульсов, счетчик, второй и третий дешифраторы, третий коммутатор и блок цифровой оперативной памяти, выход которого соединен со входом цифро-аналогового преобразователя, первый вход блока цифровой оперативной памяти подключен к первому выходу блока управления, второй выход которого соединен с первым входом первого дешифратора, второй вход первого дешифратора соединен с выходом счетчика и со входом второго дешифратора, выход которого подключен к первому входу третьего коммутатора, второй вход третьего коммутатора соединен с выхо дом третьего дешифратора, вход которого соединен с первым входом устрой ства, третий выход блока управления соединен с третьим входом третьего коммутатора, выход которого соединен со вторым в.ходом блока цифровой оперативной памяти, третий вход которого соединен со вторым входом устройства, вход блока управления соединен с шиной разрешения записи и считывания, вход счетчика соединен с выходо генератора импульсов. На чертеже изображена функциональ ная схема предложенного устройства. Устройство содержит генератор 1 импульсов, счетчик 2, дешифраторы 3 блок 6 цифровой оперативной памяти, блок 7 управления, коммутаторы 8-10, цифро-аналоговый преобразователь 11,, усилитель 1Z, блоки 13 аналоговой па ти, входы 1 + и 15 устройства, шину 1 разрешения записи и считывания и выходы 17 устройства о Устройство работает в режимах зап си и считывания, которые определяются соответствующими командами по вхо ДУ 16. По команде Запись по шине 1б блок 7 через дешифратор 5 закрывает все каналы коммутаторов 8 и 9, переводит блок 6 памяти в запи си и подключает к нему через коммутатор 10 дешифратор k. Поступающие по входу 15 сигналы в двоичном коде записываются в блок 6 памяти по адресам, выбираемым ЦВМ с помощью дешифратора 4. По команде Считывание по шине 16, подаваемой после каждого цикла записи двоичных сигналов,-блок 7 управления переводит блок 6 памяти в режим считывания и подключает к нему через коммутатор 10 дешифратор 3. На выходе дешифратора 3 периодически появляются коды всех адресов блока 6 оперативной памяти, число которых равно числу состояний счетчика 2, подключенного своими выходами к входам дешифратора 3 и дешифратора 5, а также равно числу блоков 13 аналоговой памяти, определяющем число каналов всего устройства и составляет 2, где п - число разрядов счетчика 2. Частота появления кода каждого адреса и выбора соответствующего ему блока 13 равна , где f - частота генератора 1. Записанные по выбранным адресам в блок 6 памяти двоичные сигналы поступают на вход преобразователя 11 , преобразуются в аналоговую форму и подаются на первый вход усилителя 12. В такт с поступлением двоичных сигналов на вход преобразователя 1} дешифратор 5 подключает через коммутатор 8 выход усилителя 12 к выбранному блоку 13, а через коммутатор 9 замыкает обратную связь с выхода выбранного блока 13 на второй вход усилителя 12. Время записи каждого аналогового сигнала в блок 13 аналоговой памяти равно периоду генератора 1. Изобретение позволяет хранить аналоговые сигналы практически неограниченное время с точностью, определяемое преобразователем, используя в для компенсации накопленной погрешности периодическую коррекцию выходных сигналов с помощью хранящихся в оперативном запоминающем устройстве их цифровых эквивалентов. Формула изобретения Аналоговое запоминающее устройство, содержащее блоки аналоговой памяти, входы которых соединены с выходами первого коммутатора, цифро-аналоговый перобразователь, выход которого подключен к первому входу усилителя, второй коммутатор, первая группа входов которого соединена с выходами блоков аналоговой памяти и с выходами устройства, второй вход усилителя соединен с выходом второго коммутатора, выход усилителя соединен с первым входом первого коммутат Рз, группа вторых входов которого по ключена ко второй группе входов втор -го коммутатора и к выходам первого деЛ1ифратора,блок управления и шину разрешения записи и считывания, о т л и чающееся тем, что, с целью увеличения времени хранения и повышения точности устройства, оно содер жит генератор импульсов, счетчик, второй и третий дешифраторы, третий коммутатор и блок цифровой оперативной памяти, выход которого соединен со входом цифро-аналогового прео разователя, первый вход блока цифровой оперативной памяти подключен к первому выходу блока управления, второй выход которого соединен с первым входом первого дешифратора. второй вход первого дешифратора соединен с выходом счетчика и со входом + 6 второго дешифратора, выход которого подключен к первому входу третьего коммутатора, второй вход третьего коммутатора соединен с выходом третьего дешифратора, вход которого соединен с первым входом устройства, третий выход блока управления соединен с третьим входом третьего коммутатора, выход которого соединен со вторым входом блока цифровой оперативной памяти, третий вход которого соединен со вторым входом устройства, вход блока управления соединен с шиной разрешения записи и считывания, вход счетчика соединен с выходом генератот ра импульсов. Источники информации принятые во внимание при экспертизе 1.Тренер. Техническое описание ЦУДТ, НИИЭИР № 916321,.L08.01.7 2.Патент США № 3701978, кл. 3 0-173, 1972 прототип).

Авторы

Даты

1981-11-23—Публикация

1980-03-28—Подача