(54) ЦИФРОВОЙ ДВУХФАЗНЫЙ ГЕНЕРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ

Р.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки фазометров | 1982 |

|

SU1057877A1 |

| Калибратор фазы | 1982 |

|

SU1048424A1 |

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1596270A2 |

| Калибратор фазы | 1983 |

|

SU1138761A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1984 |

|

SU1427549A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Прибор для измерения частотных характеристик | 1986 |

|

SU1335935A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

I

Изобретение относится к радиотехнике . и может быть использовано при построении широкодиапазонных генераторов синусоидальных колебаний, формирующих одновременно два выходных сигнала, фазовый сдвиг между которыми регулируется в широких пределах независимо от частоты выходного сигнала.

Известен цифровой двухфазный генератор синусоидальных сигналов, содержащий блок установки частоты, генератор сетки честоТ, блок установки фазового сдвига, блок совпадения кодов и для каждого из каналов генератора последовательно соединенные счетчик импульсов, постоянное запоминающее устройство, регистр, цифроаналоговый преобразователь и фильтр нижних частот 1.

Генератор этого типа обеспечивает высокую точность воспроизведения фазового сдвига, однако имеет ограниченный диапазон рабочих частот и относительно сложную схему обеспечения фазового сдвига в одном из каналов.

К недостаткам генератора можно отнести также необходимость использования двои .ного колнчества (по числу каналов) таких

сложных и дорогих узлов, как счетчик импульсов, запоминающее устройство и цифроаналоговый преобразователь.

Известен цифровой двухфазный генератор синусоидальных сигналов, содержащий последовательно соединенные задающий генератор, накапливающий сумматор, другой вход которого подключен к выходу блока установки частоты, и сумматор кодов, другой вход которого соединен с выходом блока установки фазового сдвига, последова-тельно соединенные преобразователь кода

10 по квадрантам, постоянное запоминающее устройство, преобразователь кода по знаку, регистр сдвига, другой вход которого подключен ко второму выходу задающего генератора, и цифроаналоговый преобразрва15 тель, а также первый и второй фильтры нижних частот |2j.

Однако известное устройство недостаточно подавляет составляющие спектра, кратные частоте выходного сигнала и использует двойное количество (по числу каналов) 20 сложных и дорогостояп|их узлов.

Цель изобретения - подавление составляющих, кратных частоте выходного,сигнала, при одновременном упрощении.

Для этого в цифровой двухфазный генеp;iTO() скнусонднльных сигналов, содержащий последовательно соединенные задающий генератор, накапливающий сумматор, д)пгой вход которого подключен к выходу б.1ока установки частоты, и сумматор колов, другой вход которого соеди)1ен с выходом блока установки фазового сдвига, последовательно соединенные преобразователь кода по квадрантам, постоянное запоминающее устройство, преобразователь кода но знаку, регистр сдвига, другой вход которого подключен ко второму выходу задающего генератора, и цифроаналоговый преобразователь, а также первый и второй фильтры нижних частот, между первым управляющим выходом задающего генератора и входом преобразователя кода но квадрантам введен коммутатор кодов, кодовые входы которого подключены к выходам накапливающего сумматора и сумматора кодов, а второй выход - ко второму входу преобразователя кода но знаку, а между выходом цифроаналогового преобразователя и входами первого и второго фильтров нижних частот введены соответственно первый и второй блоки выборки и хранения, другие входы которых соединены соответственно со ьторым и третьим управляюпшми выходами задаюп1его генератора.

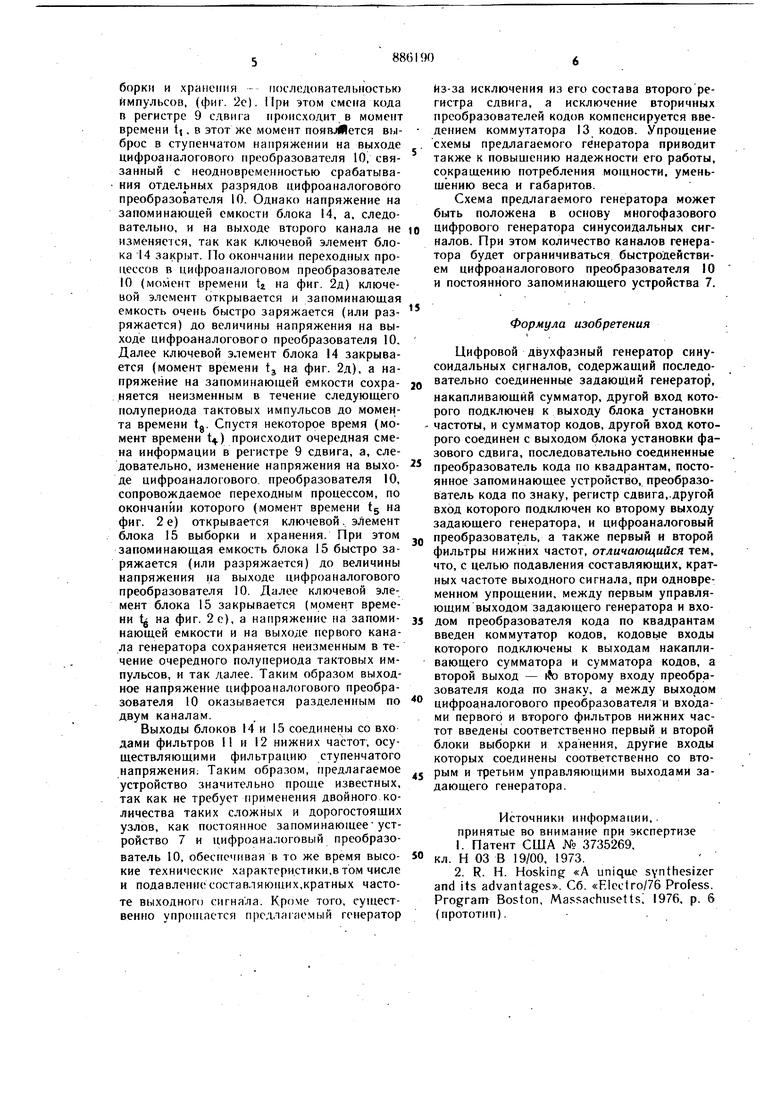

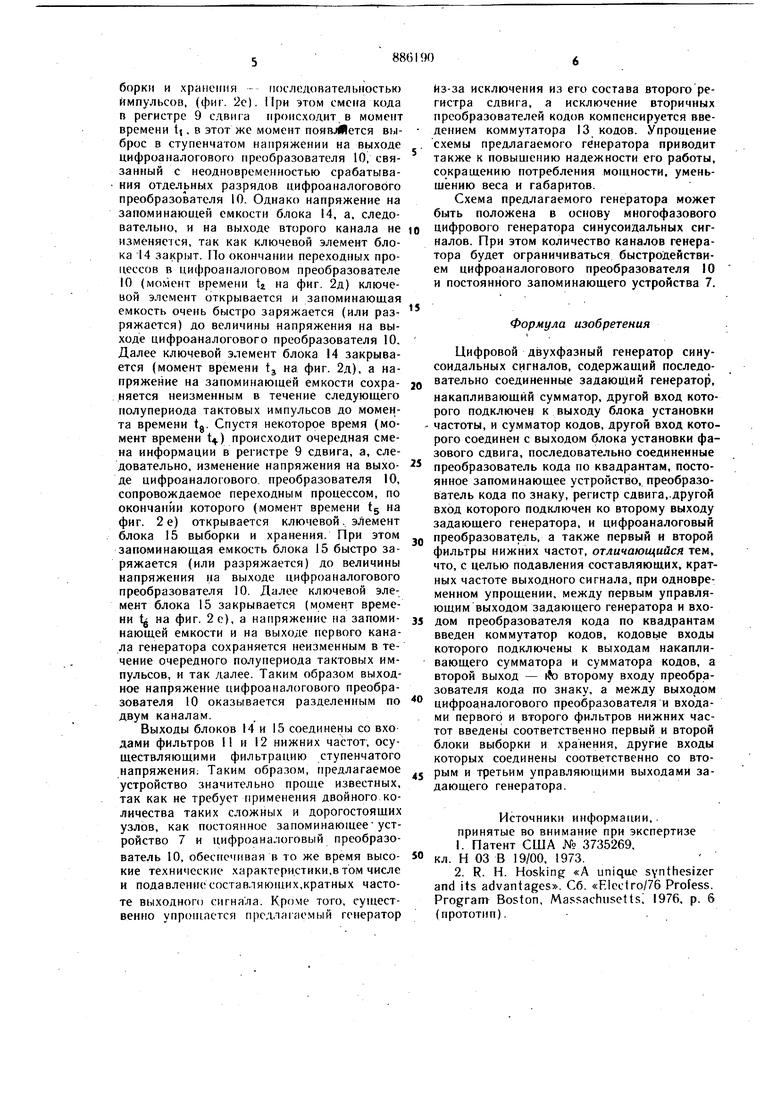

Ма фиг. 1 приведена структурная электрическая схема предлагаемого цифрового двухфазного генератора синусоидальных сигналов; на фиг. 2 - эпюры, поясняющие его работу.

Цифровой двухфазный генератор синусоидальных сигналов содержит блок I установки частоты, блок 2 установки фазового сдвига, задающий генератор 3, накапливающий сумматор 4, сумматор 5 кодов, преобразователь 6 кода по квадратам, постоянное запоминающее устройство 7, преобразователь 8 кода по знаку, регистр 9 сдвига, цифроапалоговый преобразователь 10, фильтры нижних частот II и 12, коммутатор 13 кодов, блоки 14 и 15 выборки и хранения.

Устройство работает следующим образом.

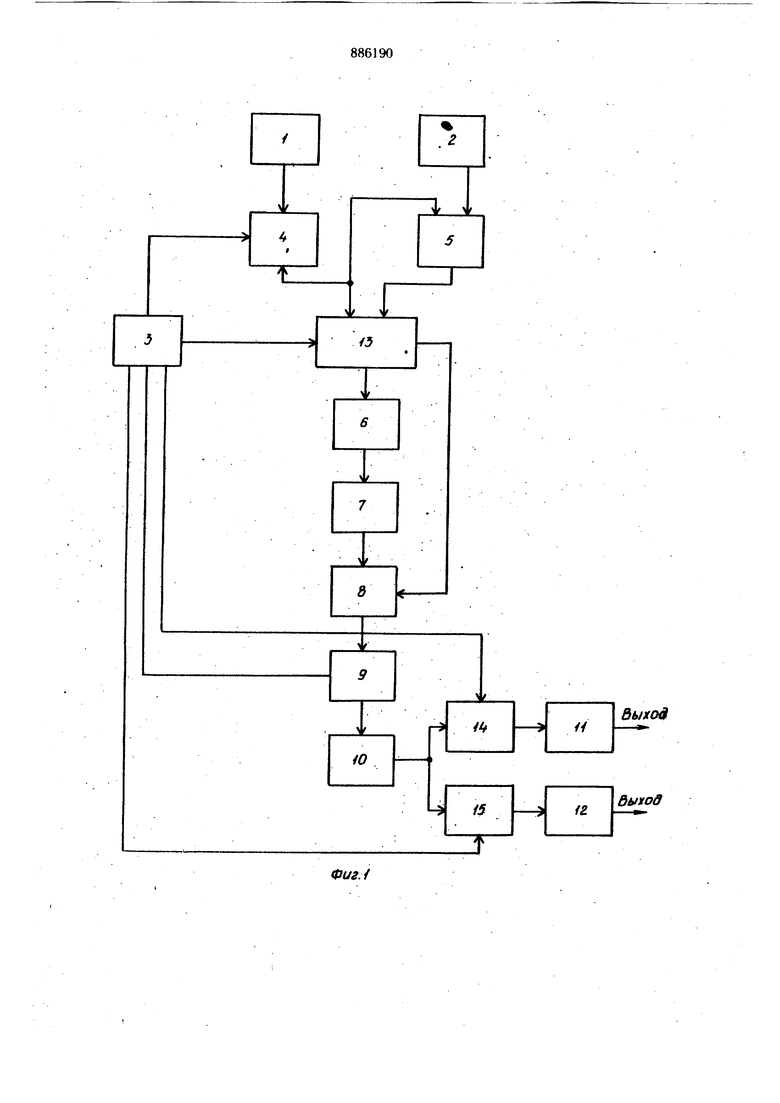

Код требуемой частоты выходного сигнала фиксируется блоком I установки частоты и поступает на накапливающий сумматор 4, имеющий емкость N. Накапливающий сумматор 4 вырабатывает двоичный код числа, соответствующего текущей фазе выходного синусоидального сигнала. Значение этого кода нарастает ,по линейному закону по мере поступления на вход накапливающего сумматора 4 тактовых импульсов (фиг. 2 а) от задающего генератора 3.

Код значении фазового сдвига выходного напряжения во втором канале .задающего генератора 3 фиксируется блоком 2 устаповки фазового сдвиг;, и посупает на сумматор 5 Kn;ui i. гле выполняется арифметическое с.)енне кола установленного

значения фазового сдвига с кодом текущего значепия фазы выходного сигнала, вырабатываемого накапливающим сумматором 4. Код текущего значения фазы выходного сигнала первого канала и код с выхода сумматора 5 кодов, являющийся кодом текущего значения фазы выходного сигнала второго канала генератора, поступают на вход коммутатора 13 кодов, представляющего собой набор схем И-ИЛИ- -НЕ.

Коммутатор 13 кодов в течение интервалов времени tj-t, -rt,0 и так далее, равных половине периода тактовых импульсов (фиг. 26) пропускает на выход код текущего значения, фазы с выхода накапливающего сумматора 4, а в течение интервалов времени t4.- t, tio-tij и так далее (фиг. 2в) - код с выхода сумматора 5 кодов.

Далее преобразователь б кода по квадрантам в течение интервалов времени 1( . -tjg и так далее осуществляет преоб разование по квадрантам кода текущего значения фазы выходного сигнала первого канала, а в течение интервалов времени Ц- ty, , -ti3 и так далее - текущего значения фазы выходного сигнала второго канала. Выходной код преобразователя б кода по квадрантам является адресом, по которому постоянное запоминающее устройство 7 выдает кодированное значение выходного синусоидального напряжения. Преобразователь. 8 кода по знаку преобразует этот код в зависимости от значения знакового разряда, поступающего с выхода коммутатора 13 кодов. Регистр 9 сдвига предназначен для выравнивания задержек в различ.ных разрядах кода выходного напряжения,

поступающего с выхода преобразователя 8 кода по знаку. При этом смена кода в регистре 9 сдвига производится с удвоенной тактовой частотой (фиг. 2г).

В результате в моменты времени t,, t,

t,... на выходе регистра 9 сдвига устанавливается код выходного напряжения второго канала, а в моменты времени t/,, t,o - код выходного напряжения первого канала генератора.

Преобразование кода выходного сигнала в аналоговое напряжение выполняет цифроаналоговый преобразователь 10. При этом в интервале времени ti--t/,, ,p выходное напряжение цифроаналогового прео.бразователя 10 относится ко второ.му каналу генератора, а в интервале времени tj,- t,, t - t.,j - к первому каналу.

Разделение выходного напряжения цифроаналогового преобразователя 10 по каналам производится с помощью блоков И и 15 выборки и хранения, имеющих в своем составе запоминающую емкость и ключевой элемент. Управление блоком 14 выборки и хранения осуществляется посчеловательностью импульсов (фиг. 2д), а блоком 15 выборки и хранения - юслодовательностью импульсов, (фиг. 2с). При этом смена кода в регистре 9 сдвига 1гроисходит в момент времени i. в этот же момент noHBjilleTCH выброс в ступенчатом напряжении на выходе цифроаналогового преобразователя 10, связанный с неодновремепностью срабатывания отдельных разрядов цифроаналоговЬго преобразователя 10. Однако напряжение на запоминающей емкости блока 14, а, следовательно, и на выходе второго канала не изменяется, так как ключевой элемент блока 14 закрыт. По окончании переходных процессов в цифроаналоговом преобразователе 10 (момент времени tj на фиг. 2д) ключевой элемент открывается и запоминающая емкость очень быстро заряжается (или разряжается) до величины напряжения на выходе цифроаналогового преобразователя 10. Далее ключевой элемент блока 14 закрывается (момент времени tj на фиг. 2д), а напряжение на запоминающей емкости сохраняется неизменным в течение следующего полупериода тактовых импульсов до момента времени tg. Спустя некоторое время (момент времени t) происходит очередная смена информации в регистре 9 сдвига, а, следовательно, изменение напряжения на выходе цифроаналогового. преобразователя 10, сопровождаемое переходным процессом, по окончании которого (момент времени tg на фиг. 2 е) открывается ключевой.. элемент блока 15 выборки и хранения. При этом запоминающая емкость блока 15 быстро заряжается (или разряжается) до величины напряжения на выходе цифроаналогового преобразователя 10. Далее ключевой элемент блока 15 закрывается (момент времени t на фиг. 2е), а напряжение на запомииающей емкости и на выходе первого канала генератора сохраняется неизменным в течение очередного полупериода тактовых импульсов, и так далее. Таким образом выходное напряжение цифроаналогового преобразователя 10 оказывается разделенным по двум каналам. Выходы блоков 14 и 15 соединены со вхо дами фильтров II и 12 нижних частот, осуществляющими фильтрацию ступенчатого напряжения Таким образом, предлагаемое устройство значительно проще известных, так как не требует применения двойного ко.личества таких сложных и дорогостоящих узлов, как постоянное запоминающееустройство 7 и цифроаналоговый преобразователь 10, обеспечивая в то же время высокие технические характеристики,в том числе и подавленно составляющих,кратных частоте выходного сигнала. Кроме того, существенно упропшется прсдлгпаемый генератор из-за исключения из его состава второго регистра сдвига, а исключение вторичных преобразователей кодов компенсируется введением коммутатора 13 кодов. Упрощение схемы предлагаемого генератора приводит также к повышению надежности его работы, сокращению потребления мощности, уменьщению веса и габаритов. Схема предлагаемого генератора может быть положена в основу многофазового цифрового генератора синусоидальных сигналов. При этом количество каналов генератора будет ограничиваться быстродействием цифроаналогового преобразователя 10 и постоянного запоминающего устройства 7. Формула изобретения Цифровой двухфазный генератор синусоидальных сигналов, содержащий последовательно соединенные задающий генератор, накапливающий сумматор, другой вход которого подключев к выходу блока установки частоты, и сумматор кодов, другой вход которого соединен с выходом блока установки фазового сдвига, последовательно соединенные преобразователь кода по квадрантам, постоянное запоминающее устройство, преобразователь кода по знаку, регистр сдвита,.другой вход которого подключен ко второму выходу задающего генератора, и цифроаналоговый преобразователь, а также первый и второй фильтры нижних частот, отличающийся тем, что, с целью подавления составляющих, кратных частоте выходного сигнала, при одновременном упрощении, между первым управляющим выходом задающего геиератора и входом преобразователя кода по квадрантам введен коммутатор кодов, кодовые входы которого подключены к выходам накапливающего сумматора и сумматора кодов, а второй выход - Лэ второму входу преобразователя кода гто знаку, а между выходом цифроаналогового преобразователя и входами первого и второго фильтров нижних частот введены соответственно первый и второй блоки выборки и хранения, другие входы которых соединены соответственно со вторым и третьим управляющими выходами задающего генератора. Источники информации,. принятые во внимание при экспертизе 1.Патент США № 3735269, кл. Н 03 В 19/00, 1973. 2.R. Н. Hosking «А unique synthesizer and its advantages. Сб. «FJectro/76 Profess. Program Boston, Massachnsettsi 1976, p. 6 (прототип)..

быход

дыхов

Т

Такт

а

4

ts teiyy /2

П

- t

Чз

Ю

0UZ.i

Авторы

Даты

1981-11-30—Публикация

1980-01-21—Подача