вход регистра памяти кода частоты подключен к первому faicTOBOMy выходу блока управления, а управляющий выход первого дешифратора адреса соединен с управляющим входом регистра памяти кода частоты, первый и: второй информационные выкоды которого соединены с входами соответственно накапливающего сумматора и делителя частоты с переменным коэффициентом деления, второй тактовьй вьгход блока управления соединен с тактовкм входом первого регцстра памяти кода амплитуды, выход которого подклточек к входу аттенюатора, управляющий-выход блока управления соединен с управляющмч входом блока ввода сигналов програм ;- ного управления, информационный вход которого является входом программно- зшравляемого генератора синусоидальных колебаний, отличающийс я тем, что, с целью повьшения точ

кости установки уровня выходных синусоидальных колебаний, в него - введены по.следоэательно сое;диненные блок формирования кода амплитуды, первьй .сумматор, второй дешифратор адреса;, второй регистр памяти кода амплитуды, преобразователь код-а, первый регистр сдвига и второй циф- роаналоговый преобразователь, к опорйому вкоду которого подключея вьжод нсточника опорного напряйсения последовательно соединенные второй регистр сдвига, первый шифратор и второй с; мматор, а также второй шифратор5 группа янформапдаонных входов которого подключена к соответ - ств ггощим кнформацяон1-1ым выходам пре- образовате,Шг кода, вьгкод которого соединен с управляющем входом первого регистра сдвига и первым гдафор- мазционньм входом первого регистра памяти кода амплитуды, второй информационный вход которого соединен с выходом второго сумматора s ззькод второго цифроаналогового преобразо- :вателя соединен с друп-ш вкодом блока сравнения, второй .ркод второго CJTM- матора под1слючен к выходу блока формирования кода амплитуды, третий Гактовьй выкод блока /правления сое- данен с тактовым входом второго ре - гистра памяти кода амплитуды, чет- 1)ер гь1й тактовый выход блока управ™ лений соединен с первым тактовым йходом блока формировйния- кода ампля- з уды пятый тактовый. выход блока уп

равления соединен с вторым тактовым входом блока формирования кода амплитуды, тактовый вход второго регистра сдвига соединен с синхрони- зирутощим выходом дешифратора, управляющих сигналов, а управляющий вход второго регистра сдвига соединен с вторым информационным вькодом блока управления, информацион.ный вход блок формирования кода амплитуды соединен с выходом оперативного запоминания, информационный вход второго регистра памяти кода амплитуды соединен с выходом блока оперативного запоминания, а второй вход перв.ого сумматора соединен с первым информационным выходом блока управления.

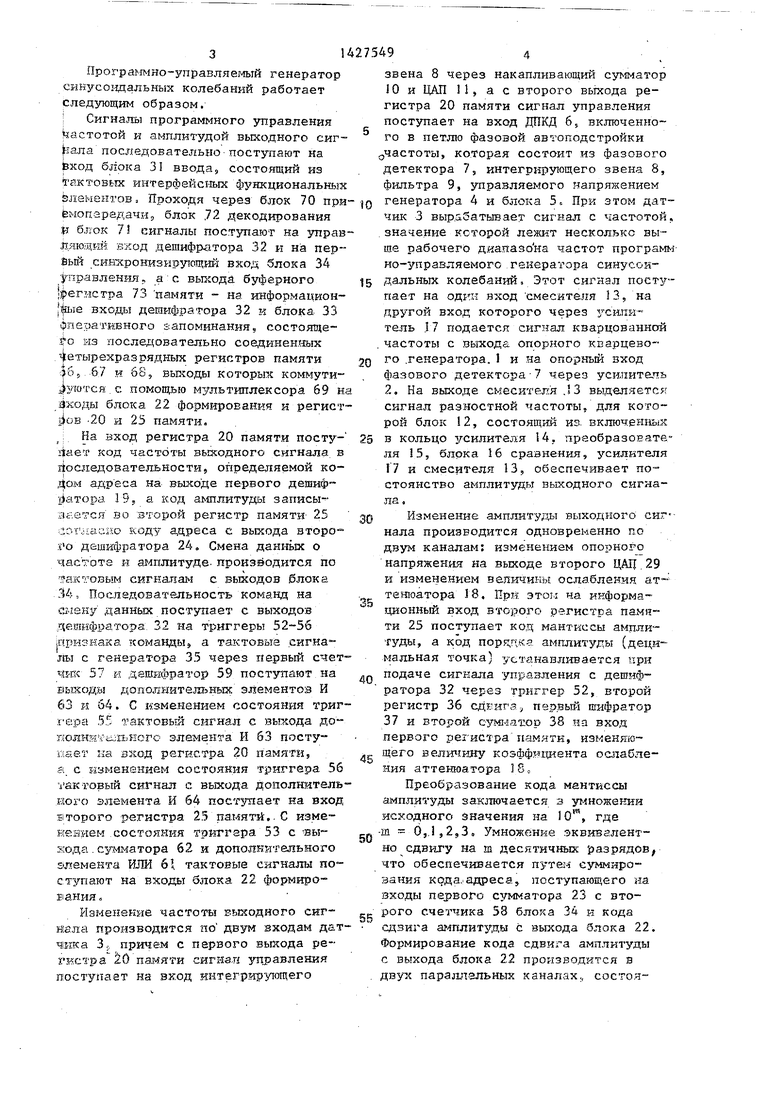

2, Генератор по п. I ., о т л и - ч а.о щ и и .с я тем, что блок формирования кода амплитзгды содержит последовательно соединенные первый элемент ИЛИ, первьй дополнительный регистр сдвига и первый дополнительный регистр памяти, первый, второй и третий ВЫХОДЫ которого соединены с .первыми входами первого, второго и третьего дополнительных элементов ИЛИ, выходы которых соединены с соответствующими входами . третьего шифратора, выходы которого являются выходами блока форми- рорания кода амплитуды, последоза- тельно соединенные первый элемент ИЛИ-НЕ, второй элемент ЙШ, второй дополнительный регистр сдвига и второй дополнительный регистр памяти, первый н второй выходы которого соединены с парвьми входами первого и втсфого элементов К, выходы которых сое/.1,йнены с соотват- ствующш и вторьЯ Ш входами первого и второго дополнительных элементов ИЛИ, а второй вкод третьего дополнительного элемента ИЛИ соединен с третьим выходом второго до- полнителького регистра памяти, вторые входы первого и второго элементов И соединены соответственно с вторым и третьим выходами п ерво- 1ГО дополнительного регистра памяти, входы первого элемента ИЛИ являются входами блока формирования кода амплитуды, первый вход первого элемента ИЛИ соединен с входом элемента апИ-НЕ, а второй, третий и четвертый входы первого элемента ШШ соединены соответственно с вторьв-, третьим и

четвертым входами второго элемента ИЛИ, тактовые входы первого и второго дополнительных регистров сдвига объединены и являются первым тактовым входом блока формирования кода

1427549

амплитуды, а тактовые входы первого ч второго дополнительных регистров памяти объединены и являются вторым тактовым входом блока формирования од Г- ампл и туды.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для ввода информации | 1983 |

|

SU1092486A1 |

| Устройство для ввода и вывода информации | 1980 |

|

SU920692A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство управления электронной вычислительной машиной | 1977 |

|

SU674020A1 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

1

Изобретение относится к радиотехнике и связи, предназнз тено для по- синусоидальных колебаний по сигналам программного таравления и может быть использог ано в автоматизированных .системах измерания и контроля „

Цель изобретения - повьшение точности установки уровня выходных синусоидальных колебаний.

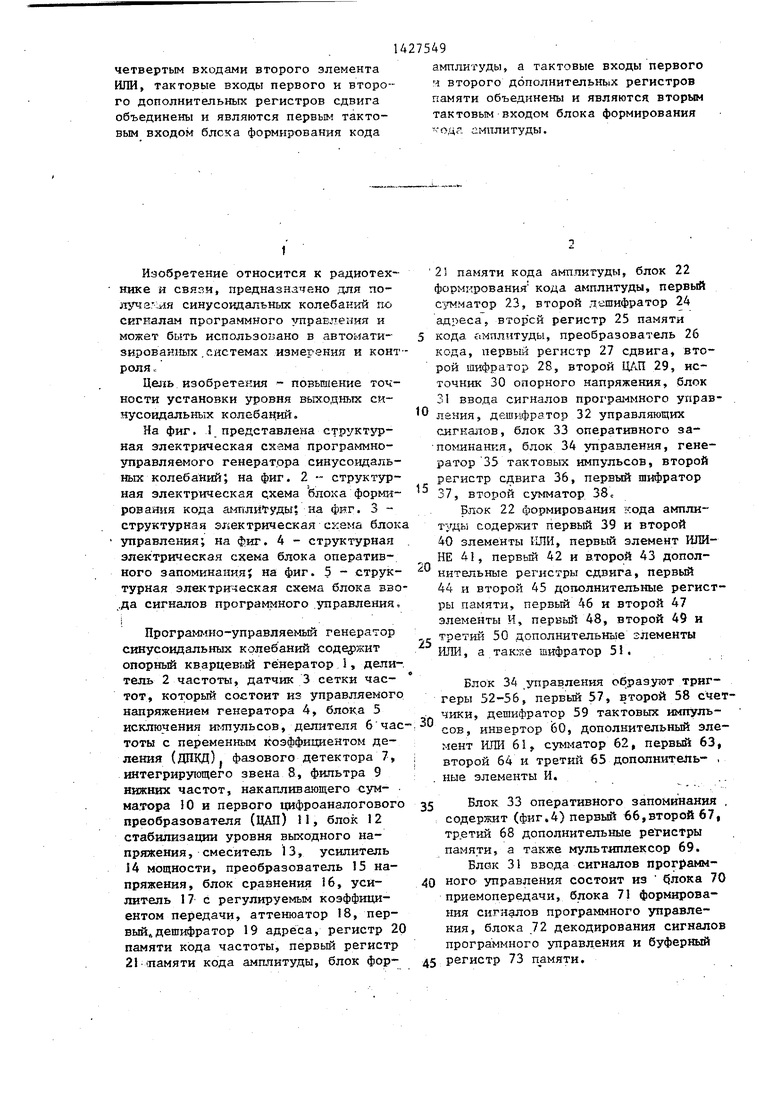

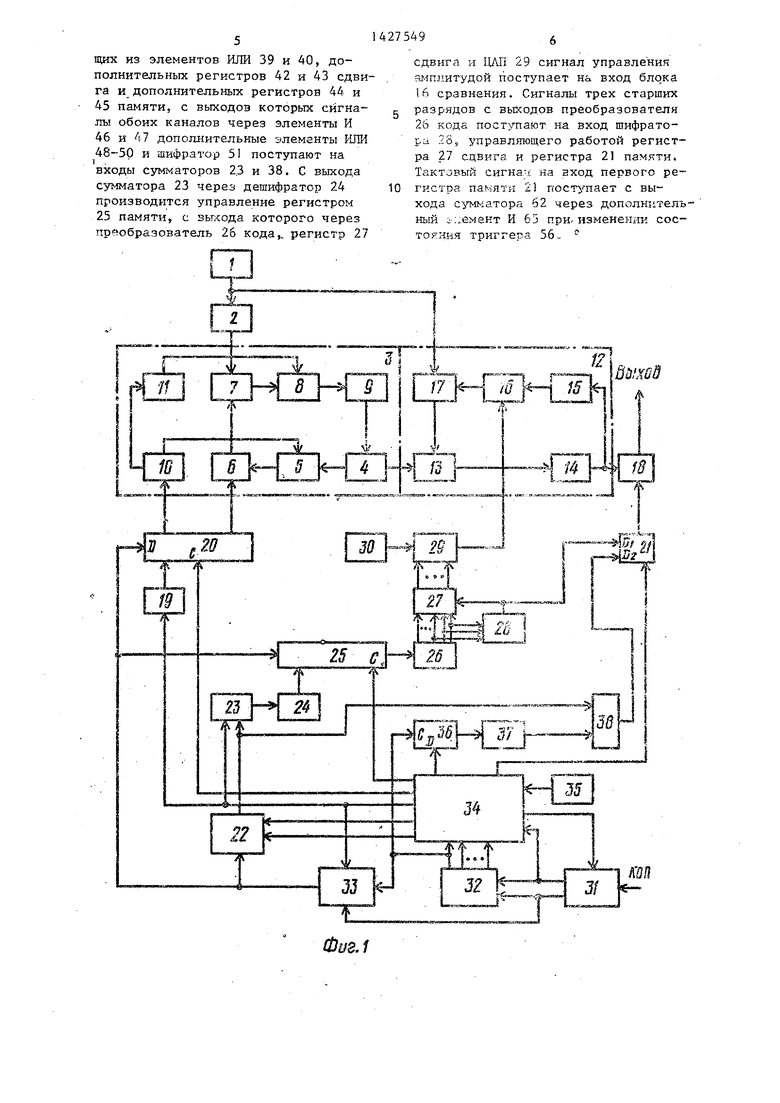

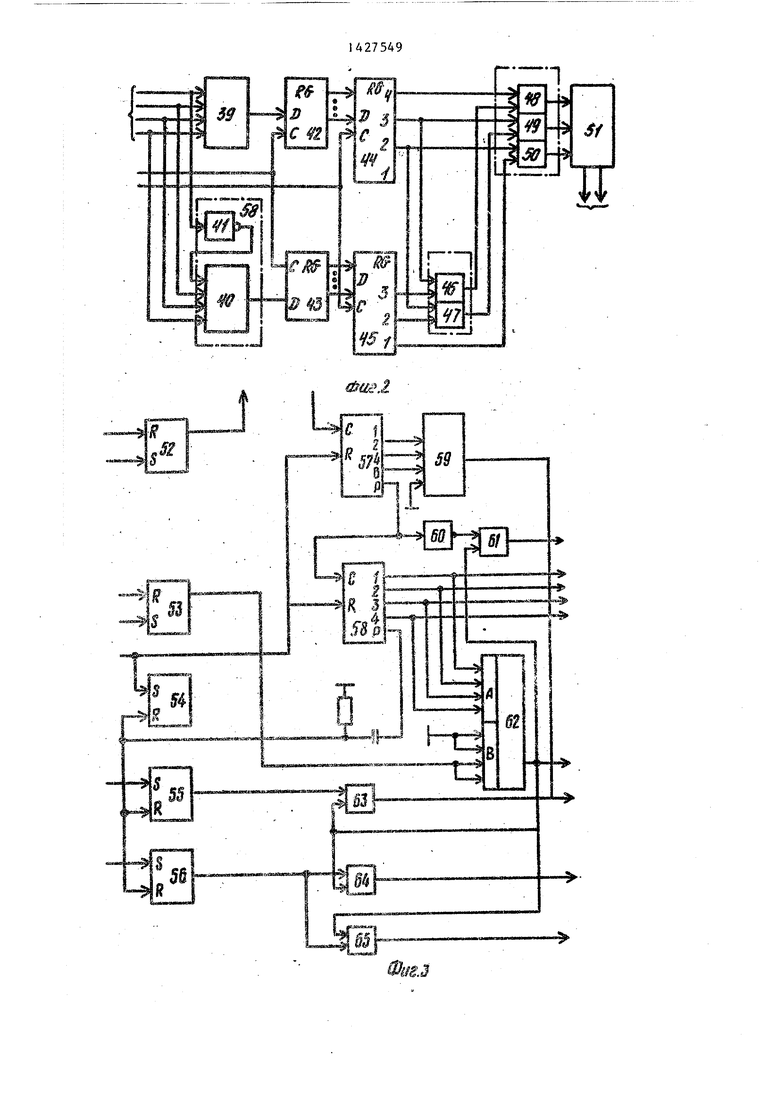

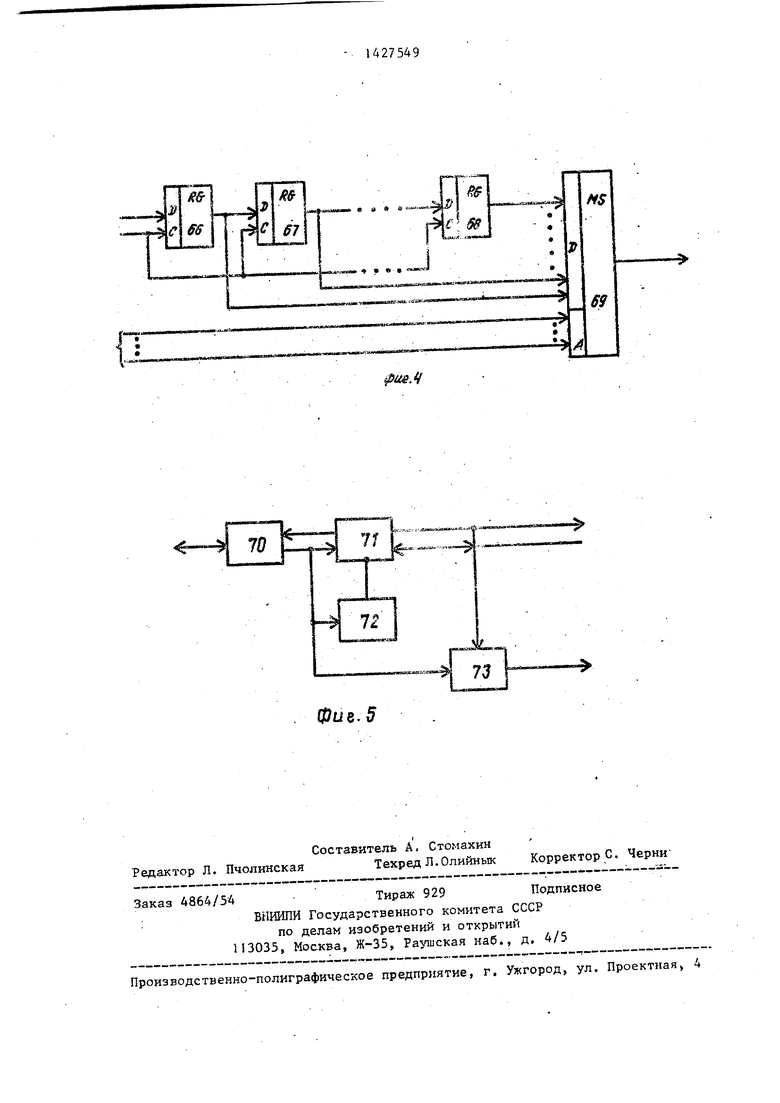

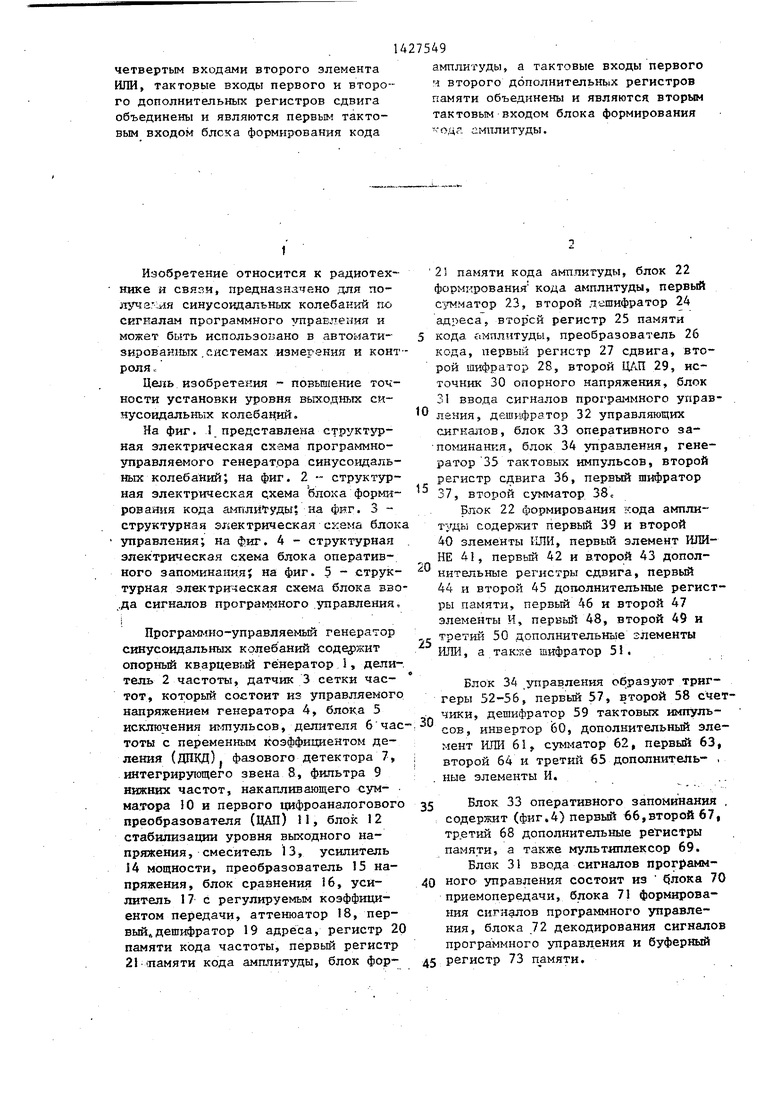

На фиг. I представлена структурная электрическая схема программно- управляемого генерат.ора синусоидальных колебаний; на фиг. 2 - структурная электрическая ахема блока формт - рования кода а далйтуды: на фиг. 3 - структурная электрическая скема блок управления; на фиг. 4 - структурная электрическая схема блока оператив- ного запоминания на фиг. 5 - структурная электри еская схема блока вво ..да сигналов программного .управления.

Программно-управляемый генератор синусоидальных колебаний опорный кварцевый генератор 1, делитель 2 частоты, датчик 3 сетки частот, который состоит из управляемого напряжением генератора 4, блок.а 5 исключения ш-тульсов, делителя 6 час тоты с переменным коэффициентом деления (ДПКД) фазового детектора 7, интегрирующего звена 8, фильтра 9 нижних частот, накапливающего сум- ма.тора 10 и первого цифроаналогового преобразователя (ЦАП) I1, блок 12 стабилизации уровня выходного напряжения , смеситель 13, усилитель 14 мощности, преобразователь 15 напряжения, блок сравнения 16, усилитель 17 с регулируемым коэффициентом передачи, аттенюатор 18, первый дешифратор 19 адреса, регистр 20 памяти кода частоты, первьй регистр 21 Памяти кода амплитуды, блок фор 21 памяти кода амплитуды, блок 22 формирования кода амплитуды, первый сумматор 23, второй дешифратор 24 адреса, втор сй регистр 25 памяти

5 кода амплитуды, преобразователь 26 кода, первый регистр 27 сдвига, второй шифратор 28, второй ЦА.П 29, источник 30 опорного напряжения, блок 31 ввода сигналов программного управ ления, дешифратор 32 управляющих сигналов, блок 33 оперативного за- поминания, блок 34 управления, генератор 35 тактовых импульсов, второй регистр сдвига 36, первый шифратор 37, второй сумматор 38«

Блок 22 формирования кода амплитуды содержит первьй 39 и второй 40 элементы ИЛИ, первый элемент ИЛИ- НЕ 41, первый 42 и второй 43 дополнительные регистры сдвига, первый 44 и второй 45 дополнительные регисры памяти, первый 46 и второй 47 элементы И, первый 48, второй 49 и третий 50 дополнительные элементы ИЛИ, а также шифратор 51.

15

20

25

Блок 34 управления образуют трнг геры 52-56, первый 57, второй 58 счетчики, дешифратор 59 тактовых импульсов, инвертор 60, дополнительный элемент ИЛИ 61 у сумматор 62, первый 63, второй 64 и третий 65 дополнитель- , ные элементы И.

35 Блок 33 оперативного запоминания , содержит (Фиг.4) первый 66,второй 67, третий 68 дополнительные ретистры памяти, а также мультиплексор 69. Блок 31 ввода сигналов программ40 ного управления состоит из лока 70 прнемопередачи, блока 71 формирования сигналов программного управления, блока 72 декодирования сигналов программного управления и буферный

45 регистр 73 п амяти.

Программно-управляемый генератор с.ик:усоздальных колебаний работает след5пощим образом. ; Сигналы программного управления Частотой и амплитудой выходного сиг- Нала последовательно-поступают на Ьход блока 31 ввода, состоящий из тактовых интерфейсных функциональных Элементов Проходя через блок 70 при Ёмопарадачи,, блок ,72 декодирования JJ б,пок 71 сигналы поступают на управ Ляющш : вход деи1ифр ;1тора 32 и на пер- йьй синкронизирзпощий вкод блока 34 управления,, ас вьпсода буферного |фег.истра 73 - на информацион- входы дешифратора 32 к блока. 33 Фперативного запоминания, состояще- fo из последовательно соединенных .(етырехразрядных регистров памяти 165 67 и 68, выходы которых коммутируете я .с помощью мультиплексора 69 н аходы блока 22 формирования и регист iioB 20 и 25 памяти,

; На вход регистра 20 памяти постуliaeT код частоты вьгходного сигнала в Последовательности, определяемой кодом адреса на выходе первого дешиф™

liaTopa 19, а код амплитуды записы веется во второй регистр памяти- 25 согласно коду адреса с выхода второ- л о дешифратора 24. Смена данньк о частоте и амплитуде, производится по - актовым сигналам с выходов блока 34, По :ледовательность команд на слену даннык поступает с выходов дешифратора. 32 на триггеры 52-56 рризнака команды9 а тактовыа сигна лы с генератора 35 через первый счет- Чш 57 и дешифратор 59 поступают на выходы дополнителтзных элементов И 63 и 64. С изменением состояния триггера 55 тактовый сигнал с выхода до r(OHHH i ii.;SbKCTo элвмвнта И 63 посту™ й.ает ка вкод регистра 20 памяти, а с изменением состояния триггера 56 i aктoвый сигнал с вьжода дополнительного элемента И 64 поступает на вход второго регистра 25 памяти.. С изме нением .состояния тркггзра 53 с -вы кода . су:мматора 62 и дополнительного (лемента ИЛИ 6 тактовыа снгнашз поступают на входы блока. 22 формирования,

Иаменекие частоты выходного сигнала иронзводится но двзгм входам дат- Ч1ика 3;. причем с первого выхода ре- rKc-fpa ZO пшчгяти сигнап управления поступает на вкод интегрирующего

Q

5

0

звена 8 через накапливающий сумматор 10 и ЦАП П, а с второго вьгхода регистра 20 памяти сигнал управления поступает на вход ДПКД 6, включенного в петлю фазовой автоподстройки частоты, ко торая состоит из фазового детектора 7, интегрирующего звена 8, фильтра 9, управляемого напряжением генератора 4 и блока 5 При этом датчик 3 выр.абатывает сигнал с частотой, .значение которой лежит несколько выше рабочего диапазо на частот программно-управляемого .генератора синусоидальных колебаний. Этот сигнал поступает на ОДК1 вход смесителя 13, на другой вход которого через усипи- тель .17 подается сигнал кварцованной частоты с выхода опорного КБарцево- го .генератора.1 и на опорный вход фазового детектора-7 через усипиталь 2, На выходе смесителя .13 выделяется сигнал разностной частоты, для которой блок 2, состоящий из. включешшх

5 в кольцо усилителя 14. праобразовате- ля 5, блока 16 сравнения, усилителя 17 и смесителя 13, обеспечивает постоянство амплитуды выходного сигнала,

0 Изменение а.мплнту;з 5 выходного сиг-нала производится одновременно по двум каналам: изменением опорноз о напряжен.шг на выходе второго ЦАЦ.29 и изменением вепичиыы ослабления ат-- тенюатора 18. При этой на информационный вход второго регистра памяти 25 поступает код мантиссы амплитуды, а код поря,п.«а. амплитуды (децимальная точка) устанавливается при подаче сигнала управления с дешифратора 32 через триггер 52, второй регистр 36 сдвига, первый шифратор 37 и второй cyMxiaizop 38 на вход .первого рех истра памяти, изменяю™ щего величину козффипдента ослабления аттенюатора IS

Преобразование кода мантиссы амплитуды заключается з умножении исходного значения на 10, где -ш 65.1,2,3, Умножение .эквивалентно сдвигу на ю десятичных разрядов что обеспечивается путем суммирования кода.адреса, поступающего на входы первого сумматора 23 с второго счетчика 58 блока 34 и кода сдвига а шлитуды с выхода блока 22. Формирование кода сдвига амплитуды с выхода блока 22 производится в параллальных канал.ах., состо.ч5

0

S

0

5

щих из элементов ИЛИ 39 и 40, дополнительных регистров 42 и 43 сдвига и дополнительных регистров 44 и

45памяти, с выходов которых сигналы обоих каналов через элементы И

46и 47 дополнительные элементы ИЛИ 48-50 и шифратор 51 поступают на входы сумматоров 23 и 38. С выхода сумматора 23 через дешифратор 24 производится управление регистром 25 памяти, с вывода которого через прр образователь 26 кода,, регистр 27

.1

сдвига и ЦЛП 29 сигнал управления амплитудой поступает на вход блочка 16 сравнения. Сигналы трех старших разрядов с выходов преобразователя 26 кода поступают.на вход шифратора 28, управляющего работой регистра 27 сдвига и регистра 21 памяти. Тактовый сигна;.; на вход первого регистра пар.зяти 21 с выхода c;i iMaTopa 62 через дополнительный ;:.емент И 65 при- изменении состояния триггера 56 „ -

т2

t:3

«70

Фи,5

4 « е ««cArJ

71

-12

| Программный генератор периодических сигналов и постоянных напряжений а.и.кантера | 1978 |

|

SU790154A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1984-11-26—Подача