(54) УСТРОЙСТВО ИНТЕГРАЛЬНОГО ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Детектор двухчастотных сигналов относительной фазовой модуляции | 1985 |

|

SU1298947A1 |

| Устройство демодуляции сигналов относительной фазовой телеграфии,прошедших канал связи с многолучевостью | 1983 |

|

SU1190535A2 |

| Устройство для регистрации кодовых посылок системы передачи дискретной информации | 1978 |

|

SU739748A1 |

| Устройство автовыбора канала при разнесенном приеме | 1980 |

|

SU886273A1 |

| Устройство тактовой синхронизации регенератора | 1981 |

|

SU1015502A1 |

| Устройство синхронизации двоичных сигналов в приемной аппаратуре системы связи | 1984 |

|

SU1256225A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ по РАБОЧЕМУ СИГНАЛУ | 1967 |

|

SU195495A1 |

| Устройство для синхронизации дискретной информации | 1976 |

|

SU588647A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

Изобретение относится к радиотехнике и может, использоваться для приема (регистрации) дискретных сигналов при реализации технических средств систем связи.

Известно устройство интегрального приема дискретных сигналов, содержащее последовательно соединенные блок выделения фронтов принимаемых посылок первый элемент ИЛИ и блок синхронизации принимаемых посылок, а также интегратор, при этом вход интегратора объединен с входом блока вьщеления фронтов принимаемых посьшок. .

Однако известное устройство недостаточно помехоустойчиво .

Цель изобретения - повышение помехоустойчивости устройства. . Для достижения поставленной цели в устройство введены блок синхронизации по положительным и отрицательным фронтам, второй элемент ИЛИ и два элемента И при этом входы блока синхронизации по поло)штельным и отриНательным фронтам соединены соответственно с выходами блока вьщеления фронтов принимаемых посылок, а выходы блока синхронизации по положительным и отрицательным фронтам через второй элемент ИЛИ подключены к первым входам элементов И, вторые входы которых соединены соответственно с двумя противофазными выходами блока синхронизации принимаемых посылок, а выходы

10 элементов И подключены к соответствующим входам управления интегратора.

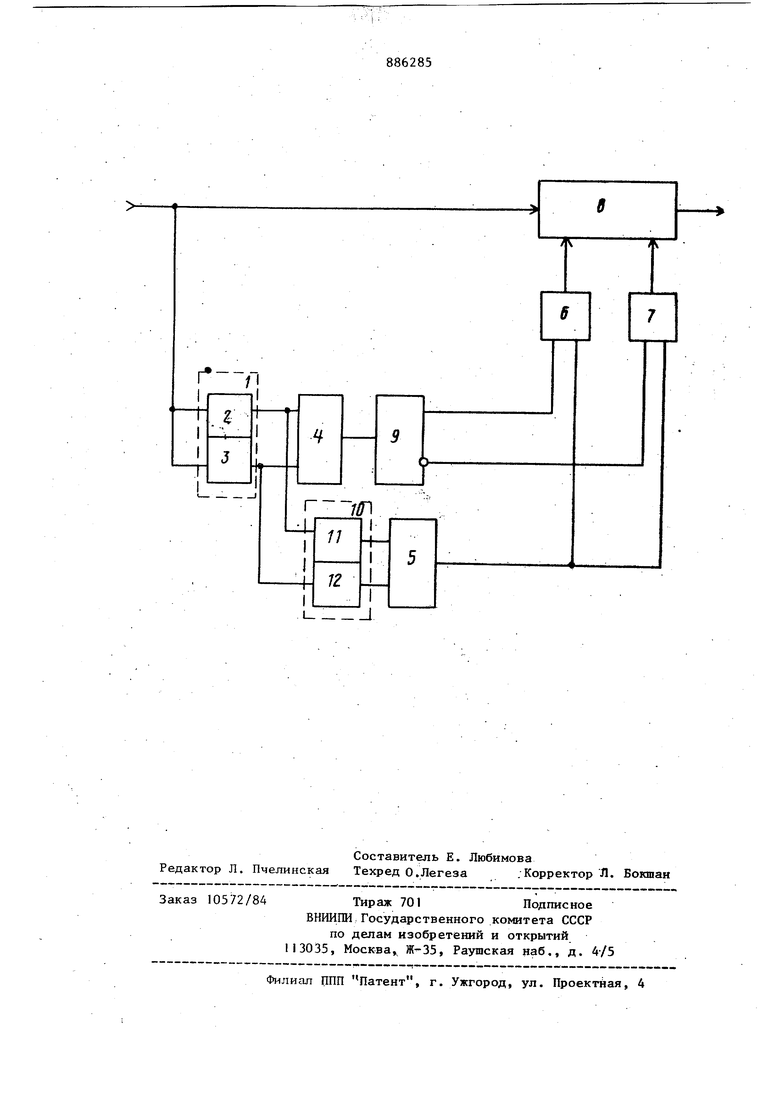

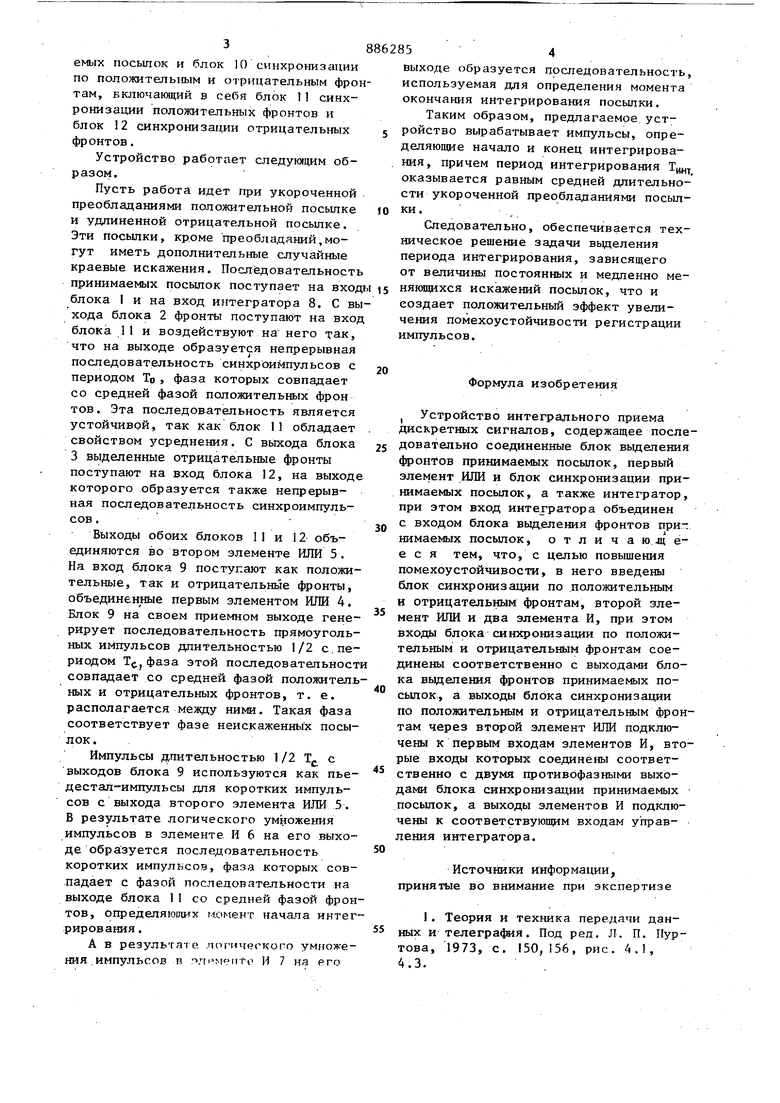

На чертеже представлена структурная электрическая схема предлагаемого устройства.

15

Устройство интегрального приема дискретных сигналов содержит блок 1 выделения фронтЬр принимаемых, посылок, включаюпщй в себя блок 2 выделения фронтов положительных посылок и блок

20 3 вьщеления фронтов. отрицательных посьшок; первьй и второй элементы ИЛИ 4 и 5, два элемента И 6 и 7, интегратор 8, блок 9 синхронизации принимаемых посылок и блок 10 cnHxpOFMsauHH по положительным и отрицательным фронтам, включающий в себя блок 11 синхронизации положительных фронтов и блок 12 синхронизации отрицательных фронтов.

Устройство работггет следующим образом.

Пусть работа идет при укороченной преобладаниями положительной посылке и удлиненной отрицательной посьшке. Эти посьшки, кроме преобладаний,могут иметь дополнительные случайные краевые искажения. Последовательность принимаемых посылок поступает на вход блока I и на вход интегратора 8. С выхода блока 2 фронты поступают на вход блока 1 1 и воздействуют нанего так, что на выходе образуется непрерывная последовательность синхроимпульсов с периодом То, фаза которых совпадает со средней фазой положитель№1х фрон тов. Эта последовательность является устойчивой, так как блок П обладает свойством усреднения. С вьпсода блока 3 выделенные отрицательные фронты поступают на вход блока 12, на выходе которого образуется также непрерывная последовательность синхроимпульсов .

Выходы обоих блоков 11 и 12 объединяются во втором злементе ИЛИ 5. На вход блока 9 поступают как положительные, так и отрицательнь;е фронты, объединен№1е первым элементом ИЛИ 4. Блок 9 на своем приемном выходе генерирует последовательность прямоугольных импульсов длительностью 1/2 с.периодом Т, фаза этой последовательност совпадает со средней фазой положительных и отрицательных фронтов, т. е. располагается между ними. Такая фаза соответствует фазе неискаженных посылок.

Импульсы длительностью 1/2 Т с выходов блока 9 используются как пьедестал-импульсы для коротких импульсов с выхода второго элемента ИЛИ 5. В результате логического умножения импульсов в элементе И 6 на его выходе образуется последовательность коротких импульсов, фаза которых совладает с фазой последовате.пьности на выходе блока 1I со средней фазой фронтов, определяювшх м:омент начала интегрирования .

А в результа-1 Ч лсп-нческого умножения .импульсов 13 Лl teFlto И 7 на его

выходе образуется лоследовательность, используемая для определения момента окончания интегрирования посьтки. Таким образом, предлагаемое устройство вырабатывает импульсы, определяющие начало и конец интегрирова. ния, причем период интегрирования оказывается равным средней длительности укороченной преобладаниями посылки.

Следовательно, обеспечивается техническое решение задачи вьщеления периода интегрирования, зависящего от величины постоянных и медленно ме5 някшщхся искажений посылок, что и создает положительный эффект увеличения помехоустойчивости регистрации импульсов.

Формула изобретения

I Устройство интегрального приема дискретных сигналов, содержащее после5 довательно соединенные блок выделения фронтов принимаемых посыпок, первый элемент ИЛИ и блок синхронизации принимаемых посылок, а также интегратор, при этом вход интетратора объединен с входом блока выд.еления фронтов принимаемых посылок, отличаюлцее с я тем, что, с целью повышения помехоустойчивости, в него введены блок синхронизации по положительным и отрицательным фронтам, второй элемент ИЛИ и два элемента И, при этом входы блока синхронизации по положительным и отрицательным фронтам соединены соответственно с выходами блока вьщеления фронтов принимаемых посылок, а выходы блока синхронизации по положительным и отрицательным фронтам через второй элемент ИЛИ подключены к первым входам элементов И, вторые входы которых соединены соответственно с двумя противофазными выходами блока синхронизации принимаемых посылок, а выходы элементов И подключены к соответствующим входам управления интегратора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-11-30—Публикация

1980-01-04—Подача