(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ОБЪЕКТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для контроля электрического монтажа | 1980 |

|

SU1096657A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Система для контроля электронных устройств | 1988 |

|

SU1667074A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

I

Изобретение относится к области вычислительной техники и может быть использовано для контроля цифровых объектов.

Известнь: устройства для контроля цифровых схем, содержащие регистр адреса, схему сравнения, генератор тактов, элемент И, счетчик, память, формирователи входных сигналов, компаратор, коммутатор, регистр ошибок, буферный регистр и регистр управления ni.

Недостаток этих устройств состоит в больших аппаратурных затратах.

Наиболее близким к предлагаемому по технической сущности является устройство для автоматического контроля Ц11фровых объектов, содержащее блок связи с объектом, состоящий иа узла формирования входных сигналов и дискриминатора выходных сигналов, эталонный блок, блок сравнения, первым и вторым входом соответственно соединенньй через дискриминатор выходньгх сигналов со входом устройства, а через эталонный блок - с выходом устройства, третьим входом - с первым выходом блока блокировки, а выходом - со входом блока синхронизации, выходы которого подключены соответственно к первым входам блока формирования входных сигналов, генератора тестов, блока памяти, блока выбора адреса и счетчика так10тов, выходы которого подклю 1ены соответственно ко вторым входам соединенных двухсторонней связью блока выбора адреса и блока памяти, третий вход которого соединен с выхо15дом блока ввода, а выход соответственно со вторыми входами блока блокировки и генератора тестов, выход которого и второй выход блока блокировки подключены к соответствукнцим входам блока формирования входных сигналов 2.

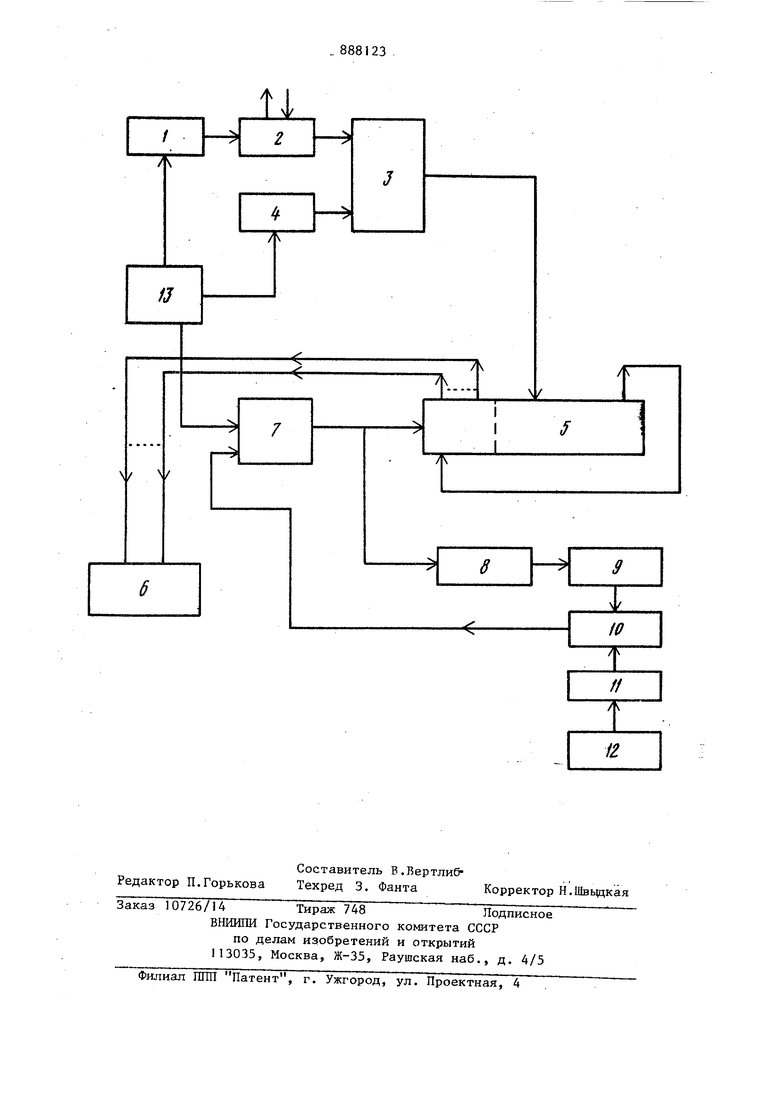

Недостаток этого устройства состоит в больших аппаратурных затратах. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем что в устройство, содержащее счетчик, блок связи с объектом, первые вход и выход которого являются соот ветственно входом и выходом устройства, второй вход соединен через генератор тестов с первым выходом блока синхронизации, а второй выход с первым входом первой схемы сравне ния, вторым входом подключенной к выходу эталонного блока, введены сдвиговый регистр, вторая схема сра нения, делитель частоты, шифратор, блок задания номера десятка и эле мент И, причем первый вход сдвиговог регистра соединен с выходом первой схемы сравнения, группа выходов с группой индикаторных выходов устройства, а второй вход - с выходом элемента И и через делитель частоты со входом счетчика, выход которого подключен к первому входу второй схемы сравнения, вторым входом соединенной через шифратор с выходом блока задания номера десятка, а выходом - с первым входом элемента И, второй вход которого и вход эталонного блока подключены соответ ственно ко второму и третьему выходам блока синхронизации. На чертеже представлена блок-схе ма устройства. Устройство содержит генератор 1 тестов, узел 2 связи с объектом, эт лонный блок 3, первую схему 4 сравнения, сдвиговый регистр 5, блок 6 индикации, элемент И 7, делитель 8 частоты, счетчик 9, вторую схему 10 сравнения, шифратор 11, блок 12 задания номера десятка и блок 13 си ронизации. Генератор 1 тестов предназначен для выработки испытательных воздействий. Узел 2 связи с объектом осуществляет сопряжение устройства кон троля с последующим объектом (состоит из приемников информации и пер датчиков информации). Эталонный бло 3 предназначен для выработки эталонных значений реакции. Первая схе ма 4 сравнения осуществляет сравнение реакции объекта и эталонного зн чения 1)еакции. Сдвиговый регистр 5 предназначен для записи в него N разрядного результата сравнения и последующего сдвига по кольцу этой информации. Блок 6 индикации предназначен для индикации заданной части (например десяти бит из М-разрядного результата сравнения, содержащегося в сдвиговом регистре). Счетчик 9 осуществляет подсчет числа десятков. Блок переключателей, реализованный на наборе тумблеров, предназначен для установки номера десятка N-разрядного результата. Блок I3 предназначен для синхронизации работы блоков устройства и может быть реализован в виде микропрограммного ПЗУ. Устройство работает следующим образом. Генератор 1 по сигналу блока 13 вырабатывает тесты проверки, которые узел 2 подает на проверяемый объект через первый выход узла 2. Реакция объекта на испытательное воздействие поступает через первый вход узла и далее на первый вход первой схемы 4 сравнения. Эталонный блок 3 вырабатывает значения реакций, соответствующие исправному проверенному объекту. Первая схема сравнения осуществляет сравнение эталонного выходного сигнала с реакцией объекта, результат сравнения поступает в сдвиговый регистр 5, замкнутый в кольцо . информации в регист ре осуществляется по синхроимпульсам, поступающим от блока 13 через элемент И 7. Делитель 8 аьщеляет каждый десятый синхросигнал, по которому ведет счет счетчик 9, осуществляя тем самым подсчет числа десятков синхроимпульсов, т.е. числа сдвинутых десятков разрядного результата сравнения. На блоке 12 устанавливается номер десятка Ы-разрядного результата сравнения, который необходимо высветить на блоке 6 индикации. Шифратор 11 шифрирует это значение и вторая схема 10 сравнения сравнивает заданный номер десятка с номером содержащегося в индицируемой части сдвигового регистра 5 десятка результата сравнения. При несовпадении этого номера с заданным из блока 13 на сдвиговый регистр 5 через элемент И 7 продолжают поступать синхросигналы, сдвигая информацию в сдвигающем регистре 5. При совпадении сигнал с выхода схемы 10 сравнения блокирует дальней5шее прохождение синхросигналов на элементен, тем самым прекращается сдвиг информации в сдвигающем ре гистре 5 и в индицируемых разрядах этого регистра оказывается расположе тот десяток разрядов выходного слова, номер которого установлен на блоке 12. Блок 6 индикации высвечивает необходимый десяток разрядок М-разрядного результата сравнения. Таким образом предлагаемое устрой ство имеет значительно меньший объем аппаратуры, причем увеличение разрядности выходных сообщений цифровых :объектов не приводит к увеличению об ема оборудования устройства. Формула изобретения Устройство для контроля цифровых объектов, содержащее счетчик, блок связи с объектом, первые вход и выхо которого являются соответственно входом и выходом устройства, второй вход соединен через генератор тестов с первым выходом блока синхронизации,, а второй выход - с первым вхо дом первой схемы сравнения, вторым входом подключенной к выходу эта3лонного блока, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены сдвиговый регистр, вторая схема сравнения, делитель частоты, шифратор блок задания номера десятка и элемент И, причем первый вход сдвигового регистра соединен с выходом первой схемы сравнения, группа выходов с группой индикаторных выходов устройства, а второй вход - с выходом элемента И и через делитель частоты со входом счетчика, выход которого подключен к первому входу второй схемы сравнения, вторым входом соединенной через шифратор с выходом блока задания номера десятка, а выхо,дом - с первым входом злемента И, второй вход которого и вход эталонного блока подключен соответственно ко второму и третьему выходам блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2687307, кл. G 06 F 11/04, 1978. 2.Авторское свидетельство СССР N5 656063, кл. G 06 F 11/06, 1977 (прототип).

Авторы

Даты

1981-12-07—Публикация

1980-01-10—Подача