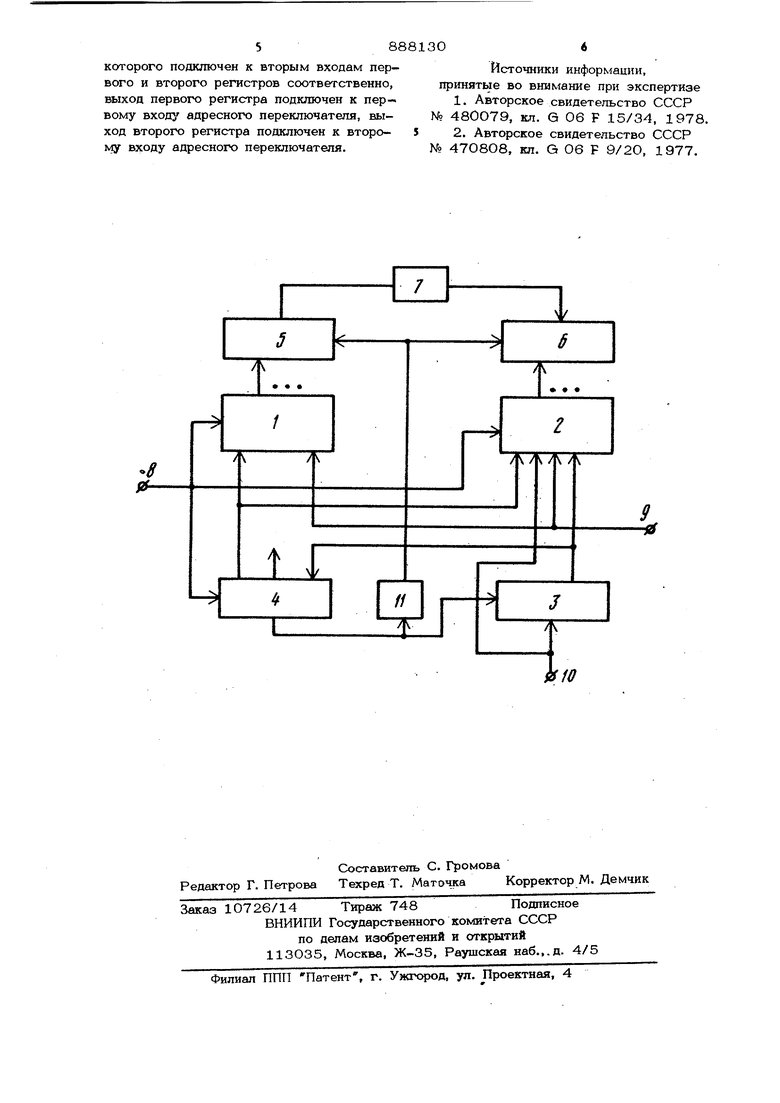

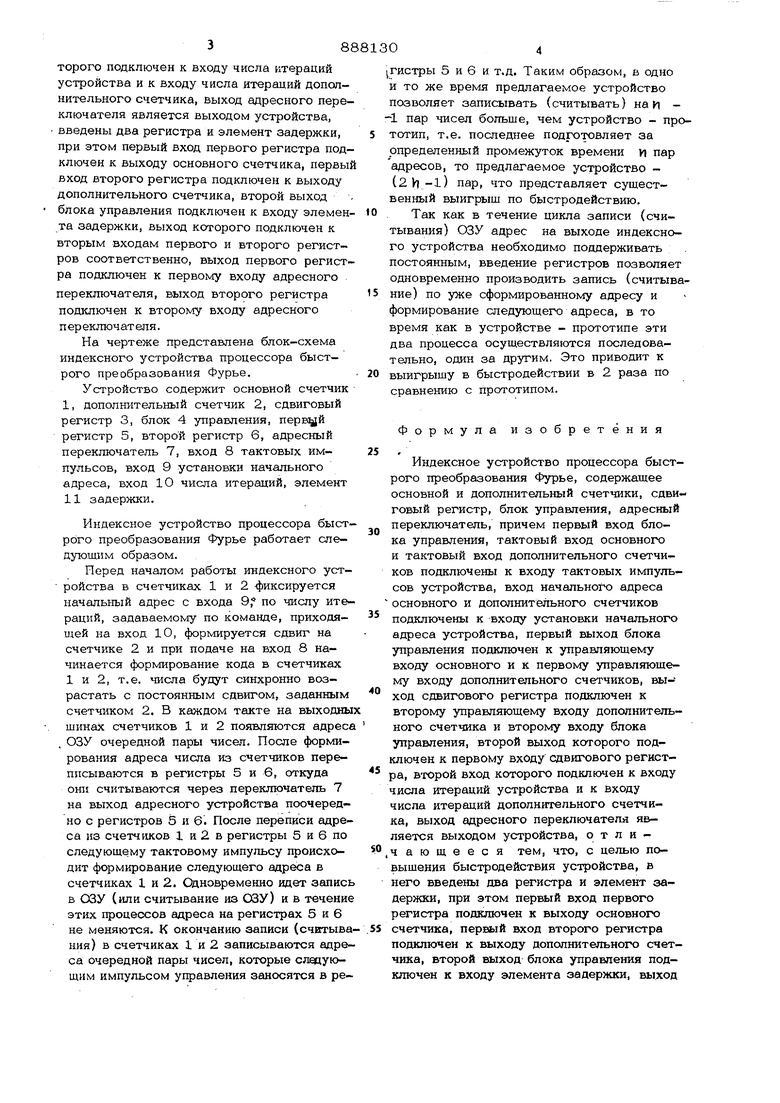

Изобретение относится к вычислитель ной технике и может быть использовано в области цифровой обработки сигналов. Известно устройство, реализующее быстрое преобразование Фурье fl, содержащее блок формирования адреса, вклю чающий счетчик ащэеса, дешифратор адреса и делитель частоты. Недостатком данного устройства является поочередное формирование каждого йореса, что увеличивает общее время пре образования и снижает быстродействие .устройства. Наиболее близким по технической сущности к иаобретенитоявляется устройство 2}, содержащее два счетчика, сдвиговый реврнстр, блок управления, адресный переключатель. Недостатком указанного устройства является невысокое быстродействие, так .как числа установившиеся в каждом такте итерации в счетчиках должшл сохраняться там до конца процесса записи (счнтывания) оперативного запоминающего устройства (ОЗУ). Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее основной и дополнительный счетчики сдвиговый регистр, блок управления, адресный переключатель, причем первый вход блока управления, тактовый юсод основного и тактовый вход дополнительного счетчиков подключены к входу тактовых импульсов устройства, вход начального адреса основного и дополнительного счетчиков подключе ны к входу установки начального адреса устройства, первый выход блока управления подключен к управляющему входу основного и к первому управляющему ;входу дополнительного счетчиков, выход сдвигового регистра подключен к второму управляющему входу дополнительного счетчика и второму ВХОДУ блока управления, второй выход которого подключен к первому входу сдвигового регистра, второй вход которого подключен к входу числа итераций устройства и к входу числа итераций дополнительного счетчика, выход адресного переключателя является выходом устройства, введены два регистра и элемент задержки, при этом первый вход первого регистра подключен к выходу основного счетчика, первы вход второго регистра подключен к выходу дополнительного счетчика, второй выход блока управления подключен к входу элемен та задержки, выход которого подключен к вторым входам первого и второго регистров соответственно, выход первого регист ра подключен к первому входу адресного переключателя, выход второго регистра подключен к второму входу адресного переключателя. На чертеже представлена блок-схема индексного устройства процессора быстрого преобразования Фурье. Устройство содержит основной счетчик 1, дополнительный счетчик 2, сдвиговый регистр 3, блок 4 управления, первщй регистр 5, второй регистр 6, адресный переключатель 7, вход 8 тактовых импульсов, вход 9 установки начального адреса, вход 10 числа итераций, элемент 11 задержки. Индексное устройство процессора быст рого преобразования Фурье работает следующим образом. Перед началом работы индексного уст- ройства в счетчиках 1 и 2 фиксируется начальный адрес с входа 9, по числу ите раций, задаваемому по команде, приходящей на вход 10, формируется сдвиг на счетчике 2 и при подаче на вход 8 начинается формирование кода в счетчиках 1 и 2, т.е. числа будут синхронно возрастать с постоянным сдвигом, заданным счетчиком 2. В каждом такте на выходны шинах счетчиков 1 и 2 появляются адрес ОЗУ очередной пары чисел. После формирования адреса числа из счетчиков переписываются в регистры 5 и 6, откуда они считываются через переключатель 7 на выход адресного устройства поочередно с регистров 5 и 6. После переписи адреса из счетчиков 1 и 2 в регистры 5 и 6 по следующему тактовому импульсу происходит формирование следующего адреса в счетчиках 1 и 2. Одновременно вдет запис в ОЗУ (или считывание из ОЗУ) и в течени этих процессов адреса на регистрах 5 и 6 не меняются. К окончанию записи (считыва ния) в счетчиках 1 и 2 записываются адре са очередной пары чисел, которые следующим импульсом управления заносятся в реГистры 5 и 6 и т.д. Таким образом, в одно и то же время предлагаемое устройство позволяет записывать (считывать) на и - 1 пар чисел больше, чем устройство - прототип, т.е. последнее подготовляет за определенный промежуток времени и пар адресов, то предлагаемое устройство (2V) -1) пар, что представляет существенный выигрыш по быстродействию. Так как в течение цикла записи (считывания) ОЗУ адрес на выходе индексного устройства необходимо поддерживать постоянным, введение регистров позволяет одновременно производить запись (считывание) по уже сформированному адресу и формирование следующего адреса, в то время как в устройстве - прототипе эти два процесса осуществляются последовательно, один за другим. Это приводит к выигрышу в быстродействии в 2 раза по сравнению с прототипом. Формула изобретения Индексное устройство процессора быстрого преобразования Фурье, содержащее основной и дополнительный счетчики, сдвиговый регистр, блок управления, адресный переключатель, причем первый вход блока управления, тактовый вход основного и тактовый вход дополнительного счетчиков подключены к входу тактовых импульсов устройства, вход начального адреса основного и дополнительного счетчиков подключены к входу установки начального адреса устройства, первый выход блока управления подключен к управляющему входу основного и к первому управляющему входу дополнительного счетчиков, вы-ход сдвигового регистра подключен к второму управляющему входу дополнительногю счетчика и второму входу блока управления, второй выход которого подключен к первому входу сдвигового регистра, второй вход которого подклЕочен к входу числа итераций устройства и к входу числа итераций дополнительного счетчика, выход адресного переключателя является выходом устройства, о т л и чающееся тем, что, с целью повышения быстродействия устройства, в него введены два регистра и элемент задержки, при этом первый вход первого регистра подключен к выходу основного счетчика, первый вход второго регистра подключен к выходу дополнительного счетчика, второй выход блока управления подключен к входу элемента задержки, выход которого подключен к вторым входам первого и второго регистров соответственно, выход первого регистра подключен к первому вход; адресного переключателя, выход второго регистра подключен к второму входу адресного переключателя. 88 130 Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 480О7Э, кл. G 06 F 15/34, 1978. S 2. Авторское свидетельство СССР № 47О808, кл. Q Об F 9/20, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Индексное устройство процессора быстрого преобразования фурье | 1973 |

|

SU470808A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Анализатор спектра | 1982 |

|

SU1062716A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

/1

/

8

1

/

/V /

/

f

9 -а

Авторы

Даты

1981-12-07—Публикация

1980-01-09—Подача