(5) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ АНАЛОГА В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь "аналог-код | 1980 |

|

SU930649A1 |

| Преобразователь аналог-код | 1978 |

|

SU766001A1 |

| Устройство преобразования "аналог-код | 1979 |

|

SU834893A1 |

| Устройство для идентификации характеристик четырехполюсников | 1983 |

|

SU1188676A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| Устройство для определения статистических характеристик непрерывных случайных величин | 1981 |

|

SU1012270A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| Устройство для программного управления | 1987 |

|

SU1432461A1 |

| Устройство для автоматического регулирования формы полосы | 1984 |

|

SU1235577A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

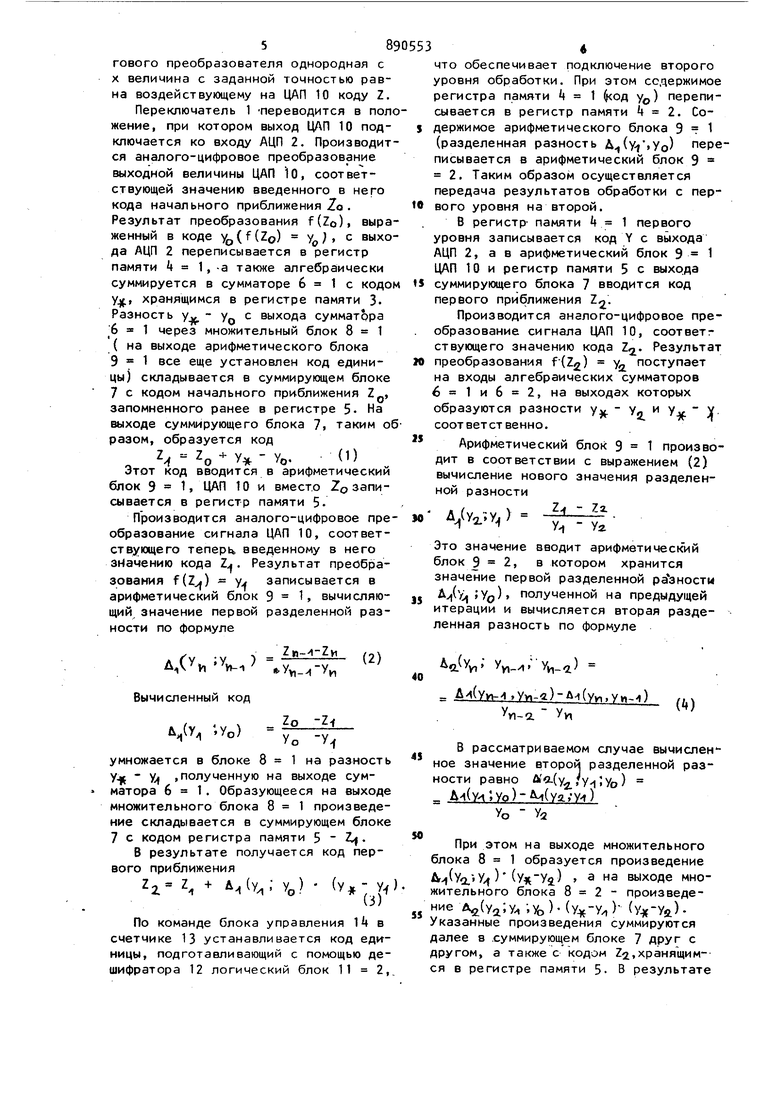

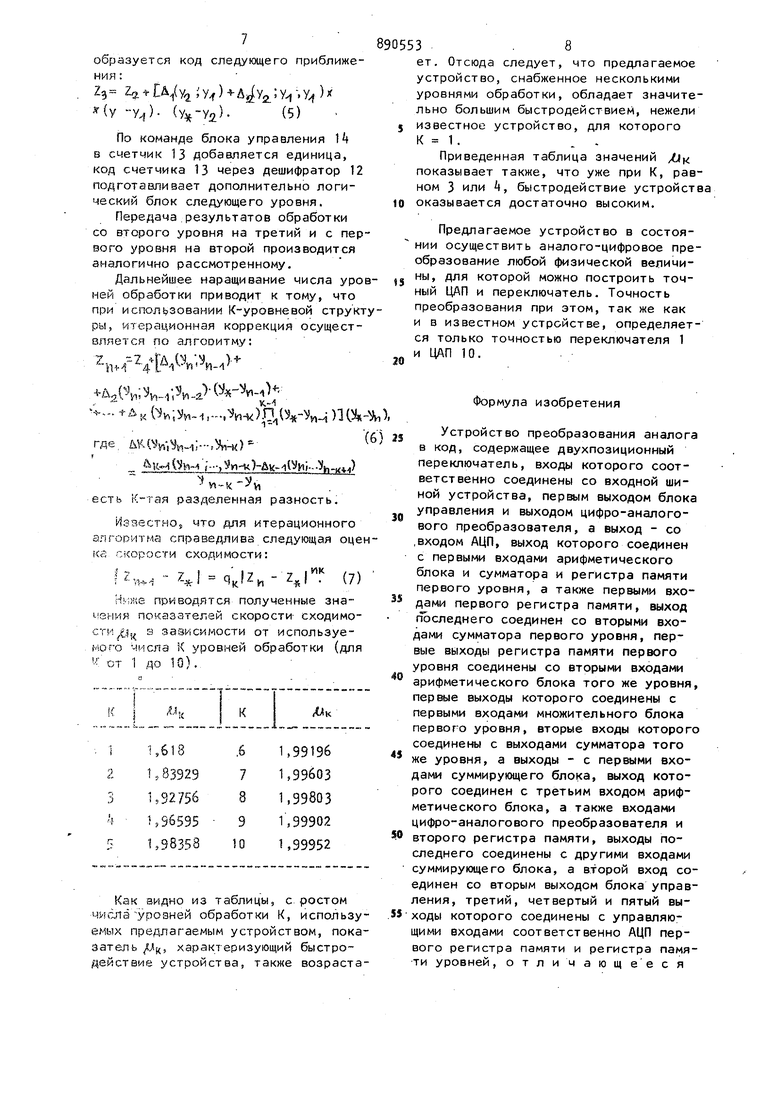

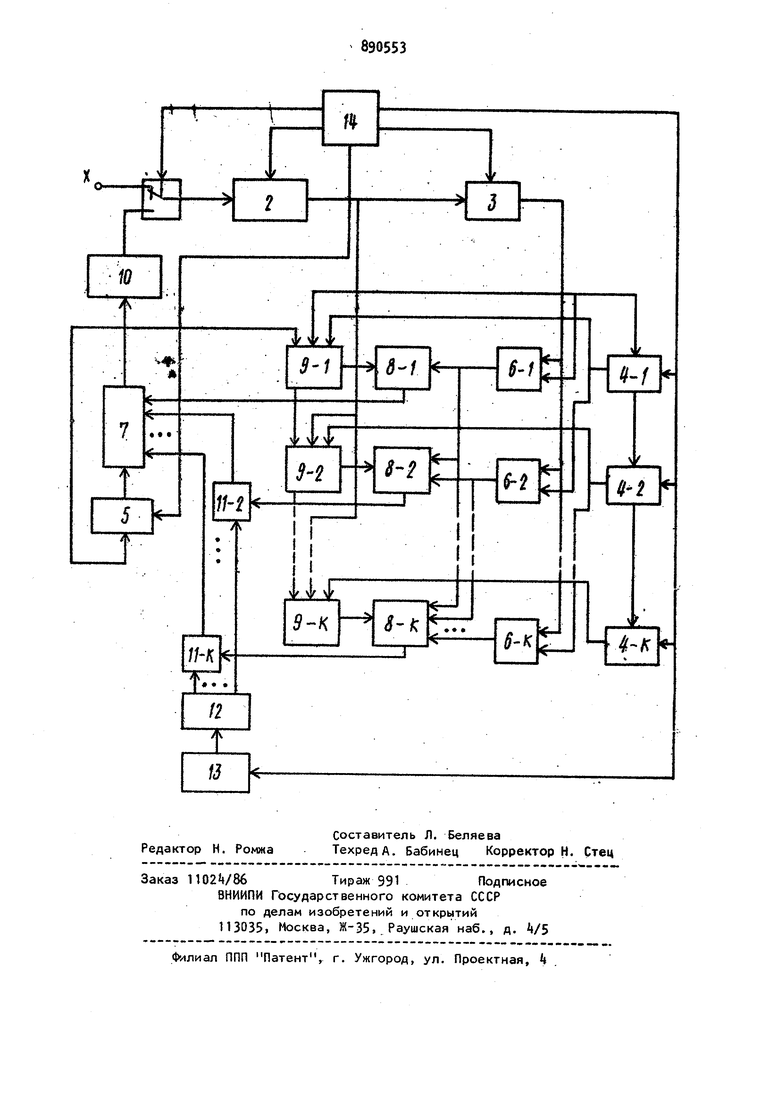

Изобретение относится к информационно-измерительной технике, а именно к разделу быстродействующих и точных измерительных преобразователей. Известен преобразователь анало - код, содержащий двухпозиционный переключатель, подключающий входную шину устройства и выход цифро-аналогового преобразователя (ЦАП) ко входу аналого-цифрового преобразователя (АЦП), соединенного непосредственно и через первый регистр памяти с соответствующими входами первого сумматора, соеди ненного с первыми входами делительного и множительного блоков, причем другой вход последнего соединен с выходом делительного блока, а выход с входом второго сумматора, другой вход которого через второй регистр памяти соединен с его же выходом, который также соединен со входом ЦАП. Выход второго регистра памяти непосредственно и через третий регистр памяти соединен с соответствующими входами третьего сумматора, выход которого подключен ко второму входу делительного устройства. Синхронизация работы переключателя АЦП и всех регистров памяти осуществляется блоком управления f1. Оценка скорости сходимости итерационного процесса, реализуемого в известном устройстве, имеет вид: ,.|2„ 2, где Zj - цифровой эквивалент истинного (без погрешностей) значения входной величины; Z, , f. коды, полученные в результате проведения п и п+1 итераций соответственно;( Z - 2 I - абсолютная погрешность определения . на каждой итерации. Данное выражение описывает скорость убывания абсолютной погрешности Zn - i / и характеризует быстродействие соответствующего устройства. При больших погрешностях нелинейности быстродействие устройства оказывается недостаточно высоким. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что в устройство преобразования аналога в код, содержащее двухпозиционный переключатель, входы которого соответственно соединены со входной шиной устройства, первым выходом бло ка управления и выходом ЦАП, а выход со входом АЦП, выход которого соединен с первыми входами арифметическог блока и сумматора и регистра памяти первого уровня, а также первыми входами первого регистра памяти, выход последнего соединен со вторыми входа ми сумматора первого уровня, первые выходы регистра памяти первого уровня соединены со вторыми входами ариф метического блока того же уровня, пе выходы которого соединены с первыми входами множительного блока пер вого уровня, вторые входы которого соединены с выходами сумматора того же уровня, а выходы - с первыми входами суммирующего блока, выход которого соединен с третьим входом арифметического блока, а также входами ЦАП и второго регистра памяти, выход последнего соединены с другими входа ми суммирующего блока, а второй вход соединен со вторым выходом блока управления, третий, четвертый и пятый выходы которого соединены с управляю щими входами соответственно АЦП первого регистра памяти и регистра памя ти уровней, введены К-1 арифметических блоков, множительных блоков сум маторов, регистров памяти и логических блоков дополнительных уровней, а также дешифратор и счетчик, причем первые входы арифметических блоков каждого из дополнительных уровней со единены с выходом АЦП, вторые входы соединены с выходом регистра памяти своего уровня, третьи входы соединен с первыми выходами арифметических бл ков предыдущего уровня, а вторые выходы - с первыми входами множительны блоков своего уровня, другие входы которых соединены с выходами суммато ров своего и всех предыдущих уровней первые входы дополнительных сумматоров соединены с выходом первого регистра памяти, а вторые входы - с выходами регистровпамяти предыдущего уровня соответственно, вход регистра памяти каждого дополнительного уровня соединен с выходом регистра предыдущего уровня, выходы дополнительных множительных блоков через логические блоки соединены с соответствующими входами суммирующего блока, а управляющие входы логических блоков соединены с выходами дешифратора, вход которого соединен с выходом счетчика, вход которого вместе с управляющими входами дополнительных регистров памяти объединен с управляющим входом регистра памяти первого уровня. На чертеже представлена структурная схема устройства преобразования аналога в код. Схема содержит двухпозиционный переключатель -1 , АЦП 2, регистры памяти 3, 1. К (где К - количество уровней обработки) и 5 сумматоры ,6 2, ...,6 к, суммирующий блок 7. множительные блоки 8 1, , ,,., 8 К, арифметические блоки , ..., 9 К, ЦАП 10, логические блоки 11 1, 11 2, ..., 11 К, дешифратор 12, счетчик 13 и блок управления 1. Устройство работает следующим образом. В исходном состоянии АЦП 2 регистры памяти 3 5 установлены в нуль, переключатель 1 - в положение, при котором преобразуемая величина х подводится ко входу АЦП 2, а на выходе арифметического блока 9 1 установлен код единицы. С помощью АЦП 2 производится аналого-цифровое преобразование входной величины X. Результат преобразования f(x), выраженный в определенном коде у , вводится в регистр памяти 3- Значение кода YV , отличающееся от истинного цифрового эквивалента Z измеряемого параметра х на величину погрешности АЦП 2, принимается в качестве кода начального приближения ZO(ZQ . Поэтому код ZQ с выхода АЦП 2 далее через сумматор , множительный блок 8 1 и суммирующий блок 7 переписывается в регистр памяти 5 арифметический блок 9 1 и ЦАП 10. Передаточная характеристика последнего выбрана такой, что образующаяся на его выходе в результате цифро-анало58гового преобразователя однородная с X величина с заданной точностью равна воздействующему на ЦАП 10 коду Z. Переключатель 1 -переводится в пол жение, при котором выход ЦЛП 10 подключается ко входу АЦП 2. Производит ся аналого-цифровое преобразование выходной величины ЦАП 10, соответствующей значению введенного в него кода начального приближения Zo. Результат преобразования f(Zo), выра женный в коде yjj(f(Zo) Xjb с выхо да АЦП 2 переписывается в регистр памяти k 1, -а также алгебраически суммируется в сумматоре 6 1 с кодо у, хранящимся в регистре памяти 3Разность у - УО с выхода сумматора 6 1 через множительный блок ( на выходе арифметического блока все еще установлен код единицы) складывается в суммирукяцем блоке 7с кодом начального приближения Z, запомненного ранее в регистре 5- На выходе суммирующего блока 7, таким о разом, образуется код Z -- Zo - У:,, - УО.(1)„ Этот код вводится в арифметический блок , ЦАП 10 и вместо ZQ записывается в регистр памяти 5. Производится аналого-цифровое пре образование сигнала ЦАП 10, соответствующего теперь, введенному в него значению кода Zj. Результат преобразования f(Z) у записывается в арифметический блок , вычисляющий значение первой разделенной разности по формуле Д,(Уц Vi .Уу,,-у., Вычисленный код Zo -21 Л,(У -УС) УО -y-f умножается в блоке 8 1 на разность У У , полученную на выходе сумматора . Образующееся на выходе множительного блока 8 1 произведение складывается в суммирующем блоке 7 с кодом регистра памяти 5 - В результате получается код первого приближения Z2. z + А( УО) ;j.r По команде блока управления 1 в счетчике 13 устанавливается код единицы, подготавливающий с помощью дешифратора 12 логический блок 11 2, что обеспечивает подключение второго уровня обработки. При этом содержимое регистра памяти k 1 (код у) переписывается в регистр памяти + 2. Содержимое арифметического блока 9 1 (разделенная разность Л(у-|,Уо) переписывается в арифметический блок 9 2. Таким образом осуществляется передача результатов обработки с первого уровня на второй. В регистр памяти 1 первого уровня записывается код Y с выхода АЦП 2, а в арифметический блок 9 t ЦАП 10 и регистр памяти 5 с выхода суммирующего блока 7 вводится код первого приближения 2. Производится аналого-цифровое преобразование сигнала ЦАП 10, соответг ствующего значению кода 2. Результат преобразования {Zg) Уд поступает на входы алгебраических сумматоров 6 - 1 и 6 2, на выходах которых образуются разности У УО и у„ - у, соответственно. Арифметический блок 9 1 производит в соответствии с выражением (2) вычисление нового значения разделенной разности Л (v v ) Д,У2. - значение вводит арифметический блок , в котором хранится значение первой разделенной разности полученной на предыдущей итерации и вычисляется вторая разделенная разность по формуле Уу1 Уу,/|.Уи-а) А( ,Уу,-й)-Д-1(уу..уи-) Уи-С2. УИ В рассматриваемом случае вычислен ное значение второй разделенной разности равно ЛаСу., ,) ()-&(уа,У.1) УО - У2 При этом на выходе множительного блока 8 1 образуется произведение Л 1 УаУ-1 .) , а на выходе множительного блока произведе ХэЬ ( Указанные произведения суммируются далее в .суммирующем блоке 7 друг с другом, а также с кодом Z-j,хранящимся в регистре памяти 5- В результате образуется код следующего приближе ния: Zg Zg.(y iy)-f д, )х (у -у)- (у -УгЬ(5) По команде блока управления ft в счетчик 13 добавляется единица, код счетчика 13 через дешифратор 1 подготавливает дополнительно логический блок следующего уровня. Передача результатов обработки со второго уровня на третий и с пе вого уровня на второй производится аналогично рассмотренному. Дальнейшее наращивание числа уро ней обработки приводит к тому, что при испол,зовании К-уровневой струк ры, итера14ионная коррекция осущест вляется по аягооитму: . . .-/l,(Л;v1; v1-:г v v1-.):- - (%;51п-1,-.,нч) ncv где, /iVUVvoViI- i-K) f ife4J,Vti- sj;i:-,M-)-:6K-l(Hj--- -j ;HJ есть К-тая разделенная разность. Иззестно, что для итерационного алгоритма справедлива следующая оц ка скорости сходимости: ... - q,Z - Нмже приводятся полученные значения показателей скорости- сходимо S зазисимости от используе(vioro числа К уровней обработки (дл У от 1 до 10), 1,99196 1,618 1,99603 1,83929 1,99803 1,92756 Ь9б595 1,99902 1,98358 1,99952 Как видно из таблицы, с. ростом числа уроэней обработки К, использ емых предлагаемым устройством, пок затель /J(5 характеризующий быстродействие устройства, также возраст 3.8 ет. Отсюда следует, что предлагаемое устройство, снабженное несколькими уровнями обработки, обладает значительно большим быстродействием, нежели известное устройство, для которого К 1.. . Приведенная таблица значений показывает также, что уже при К, равном 3 или k, быстродействие устройства оказывается достаточно высоким. Предлагаемое устройство в состоянии осуществить аналого-цифровое преобразование любой физической величи которой можно построить и переключатель. Точность преобразования при этом, так же как ив известном устройстве, определяется только точностью переключателя 1 и ЦАП 10. Формула изобретения Устройство преобразования аналога в код, содержащее двухпозиционный переключатель, входы которого соответственно соединены со входной шиной устройства, nepKjiM выходом блока управления и выходом цифро-аналогового преобразователя, а выход - со .входом АЦП, выход которого соединен с первыми входами арифметического блока и сумматора и регистра памяти первого уровня, а также первыми входами первого регистра памяти, выход последнего соединен со вторыми входами сумматора первого уровня, первые выходы регистра памяти пер юге уровня соединены со вторыми входами арифметического блока того же уровня, первые выходы которого соединены с первыми входами множительного блока первого уровня, вторые входы которого соединены с выходами сумматора того же уровня, а выходы - с первыми входами суммирующего блока, выход которого соединен с третьим входом арифметического блока, а также входами цифро-аналогового преобразователя и второго регистра памяти, выходы последнего соединены с другими входами суммирующего блока, а второй вход соединен со вторым выходом блока управления, третий, четвертый и пятый выХОДЫ которого соединены с управляющими входами соответственно АЦП первого регистра памяти и регистра памяти уровней, отличающееся

тем, что, с целью повышения быстродействия, введены К - 1 арифметиче-/ ских блоков, множительных блоков, сумматоров, регистров памяти и логических блоков дополнительных уровней, а также дешифратор и счетчик, причем первые входы арифметических блоков каждого из дополнительных уровней соединены с выходом АЦП, вторые входы соединены с выходом регистра памяти своего уровня, третьи входы соединены с первыми выходами арифметических блоков предыдущего уровня, а вторые выходы - с первыми входами множительных блоков своего уровня, другие входы которых соединены с выходами сумматоров своего и всех предыдущих уровней, первые входы дополнительных сумматоров соединены с выходом первого регистра памяти, а вторые входы - с выходами регистров памяти

предыдущего уровня соответственно, вход регистра памяти каждого дополни тельного уровня соединен с выходом регистра-предыдущего уровня, выходы дополнительных множительных блоков через логические блоки соединены с соответствующими входами суммирующего блока, а управляющие входы логических блоков соединены с выходами дешифратора, вход которого соединен с выходом счетчика, вход которого вместе с управляющими входами дополнительных регистров памяти объединен с управляющим входом регистра памяти первого УРОВНЯ.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

по заявке ГГ 2680010/21, кл. Н 03 К 13/02, 01.11.78.

Авторы

Даты

1981-12-15—Публикация

1980-04-07—Подача