(54) ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь аналог-код | 1978 |

|

SU766001A1 |

| Устройство преобразования аналога в код | 1980 |

|

SU890553A1 |

| Устройство преобразования "аналог-код | 1979 |

|

SU834893A1 |

| Преобразователь аналоговых величин в цифровой код | 1978 |

|

SU752789A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1979 |

|

SU1840108A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Гибридный функциональный преобразователь | 1980 |

|

SU879610A1 |

| Устройство для измерения электрических параметров в цепях переменного тока | 1987 |

|

SU1493956A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

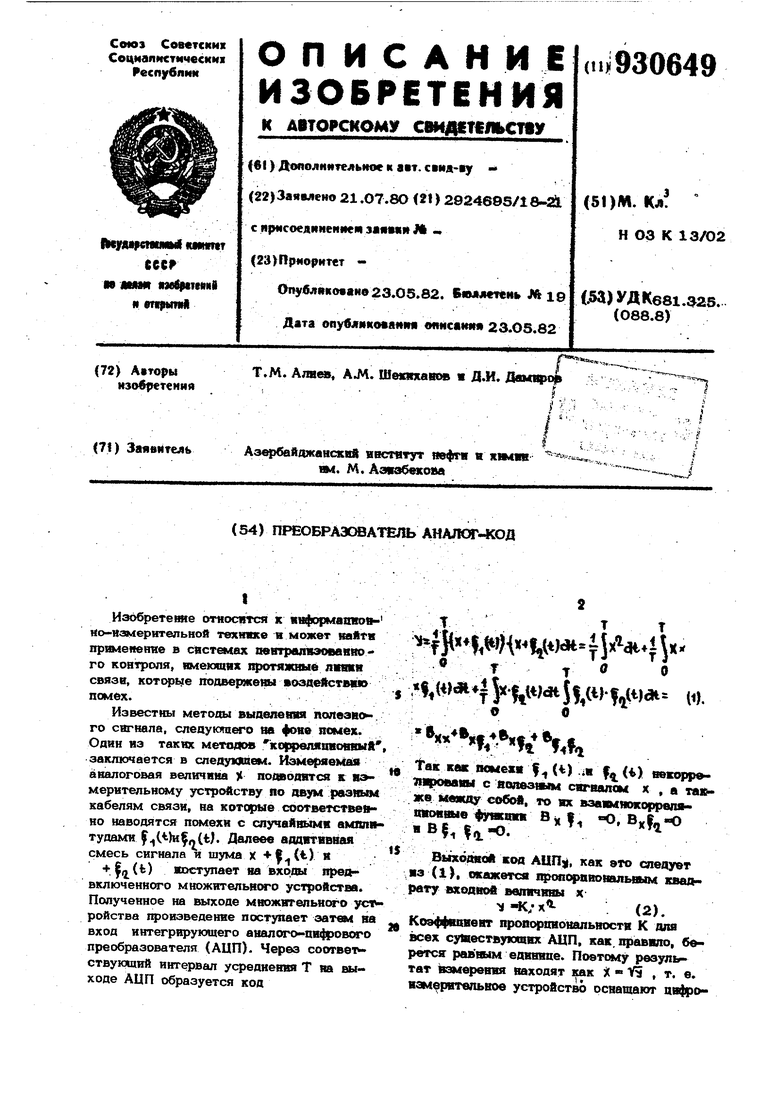

I .:. Изобретете относятся к кнфqpмamювНо-иамернтельной техмшсе в может miftTv прямекение в системах певтралвэовавяого контроля, имеющих протяжные лтшн связи, которые поовержеиы BoaaeftcTBino помех. Известны метопы выпелеяю полеаяо-. го свгнала, слеауютего на фоне помех. Один из такнх методов ко|)|)епяаяояяый заключается в следумшем. Иэме))яеМаЯ ашшоговая величина % поовооятся к я мерительнюлу устройству по двум раэяым кабелям связи, на которые соответствевно наводятся помехи с спучайяымя амплитудами ( Zkuieee ашятявная смесь сигнала и шума х | (t) я ( fij (Ь) ах ступает на входы препвключенного множительн1х о устройства. Полученное на выходе множительного устройства 1фонзведение поступает затш яа вход ннтегрирующего аналого-цифрового преобразователя (АЦП). Через соответ ствукжяий интервал усреднения Т на выходе АЦП образуется код (i)fjx в тt о f,(i.Ui,ai (1). во tae ка« помежя f (t) л f (i) яекрр. с аопезвым сягяалом ж , а тлкже. между собсА, то ях взатнокоррела- ИТ|Г- - .i-O BbjfxofmoA Еод AUn, как это следует яз (1), окажется щ опс 11ио11альшвым ква рагу ВХОДШИ1 ввлячяяы х «-К;х« (2). Коэффявяеят пропорцяоыальяостя К шш всех суАествуюшях АЦП, как, правшю, берется равяым единице. Поетому результат взмереяяя находят 1шк Х - V5 , т. е. яамерятвпьвое устройство оснащают цвфровым блоком извлечения квадратного корня

Итак, известный преобразователь содержит последовательно включенные множительный блок, интегрирующий АЦП и блок извлечения квадратного корня til

Недостаткгод этого устройства является то обстоятельство, что погрешности всех упомянутых блоков оказывают непосредственное влнянпае на точность преобразоваВИЯ. Другой недостаток устройства состоит в необходимости извлечения квадратного корня, процедура которого, как известно, является достаточно трудоемкой и длительной, а результат приближенным.

Известно устройство содержащее переключатель, входы -которого соединены с входной шшюй устройства и выход см ЦАП а выход - с входом AUfI, выход которого непрсредственно и через регистр памяти соединен с входами первого сумматора, выход которого соединен с входами множитеяшого и делительного блоков. Другой вход носледнего соединен с выхо дом второго сумматора, а выход - с другнм входом множительного блока, выход которого соединен с входом третьего сумматора, выход которого соединен с входами ЦАП и регистра памяти, которого соединен с другим третьего сумматора, входами второго сумматоре та. третьего региртра , выход последнего соединен с другим входе второго сумматора, а выходы блока ynpas ленвй соединены с управляющими входами переключателя, АЦП, дедительиого блока и трех регистров памяти.

Скорость сходимости итераций, то есть быстродействие известного устройства, оценшжется следующим офазом.

}1п- 1-Яг-|1п-1-2.)

(3)

- цифровой эквивалент

де ного (без погрешностей) значения входной величины у ;

пн

разность, характеризующая величину абсолютной погрешности юмерения на каждой итерации С21.55

Таким образом, с одной стороны имеетя преобразователь, обеспечивающий xi ощее подавление помех случайной приро- .

ды, что является особо ценным качеством но обладающий низким быстродействием и точностью, а с другой - измерительное устройство способное эффективно корректировать систематические погрешности ана-г лого-цифрового преобразователя.

Однако при квадратичной характеристике (2) применение известной структуры, реализуюлей итерационный метод измерения, не обеспечивает высокого быстродействия.

Кроме того, оно не обеспечивает коррекцию влияния помех случайной природы.

Цель изобретения - повышение быстродействия и точности преобразования.

Поставленная цель достигается тем, что в первый преобразователь аналог-код содержащий переключатель, первый вход которого соединен с первой входной шиной, а второй - с выходом цифро-аналогового преобразователя, вход которого соединен с выходами первого сумматора, и вхсеами первого регистра памяти, выходы которого соединены с первыми входами первого сумматора, аналоге-ыи чэоъой преобразователь, выходы которого соедннеш 1 с первыми входами второго сумматора и второго регистра памяти, выхошя последнего соединены с вторыми вхошми BTqporo сумматора выходы которого соединены с первыми входами блока деления, а с первого по четвертый кыховза управления соединены с упра&ЯЯК1ШШ14И входами первого переключателя, аналтнх -ав) преобразователя и регистров памяти, {юедекы второй переключатель, блок вг исления производной и мвожйтельйый блок, входы которого соединены с ш 1яодами переялючателей, а - с «коа(ял аналого-цифрового преофазователя, при этом входы блока ш 1числевия вроизводнс соединены с выходами первого регистра памяти, а выходы - с входами блежа деления, выхош 1 которого соединены с вторыми вхо{шмв нового сумматора, причем первый вход второго переключателя подклк чен к второй входной шине, второй вход к выходу цифро-аналогового преобразовав теля, а упраелякяпий вход - к первому выходу блока управления.

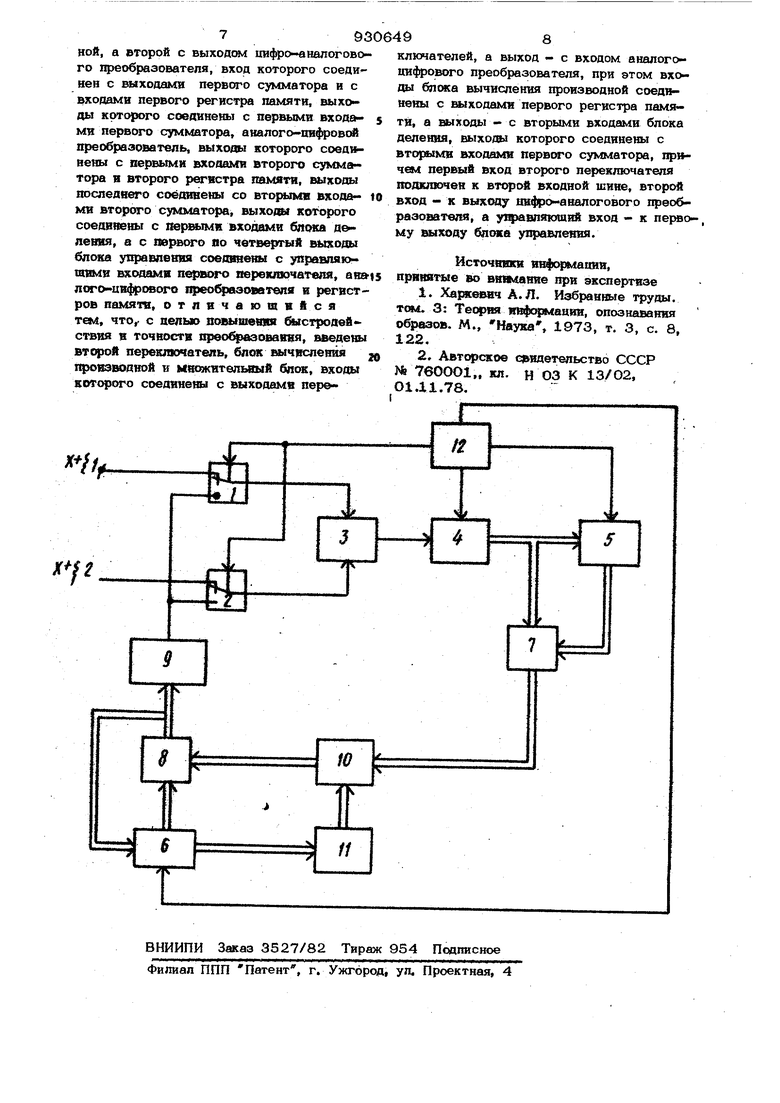

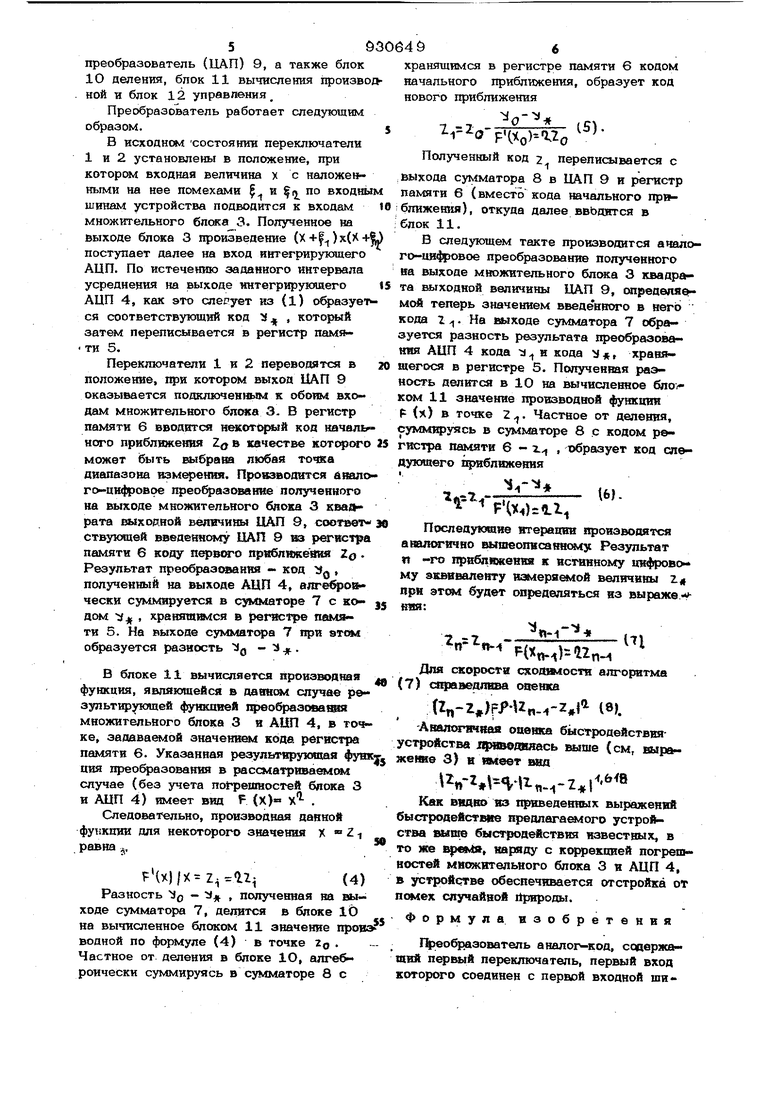

На чертеже представлена блок-схема преобразователя аналог-код, содержащего переключатели 1 и 2, множительный блок 3, интегрирующий (аналого-цифровой преобразователь (АЦП) 4, регистры памяти 5 и 6, сумматоры 7 и 8, ши| о-аналоговый преобразователь (ЦАП) 9, а также блок 10 деления, блок 11 вычисления произво ной и блок 12 управления Преобразователь работает следующим образом. В исходное СОСТОЯНИИ переключатели 1 и 2 установлены в положение, при котором входная величина х с наложенными на нее помехами и fij по входны шинам устройства подводится к входам множительного 6п(жа 3, Полученное на выходе блока 3 произведение (X+f)x()t+ поступает далее на вход янтет рирующего АЦП. По истечению заданного интервала усреднения на выходе кнтегрщзукяяего АЦП 4, как это спесует из (1) образует ся соответствующий код : , который затем переписывается в регистр памяти 5. Переключатели 1 и 2 переводятся в положение, при котором выход ЦАП 9 оказывается подключенш 1м к обошд входам множительного блсжа 3. В регистр памяти 6 вводито некото яый код началь нрго приближетш ZQ в качестве которого может быть Еялбрааа любая точяа диапазона . Производится двало го-цифровое прео азовав« получевного на выходе множительного блока 3 кваарата выходвой величины ШШ 9, соответ ствуюшей введенному ЦАП 9 вз регисфа памяти 6 коду првблкжевия Zo Результат преобраз1жаннв - код Уд , полученный на выходе АЦП 4, алгефо чески суммируется в сумматоре 7 с кодом -г/ , хранящимся в peracipe памяти 5. На выходе сумматора 7 при этом образуется разность Q - . в блоке 11 вычисляется производная функция, являющейся в случае ре зупьтируюшей функцией 1феобразовагак множительного блока 3 и ЛИП 4, в тоф ке, задаваемой значением кода регистра памяти 6. Указанная результирующая фув ция прео азованвя в рассматрвваемсвл случае (без учета погрешностей блока 3 и АЦП 4) имеет вид F (х)- х . Следовательно, производная давной фуккшш для некоторого зваченвя X Z-i равна J. FHx)(4) Разность Зд - .)( , полученная на выходе сумматора 7, делится в блоке lO ва вычисленное блоком 11 значение пров водной по формуле (4) в точке Zg . Частное от деления в блоке 1О, алгеброически суммируясь в сумматоре 8 с хранящимся в регистре памяти 6 кодом начального приближения, образует код нового приближения )-г1о Полученный код 2 переписывается с выхода сумматора 8 в ЦАП 9 и регистр памяти 6 (вместо кода начального прв ближения), откуда далее ввЬдится в блок 11. В следующем такте производится ачалого-1ш4ровое преобразование полученного ва выходе множительного блока 3 квадрата выходной величины ЦАП 9, определяем мой теперь значением введеввого в него кода 1.,. На выходе сумматора 7 образуется разность результата преобразования АЦП 4 кода -а и кода у, xpaeatщегсюя в регистре 5. Получентя разность делится в 10 на вычисленное 6nov ком 11 значение провзводвой фушсшт Р (х) в точке 2-J. Частное от деления, сул«мнруясь в сумматоре 8 с кодом регистра памяти 6 - г , образует код сяеяухлцего прибпюкевия -,- FCX.)II, Последующие втерацяв производятся анажя ичво вышеопвсашнжлу Результат п -го прибпижения к встивному цнфрово му эквввалевту { меряемой величины г« ярн будет определяться из выраже.- нвя:2 -7УГ - -n -«-i р/« «, ) /1ля скороста cxoftifttocTH алгоритма (7) справедлива опенка (1„-г)рЯ2„-.,-2,1 (8. -Авалоппнеш опеюса быстродействияустрЫ1ства ;гфШ9{Шяесь выше (см, виражеше 3) и плеет ваа VM-VRflM- ® Как вндво яз првведеввых выражений быстродействие нреалагаалого устройства выгце быс1 к действия известных, в то же , каряду с ксцфекаией погрешностей множительного блока 3 и АЦП 4, в устройстве обеспечивается отстройка от помех случайной 11рнроды. Формула изобретения 1 образователь аналоп-код, содержашнй переключатель, первый вход которого соединен с первой входной

ной, а второй с выходсы цифро-аналогового преобразователя, вход которого соеди нен с выходами первого сумматора и с входами первого регистра памяти, выходы которого соединены с первыми входами первого сумматора, аналого-ои овЫ преобразователь, выхощд которого соединены с первыми входами второго сумматсфа в второго регистра памяти, выходы последвего соедивены со вторьаля входами вторсяго сумматора, выхолы которого соединены с 11ерш 1ми входами бпснса д&левия, а с первого по четвертый выходы блсжа управления сое1ЕПнеиы с упрввляк шйми входами п явого 11ерекл1рчателя, ан лиго-цифрсдаого 11рео(% эовател0 и регистров памяти, отличающийся тем, что с целью яомлшешо быстродей ствия и точности 11рео 8зоваи1|1я, в&едены переключатель, блок ылчисления произш дной н М110жител1ЛЗ 1Й блок, вхо|Ш которого coemiHetSd с выходами переxif

ключателей, а выход - с входом аналогоцифрового преобразователя, при этом входы бпсжа вычисления производной соединены с выходами первого регистра памяти, а выходы - с вторыми входами блока деления, выхода которого соединены с вторыми входами первого сумматора, первый вход второго переключателя подключен к второй входной шине, второй вход - к выходу нифро-аналогового преобразователя, а у1фавляюш1й вход - к перво му выходу блока управления.

Источвики информации, принятые во при экспертизе

2,Авторское с| идетельство СССР № 760ОО1,, кл. Н ОЗ К 13/02, О1Д1.78.

Авторы

Даты

1982-05-23—Публикация

1980-07-21—Подача