вый 8, второй 9 и третий 10 цнфроана- логовые преобразователи (ЦАП), первый 11 и второй 12 блоки ввода, первый 13, второй 14, третий 15 сумматоры, первый 16, второй 17, третий 18, четвертый 19 и пятый 20 регистры, преобразователь 21 прямого кода в дополнительньш, коммутатор 22, nep-f вый 23 и второй 24 датчики, первый 25 и второй 26 выходы управления и первый 27, второй 28, третий 29 и четвертый 30 выходы синхронизации блока 1 управления, информационный выход 31, выходы аварии 32 и ошибки 33 первого блока 2 памяти, информационный выход 34, выходы аварии 35 и ошибки 36 второго блока 3 памяти, информационны выход 3/, выходы аварии 38 и ошибки 39 третьего блока 5 памяти. Выходы первого 8, второго 9 и третьего 10 цифроаналого- вых преобразователей являются первым, вторым и третьим выходами устройства. Такое выполнение устройства для программного управления позволяет повы-; сить достоверность функционирования и расширить область применения. 1 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах и устройствах программного управления, - обеспечивающих контроль и коррекцию информации, поступающей от датчиков. Цель изобретения - повьшение достоверности функционирования и расгаиренне области применения. Устройство содержит блок 1 управления, первый 2, второй 3, четвертый 4, третий 5 блоки памяти, первый 6 и второй 7 аналого- цифровые преобразователи (АЦП) пер- S с tsD О)

1)

Изобретение относится к автоматие и вычислительной технике и может быть использовано в системах и уст- ройствах программного управления, обеспечивающих контроль и коррекцию 5 информации, поступающей от датчиков параметров.

Цель изобретения - повышение достоверности функционирования и расширение области применения.

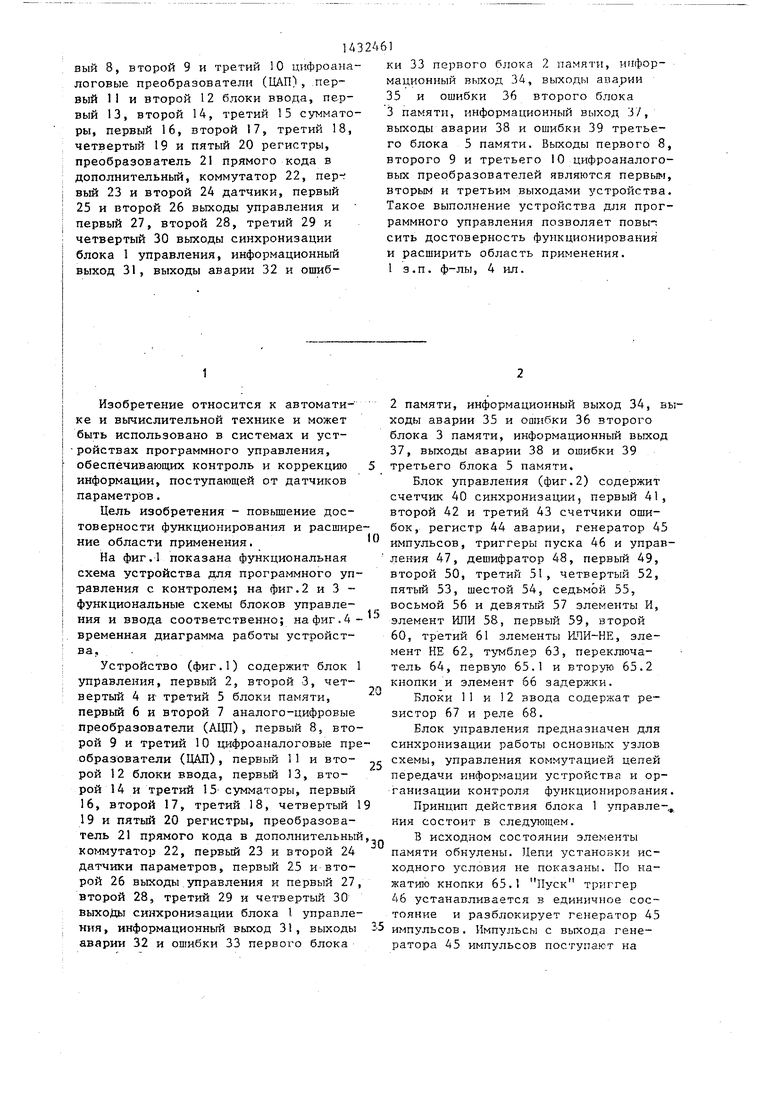

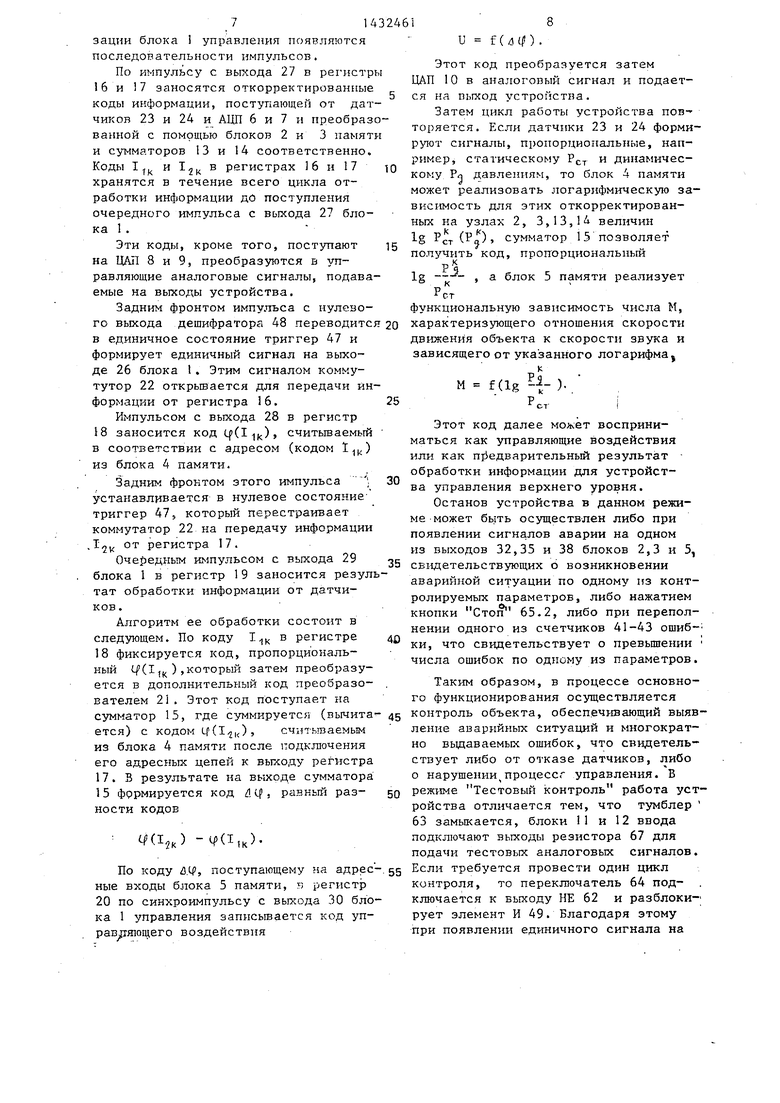

На фиг,1 показана функциональная схема устройства для программного упавления с контролем; на фиг.2 и 3 - функциональные схемы блоков управления и ввода соответственно; на фиг. 4- временная диаграмма работы устройства, .

Устройство (фиг.1) содержит блок 1 управления, первый 2, второй 3, четвертый 4 и- третий 5 блоки памяти, первый 6 и второй 7 аналого-цифровые преобразователи (АЦП), первый 8, второй 9 и третий 10 цифроаналоговые преобразователи (ЦАП) , первый I 1 и ВТО- ,,- рой 12 блоки ввода, первый 13, второй 14 и третий 1 5- сумматоры, первый 16, BTOpoii 17, третий 18, четвертый 19 19 и пятьй 20 регистры, преобразователь 21 прямого кода в дополнительный, коммутатор 22, первьй 23 и второй 24 датчики параметров, первый 25 и второй 26 выходы управления и первый 27, второй 28, третий 29 и четвертый 30 выходы синхронизации блока управления, информационный выход 31, выходы 35 аварии 32 и ошибки 33 первого блока

20

30

)

,,- 35

0

30

2 памяти, информационный выход 34, выходы аварии 35 и ошибки 36 второго блока 3 памяти, информационный выход 37, выходы аварии 38 и ошибки 39 третьего блока 5 памяти.

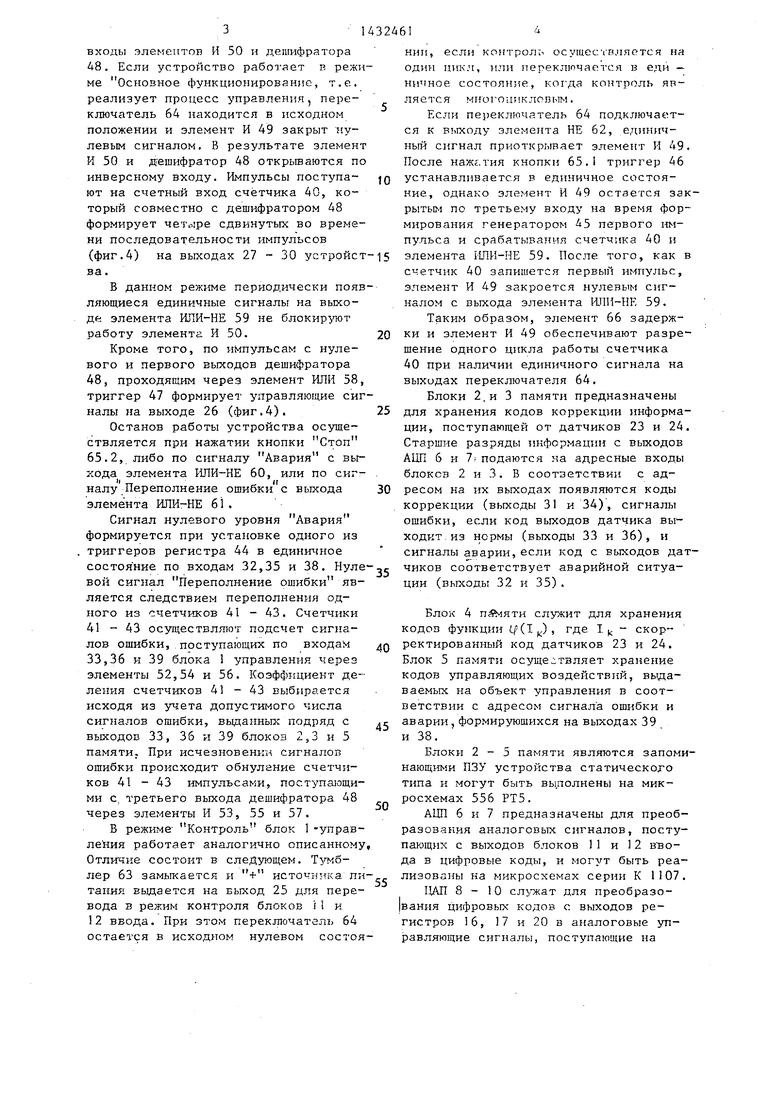

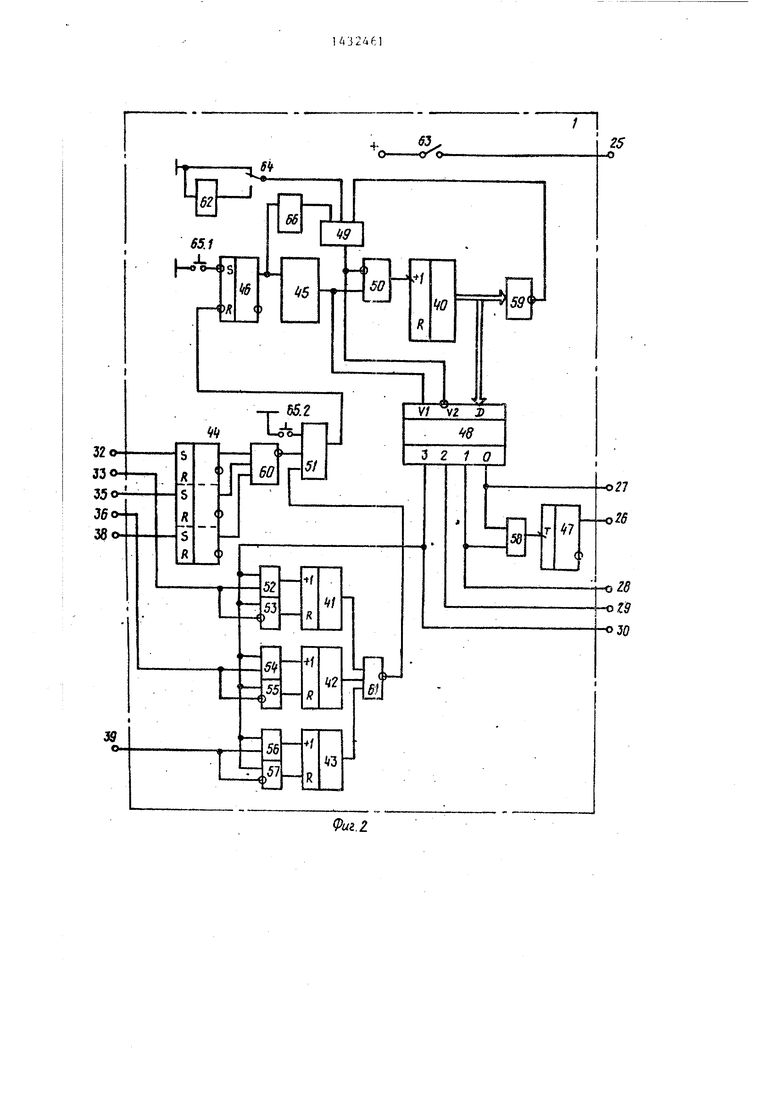

Блок управления (фиг.2) содержит счетчик 40 синхронизации, первый 41, второй 42 и третий 43 счетчики ошибок, регистр 44 аварии, генератор 45 импульсов, триггеры пуска 46 и управления 47, дешифратор 48, первый 49, второй 50, третий 51, четвертый 52, пятый 53, шестой 54, седьмой 55, восьмой 56 и девятый 57 элементы И, элемент ИЛИ 58, первый 59, второй 60, третий 61 элементы ИЛИ-НЕ, элемент НЕ 62, тумблер 63, переключатель 64, первую 65.1 и вторук 65.2 кнопки и элемент 66 задержки.

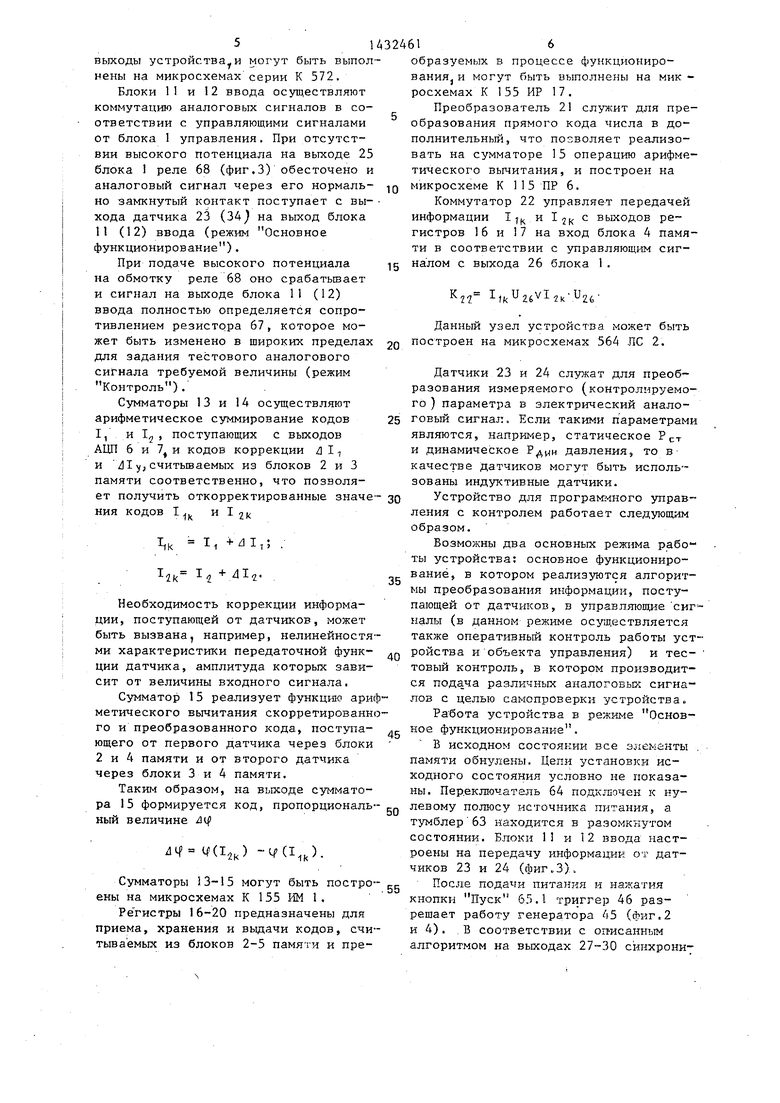

Блоки 11 и 12 ввода содержат резистор 67 и реле 68.

Блок управления предназначен для синхронизации работы основных узлов схемы, управления коммутацией цепей передачи информации устройства и организации контроля функционирования.

Принцип действия блока 1 управле-,. НИН состоит в следующем.

В исходном состоянии элементы памяти обнулены. Цепи устанонки исходного условия не показаны. По нажатию кнопки 65.1 Пуск триггер 46 устанавливается в единичное состояние и разблокирует генератор 45 импульсов. Импульсы с выхода генератора 45 импульсов поступают на

3

входы элемептои И 50 н дешифратора 48. Если устройство работает в режме Основное функционирование, т.е. реализует процесс управления, переключатель 64 находится в исходном положении и элемент И 49 закрыт левым сигналом. В результате элемен И 50 и дешифратор 48 открьшаются п инверсному входу. Импульсы поступа-

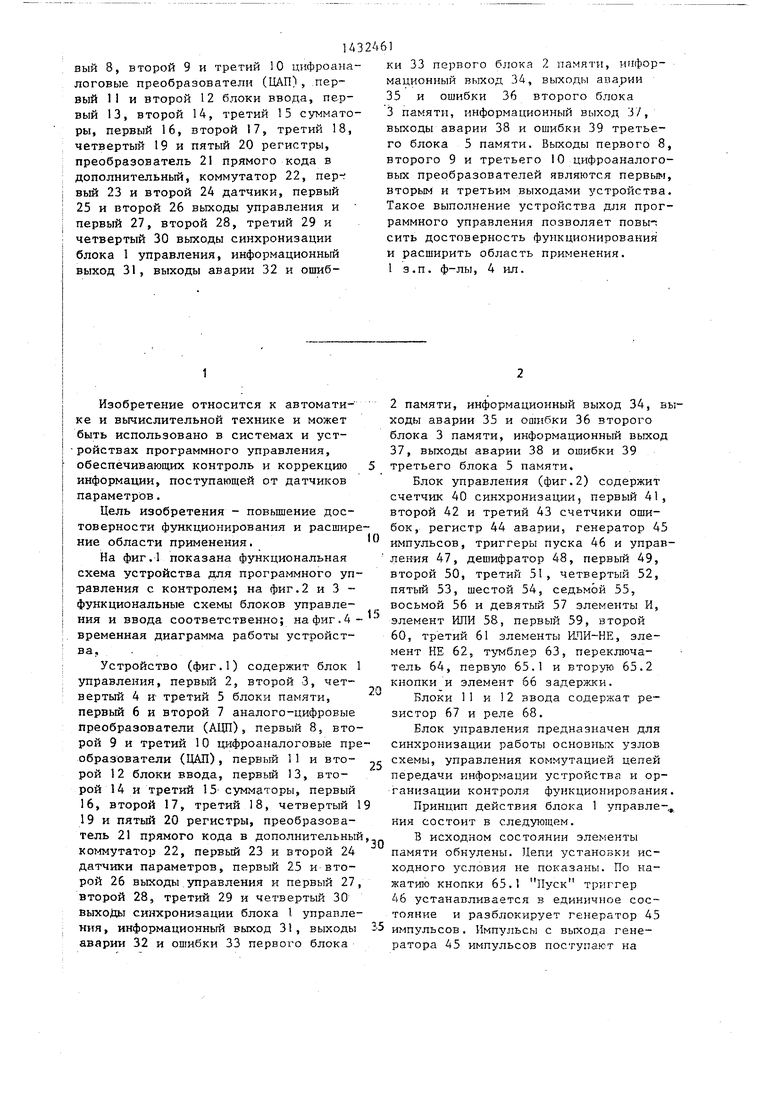

ют на счетный вход счётчика 40, который совместно с дешифратором 48 формирует четофе сдвинутых во времени последовательности импульсов (фиг.4) на выходах 27 - 30 устройс ва.

В данном режиме периодически пояляющиеся единичные сигналы на выходе элемента ИЛИ-НЕ 59 не блокир тот работу элемента И 50.

Кроме того, по импульсам с нулевого и первого выходов дешифратора 48, проходящим через элемент ИЛИ 58 триггер 47 формирует управляющие синалы на выходе 26 (фиг.4).

Останов работы устройства осуществляется при нажатии кнопки Стоп 65.2, либо по сигналу Авария с выхода элемента 1-1ПИ-НЕ 60, или по сиг

налу Переполнение ошибки с выхода

элемента ИЛИ-НЕ 61.

Сигнал нулевого уровня Авария формируется при установке одного из триггеров регистра 44 в единичное состоя ние по входам 32,35 и 38. Нуле вой сигнал Переполнение ошибки является следствием переполнения одного из счетчиков 41 -43. Счетчики 41 - 43 осуществля от подсчет сигналов ошибки, поступающих по входам 33,36 и 39 блока 1 управления через элементы 52,54 и 56. Коэффициент деления счетчиков 41 - 43 выбирается исходя из учета допустимого числа сигналов ошибки, выданных подряд с выходов 33, 36 и 39 блоков 2,3 и 5 памяти. При исчезновении сигналов ошибки происходит обнуление счетчиков 41-43 импульсами, поступающими с, третьего выхода дешифратора 48 через элементы И 53, 55 и 57.

В режиме Контроль блок 1-управ- лейия работает аналогично описанному Отличие состоит в следующем. лер 63 замыкается и + источника питания выдается на выход 25 для перевода в режим контроля блоков i1 и 12 ввода. При этом переключатгль 64 остается в исходном нулевом состоя

д

5

0

5

0

0

с

5

0

5

НИИ, если контрол;-. осущссч вляотся на один цикл, или переключается в еди - ничное состояние, ког да ко}1троль является миогоцпкловым.

Если переключатель 64 подключается к выходу элемента НЕ 62, единичный сигнал приоткрывает элемент И 49. После нажг.тия кнопки 65.1 триггер 46 устанавливается в единичное состояние, однако элемент И 49 остается закрытым по третьему входу на время формирования генератором 45 первого импульса и срабатывания счетчика 40 и элемента ШИ-НЕ 59. После того, как в счетчик 40 запишется первый импульс, элемент И 49 закроется нулевым сигналом с выхода элемента Ш1И-НЕ 59.

Таким образом, элемент 66 задержки и элемент И 49 обеспечивают разрешение одного цикла работы счетчика 40 при наличии единичного сигнала на выходах переключателя 64.

Блоки 2.и 3 памяти предназначены для хранения кодов коррекции информации, поступающей от датчиков 23 и 24. Старшие разряды информации с выходов АЦП 6 и 7i подаются на адресные входы блоков 2 и 3. В соответствии с адресом на их выходах появляются коды коррекции (выходы 31 и 34), сигналы ошибки, если код выходов датчика выходит из нормы (выходы 33 и 36), и сигналы аварии, если код с выходов датчиков соответствует аварийной ситуации (выходь 32 и 35) .

Блок 4 памяти служит для хранения кодов функции Ц (1), где 1| - скорректированный код датчиков 23 и 24. Блок 5 памяти осуще::твляет хранение кодов управляющих воздействий, выдаваемых на объект управления в соответствии с адресом сигнала ошибки и аварии, формирующихся на выходах 39 и 38.

Блоки 2-5 памяти являются запоминающими ПЗУ устройства статического типа и могут быть выполнены на микросхемах 556 РТ5.

АЦП 6 и 7 предназначены для преобразования аналоговых сигналов, поступающих с выходов блоков 1 и 12 в во- да в цифровые коды, и могут быть реализованы на микросхемах серии К 1107.

ЦАП 8-10 для преобразования цифровых кодов с выходов регистров 16, 17 и 20 в аналоговые управляющие сигналы, поступающие на

вькоды устройствами могут быть выполнены на микросхемах серии К 572.

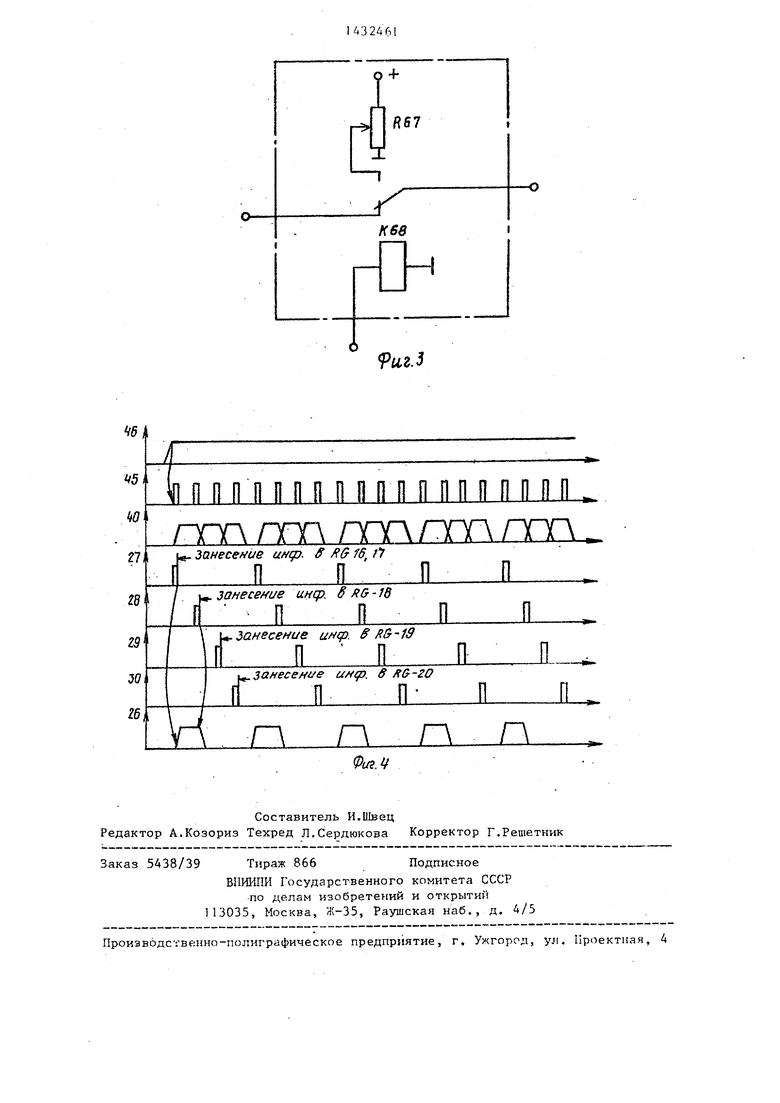

Блоки 1 и 12 ввода осуществляют коммутацию аналоговых сигналов в соответствии с управляющими сигналами от блока 1 управления, При отсутствии высокого потенциала на выходе 25 блока 1 реле 68 (фиг.3) обесточено и аналоговый сигнал через его нормаль- но замкнутый контакт поступает с вы- хода датчика 23 (34) на выход блока 11 (12) ввода (режим Основное функционирование).

При подаче высокого потенциала на обмотку реле 68 оно срабатьшает и сигнал на выходе блока 11 (12) ввода полностью определяется сопротивлением резистора 67, которое может быть изменено в широких пределах для задания тестового аналогового сигнала требуемой величины (режим Контроль).

Сумматоры 13 и 14 осуществляют арифметическое суммирование кодов I, и 1, поступающих с выходов АЦП 6 и 7 и кодов коррекции и I и Л у, считьшаемых из блоков 2 и 3 памяти соответственно, что позволяет получить откорректированные значе ния кодов и I 2к

I,h

1 + Л I,;

2k

I, + Л1,

Необходимость коррекции информации, поступающей от датчиков, может быть вызвана, например, нелинейностя- ми характеристики передаточной функ- Q ции датчика, амплитуда которых зависит от величины входного сигнала,

Сумматор 15 реализует функции арифметического вычитания скорретированн(5- го и преобразованного кода, поступа- ющего от первого датчика через блоки 2 и 4 памяти и от второго датчика через блоки 3 и 4 памяти.

Таким образом, на выходе сумматора 15 формируется код, пропорциональный величине Щ

50

А M-d

2k

) Ч (1,,).

Сумматоры 13-15 могут быть построены на микросхемах К 155 ИМ 1.

Ре гистры 16-20 предназначены для приема, хранения и выдачи кодов, считываемых из блоков 2-5 памяти и преобразуемых в процессе функциониро- вания и могут быть выполнены на мик - росхемах К 155 ИР 17.

Преобразователь 21 слуясит для преобразования прямого кода числа в до- полнительньй, что позволяет реализовать на сумматоре 15 операцию арифметического вычитания, и построен на микросхеме К 115 ПР 6.

Коммутатор 22 управляет передачей информации 11, и с выходов регистров 16 и 17 на вход блока 4 памяти в соответствии с управляющим сигналом с выхода 26 блока 1.

г Г I)kU26Vl2K-U26

g 0

5 о

5

Q

0

6

Данный узел устройства может быть построен на микросхемах 564 ЛС 2.

Датчики 23 и 24 служат для преобразования измеряемого (контролируемого ) параметра в электрический аналоговый сигнал. Если такими п араметрами являются, например, статическое Рст и динамическое давления, то в качестве датчиков могут быть использованы индуктивные датчики.

Устройство для программного управления с контролем работает следующим образом.

Возможны два основных режима рабо ты устройства; основное функционирование, в котором реализуются алгоритмы преобразования информации, поступающей от датчиков, в управляющие сигналы (в данном режиме осугдествляется также оперативный контроль работы устройства и объекта управления) и тестовый контроль, в котором производится подача различных аналоговых сигналов с целью самопроверки устройства.

Работа устройства в режиме Основное функционирование.

В исходном состоянии все элементы . памяти обнулены. Цепи установки исходного состояния условно не показаны. Переключатель 64 подключен к нулевому полюсу источника питания, а тумблер 63 находится в разомкнутом состоянии. Блоки 1 и 12 ввода настроены на передачу информации от датчиков 23 и 24 (фиг.З)

После подачи питания и нажатия кнопки Пуск 65.1 триггер 46 раз- рещает работу генератора 45 (фиг,2 и 4) . .В соответствии с отписанным алгоритмом на выходах 27-30 синхрони71432461

зацни блока i управления появляются последовательности импульсов.

По импульсу с выхода 27 в регистры 16 и 7 заносятся откорректированные коды информации, поступающей от датчиков 23 и 24 и АЦП 6 и 7 и преобразованной с помощью блоков 2 и 3 памяти и сумматоров 13 и 14 соответственно. Коды I |. и Iji в регистрах 16 и 17 io хранятся в течение всего цикла отработки информации до поступления очередного импульса с выхода 27 блока 1 .

Эти коды, кроме того, поступают ig на ЦАП 8 и 9, преобразуются в управляющие аналоговые сигналы, подаваемые на выходы устройства.

Задним фронтом импульса с нулезои fC/jtn.

Этот код преобразуется затем ЦАП 10 в аналоговый сигнал и подается на пыход устройства.

Затем пнкл работы устройства пов теряется. Е1СЛИ датчики 23 и 24 форми руют сигналы, пропорциональные, например, статическому Р(.-г и динамическому Pq давлениям, то блок 4 памяти может реализовать логарифмическую за висимость для этих откорректированных на узлах 2, 3,13,14 величин Ig Pj.(P), сумматор 15 позволяет получить код, пропорциональный

ТЭ

Ig - , а блок 5 памяти реализует

К

РСТ

функциональную зависимость числа М, го выхода дешифратора 48 переводится 2о характеризующего отношения скорости в единичное состояние триггер 47 и движения объекта к скорости звука и формирует единичный сигнал на выходе 26 блока 1. Этим сигналом комму- тутор 22 открьшается для передачи йнзависящего от указанного логарифма j к

).

М f(lg

формации от регистра 16,

Импульсом с выхода 28 в регистр 18 заносится код Cfi(I-|,), считьгоаемый в соответствии с адресом (кодом ц) из блока 4 памяти.

Задним фронтом этого импульса ; устанавливается в нулевое состояние триггер 47s который перестраивает коммутатор 22 на передачу информации , от регистра 17.

Очередным импульсом с выхода 29 блока 1 в регистр 19 заносится резултат обработки информации от датчиков ,

Алгоритм ее обработки состоит в следующем.. По коду 1 в регистре 18 фиксируется код, пропорциональный f(I, ),который затем преобразуется в дополнительный код преобразователем 21 . Этот код поступает на

сумматор 15, где суммируется (вычита- 45 контроль объекта, обесп.еч шающий выяв- ется) с кодом Lf(), считьшаемым из блока 4 памяти после подключения его адресных цепей к выходу регистра 17, В результате на выходе сумматора 15 фррмируется код Л с, равный разности кодов

I.J -(IIK)ленне аварийных ситуаций и многократно выдаваемых ошибок, что свидетельствует либо от отказе датчиков, либо о нарущенни процесс.- управления. В 5Q режиме Тестовый контроль работа устройства отличается тем, что тумблер 63 замыкается, блоки П и 12 ввода подключают выходы резистора 67 для подачи тестовых аналоговых сигналов. По коду u.(f, поступающему на адрес -. 55 Если требуется провести один цикл

контроля, то переключатель 64 подключается к выходу НЕ 62 и разблоки-; рует элемент И 49, Благодаря этому при появлении единичного сигнала на

ные входы блока 5 памяти, Р регистр 20 по синхроимпульсу с выхода 30 блока 1 управления записьшается код уп- рав гяющего воздействия

и fC/jtn.

Этот код преобразуется затем ЦАП 10 в аналоговый сигнал и подается на пыход устройства.

Затем пнкл работы устройства пов теряется. Е1СЛИ датчики 23 и 24 формируют сигналы, пропорциональные, например, статическому Р(.-г и динамическому Pq давлениям, то блок 4 памяти может реализовать логарифмическую зависимость для этих откорректированных на узлах 2, 3,13,14 величин Ig Pj.(P), сумматор 15 позволяет получить код, пропорциональный

ТЭ

Ig - , а блок 5 памяти реализует

К

РСТ

функциональную зависимость числа М, характеризующего отношения скорости движения объекта к скорости звука и

зависящего от указанного логарифма j к

).

М f(lg

0

Этот код далее может восприниматься как управляющие воздействия или как П13едварительный результат - обработки информации для устройства управления верхнего уровня.

Останов устройства в данном режиме может быть осуществлен либо при появлении сигналов аварии на одном из выходов 32,35 и 38 блоков 2,3 и 5, 5 свидетельствующих 6 возникновении

аварийной ситуации по одному из контролируемых параметров, либо нажатием кнопки Стоп 65.2, либо при переполнении одного из счетчиков 41-43 ошиб- ки, что свидетельствует о превьшении числа ошибок по одному из параметров.

Таким образом, в процессе основного функционирования осуществляется

0

выходе элемента ИЛИ-НЕ 59 после обнуления счетчика 40 обеспечивается блокировка подачи импульсов от генератора 45. Если требуется провести много- цикловый контроль, то переключатель 64 остается в исходном положении.

В этом режиме внешними средствами могут быть проанализированы величины

вьгкодных сигналов устройства, а впут-IQ рого аналого-дифровых преобразоватеренними средствами с .помощью регистра 44 и счетчиков 41-43 произведена проверка устройства по выдаче сигналов аварии и ошибки.

Таким образом, сущность изобретения состоит в повышении достоверности функционирования путем обеспечения возможности периодического тестового самоконтроля на основе подачи на вход

устройства контролирующих, воздействий 2о выход которого соединен с управлйющи- в различном диапазоне значений сигна- ми входами первого и второго блоков

лов и анализа, в осуществлении встроенного аппаратного контроля устройства и объекта управления по -граничным значениям локализации аварийных ситуаций, а также в расширении области применения за счет организации предварительной обработки информации, поступающей от датчиков, и ее коррекции.

Формула изобретения

соотБетстве1 ; о, выходы первого и второго аналого-цифровых преобразсвате лей соединены с первыми входами первого и второго сумматоров соответст- венпо, выходы которых соеди1 ены с HHtbopMaunoHHfcHviK входами первого и второго регистров соответственно., выходы старших разрядов первого и втолеи соединены с входами первого и второго блоков памяти соответственко, информадионные выходы которых соединены с вторыми входами первого и вто- рого сумматоров соответственно, выходы аварии первого, второго и треть- , его блоков памяти соединены соответственно с первьи - третьим входами блока управления, первый управляющий

ввода, второй управляющий выход соединен с управляющим входом коммутатора, первый выход синхронизации соединен с входами синхронизации первого и второго регистров, второй - четвертый выходы синхронизадии соединены с входами синхро}1изаи,ии третьего пятого регистров соотзетственно, пы

ходы первого и второго рег истров соединены с входами первого и второго цифроаналоговых ;1реобразователей, с первым и вторым информационньп 1и вхо- коммутатора соответственно5 выход которого соединен с входом четвертого блока памяти, выход которого соединен с первьм входом трс.тьего сумматора и с инфорг а-ционнь:;- входом третьего регистра, вьгход которого че-

рез-преобразователь кодов соедз нен с вторым входам третьего суммато-- ра, выход которого соединен с инфор- мационньпч входом четвертого регистра, выход четвертого регистра соединен с

входом третьего блока ггамят;-, информационный вькод которого соединен с информационным входом пятого регистра, выходы ошибки первого, второго и третьего блоков памяти соединены с

четвертым - шестььм входами блока управления соответственно3 выход пятого регистра через третей п,ифроанало говыйпреобразователь соединен с третьим выходом устройства,

триггеры пуска и управления, дешифратор, первый - девятый элементы И, элемент ИЛИ, первый - третий элементы ИЛИ-НЕ, элемент НЕ, тумблер, переключатель, первую и вторую кнопки, элемент задержки, причем шина положительного потенциала источника питания через тумблер соединена с первым

зшравляющим выходом блока управления, -JQ входом дешифратора, третий вход пер- первый - третий входы которого соеди- вого элемента И через элемент задерж- нены с первым - третьим входами регистра аварии соответственно, шина ну- нулевого потенциала источника питания

ки соединен с выходом триггера пуска, первый и второй выходы дешифратора соединены соответственно с первым

соединена с нормально замкнутым, а 15 и вторым входами элемента ИЛИ, вы- через элемент НЕ с нормально разомкну- ход которого соединен со счетным вхо- тыми контактами переключателя, выход дом триггера управления, выход кото- которого соединен с первым входом первого элемента И, выход первого элеменрого является вторым управляющим выходом блока управления, первый - трета И соединен с инверсным управляющим входом дешифратора и инверсным входом второго элемента И, выход кото рого соединен со счетным входом счетчика синхронизации, шина нулевого потенциала источника питания через первую и вторую кнопки соединена соответственно с единичным входом триг гера пуска и первым входом третьего элемента И, выход которого соединен

с нулевым входом триггера пуска, вы- ЗО ошибки через третий элемент ИЛИ-НЕ ходы счетчика синхронизации соединены |соединены с третьим входом Фретьего с информационными входами дешифратора, -элемента И, четвертый выход дешифра- первый - четвертый выходы которого тора, соединен с вторыми входами чет- . являются первым - четвертым выхода- вертого - девятого элементов И.

ми синхронизации блока управления соответственно, выходы счетчика синхронизации через первый элемент ИЛИ-НЕ соединены с вторым входом первого элемента И, выход триггера пуска соединен с входом генератора, выход которого соединен с прямым входом второго элемента И и прямым yпpaвляющIiм

входом дешифратора, третий вход пер- вого элемента И через элемент задерж-

ки соединен с выходом триггера пуска, первый и второй выходы дешифратора соединены соответственно с первым

и вторым входами элемента ИЛИ, вы- ход которого соединен со счетным вхо- дом триггера управления, выход кото-

рого является вторым управляющим выходом блока управления, первый - третий выходы регистра аварии через второй элемент ИЛИ-НЕ соединены с вторым входом третьего элемента И, i-й вход блока управления (i 4,5,6) соединен с первым входом г-го и инверсным входом (г+1)-го элементов И (), выходы которых соединены со счетным и установочным входами j-ro счетчика ошибки (J 1 i-3) соответственно, выходы первого - третьего счетчиков

К68

Риг.З

| Устройство программного управления с самоконтролем | 1981 |

|

SU999018A1 |

| Патент CIliA № 4109185, кл.318-571, 1978 | |||

| Способ управления процессом прессования порошкового материала и устройство для его осуществления | 1987 |

|

SU1507537A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1242945A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-03—Подача