, f

ff

4 rsD 4 О

ОЭ

Изобретение относится к вычисли- тел1люи TfXHUKf и может бмть использовано при пост1)О( нии арифметических устройств с инжекционным питанием на оснопе элементов многоуронневой логики .

Ноль изобретения - упрощение суыматора-вьп1итателя .

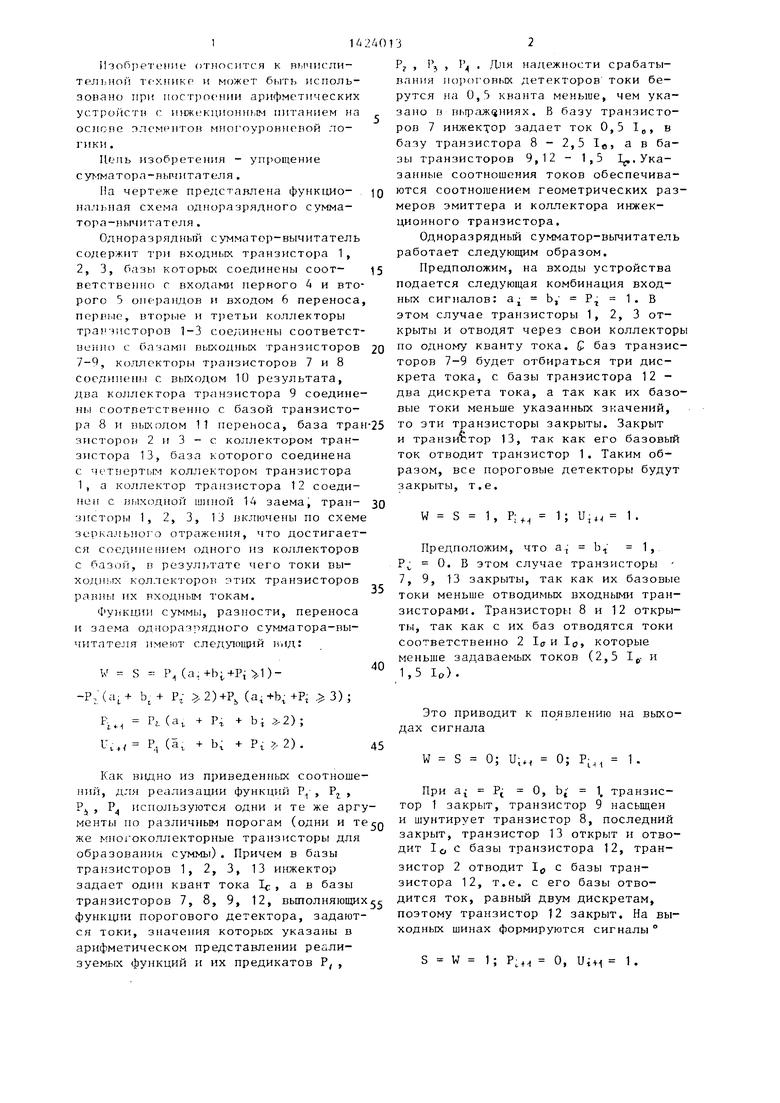

На чертеже представлена функгшо- на.чьная схема одноразрядного сумма- тора-вычитатсля.

Одноразрядный сумматор-вычитатель содержит три входньк транзистора 1, 2, 3, базы которых соединены соот- ветственно с входами первого 4 и второго 5 опс рандов и входом 6 переноса первые, вторые и Т1)етьи коллекторы тра зисторов 1-3 соединены соответст ненпо с базами выходных транзисторов 7-9, коллекторы транзисторов 7 и 8 Соединены с выходом 10 результата, два коллектора транзистора 9 соедине Н,1 соответственно с базой транзистора 8 и выходом 11 переноса, база тра зисторои 2 и 3 - с коллектором транзистора 13, база которого соединена с четиерТ)ГМ коллектором транзистора 1 , а коллектор транзистора 12 соединен с выходной шиной 14 завма, трап- зисторы 1, 2, 3, 13 включены по схем зеркалыюг-о отражения, что достигается соединением одного из коллекторов с базой, в резул1,тате чего токи выходных коллекторов этих транзисторов равны их входньм токам.

1 уикци11 суммы, разности, переноса и заема одноразрядного сумматора-вы- читателя имеют следупощий вид:

W S 1% (a,+bi,+Pi 1)-

-Р.(а,+ Р,- )+Р, (а,+Ц+Р, 3); Ь.н Р ( Ч + Рг + bi 2); . Р., (5. + Ь, + Р, и. 2).

Как В1ЩНО из приведенных соотношений, для реализации функций , Р , Р,. , Р используются одни и те же аргменты по различным порогам (одни и T же многоколлекторные транзисторы для образования суммы). Причем в базы транзисторов 1, 2, 3, 13 инжектор задает один квант тока 1 , а в базы транзисторов 7, 8, 9, 12, выполняющи функции порогового детектора, задаются токи, значения которых указаны в арифметическом представлении реализуемых функций и их предикатов Р, ,

Q

5 0 5 О

5

5

Рг РЛ Р наде-жности срабатывания ио1)оговь х детекторов токи берутся на 0,3 кванта меньше, чем указано в вьфаж(ниях. В базу транзисторов 7 инжектор задает ток 0,5 I, в базу транзистора 8 - 2,5 Те, а в базы транзисторов 9,12 - 1,5 1.Указанные соотношения токов обеспечиваются соотношением геометрических размеров эмиттера и коллектора инжек- ционного транзистора.

Одноразрядный сумматор-вычитатель работает следующим образом.

Предположим, на входы устройства подается следующая комбинация входных сигналов: а Ь, Р 1 . В этом случае транзисторы 1, 2, 3 открыты и отводят через свои коллекторы но одному кванту тока. С баз транзисторов 7-9 будет отбираться три дискрета тока, с базы транзистора 12 - два дискрета тока, а так как их базовые токи меньше указанных значений, то эти транзисторы закрыты. Закрыт и транзистор 13, так как его базовый ток отводит транзистор 1. Таким образом, все пороговые детекторы будут закрыты, т.е.

W S 1, Р;, 1; и,, 1.

Предположим, что а 1 Р 0. В этом случае транзисторы 7, 9, 13 закрыты, так как их базовые токи меньше отводимых входными транзисторами. Транзисторы 8 и 12 откры- Т1)1, так как с их баз отводятся токи соответственно 2 1аи 1о, которые меньше задаваемых токов (2,5 1р- и 1,5 1а).

Это приводит к появлению на выходах сигнала

W S 0; Ui. 0; Р, 1.

При а{ PJ О, 1, транзистор 1 закрыт, транзистор 9 насьщен и шунтирует транзистор 8, последний закрыт, транзистор 13 открыт и отводит 1о с базы транзистора 12, транзистор 2 отводит 1 с базы транзистора 12, т.е. с его базы отводится ток, равный двум дискретам, поэтому транзистор 12 закрыт. На выходных шинах формируются сигналы °

S W 1; Р;, О, Ui+1 1.

1/42/40

При b PL О, а 1 транзистор 7 закрыт, транзистор 9 насьпцеи и иунтирует транзистор 8. Транзистор 13 закрыт, а транзистор 12 открыт. На выходных uninax формируются сигналы

S W 1 ,

У.

О, Ui, 0.

Формула изобретения

Одноразрядный сумматор-вычитатель, содержапд1й три входных многоколлекторных транзистора, включенных по схеме зеркального отражателя, и четыре выходных транзистора, включенных по схеме порогового детектора, причем первые, вторые и третьи коллекторы входных транзисторов соединены соответственно с базами первого, второго и третьего выходньк транзисторов, четвертые коллекторы второго и треть

0

5 o

13

его входных транзисторов соединены с базой четвертого выходного транзистора, коллекторы первого и второго вы- выходных транзисторов соединены с выходом результата сумматора-пычитателя, первьвЧ и второй коллекторы третьего выходного транзистора соединены соответственнее с базой второго выходного транзистора и выходом переноса сумма- тора-вьтитателя, а коллектор четвертого выходного транзистора - с выходом заема сумматора-вычитателя, отличающийся тем, что, с целью упрощения сумматора-вычитателя, введен дополнительный транзистор, включенный по схеме токового отражателя, база которого соединена с четвертым коллектором первого входного транзистора, а коллектор - с базой четвертого выходного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Инжекционный сумматор-вычитатель | 1987 |

|

SU1471305A1 |

| Одноразрядный сумматор | 1982 |

|

SU1043641A2 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Полный одноразрядный сумматор инжекционного типа | 1980 |

|

SU892730A1 |

| Четырехуровневый сумматор-вычитатель | 1987 |

|

SU1422396A1 |

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Одноразрядный сумматор | 1988 |

|

SU1522193A1 |

Изобретение относятся к вычислительной технике и предназгитчоно для реализации в составе БИС с И1гаек- ционным питанием. Целью изобретения является упрощение суьгматора-вычита- теля. В одноразрядный сумт атор-вычи- татехгь, содержащий три входных транзистора 1, 2, 3 и четыре выходных транзистора 7, 8, 9, 12, введен дополнительный транзистор 13 и орга)Н1 зованы новые связи согласно вьфаже- ниям реализуемых функций, представленных в арифметическоь Г)лзисе,1 ил.

| Одноразрядный сумматор-вычитатель | 1983 |

|

SU1137462A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ определения инвариантного коэффициента устойчивости четырехполюсника | 1985 |

|

SU1335892A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1987-01-28—Подача