(54) ЦИФРОВОЙ ЧАСТОТОМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Цифровой частотомер | 1985 |

|

SU1247771A1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2326391C1 |

| Цифровой периодомер-частотомер | 1982 |

|

SU1064223A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Цифровой частотомер | 1980 |

|

SU892332A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 2008 |

|

RU2402025C2 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

Изобретение относится к цифровой электроизмерительной технике , Известен цифровой частотомер, содержащий генератор образцовой частоты, формирователь, вычитающий счетчик, два накапливающих суммат ч5а, блок угфавлени:я, ключи, схемы совпадения и управляющий триггер. Такой частотомер реализует ме тод измерения частоты, основанный на воспроизведении функции F(Ty) средствами импульсного моделирования с использованием цифровых интеграторов.. Известный частотомер характеризуется недостаточно высоким быстродействием, ограниченным переходными процессами в накапливающих сумматорах при параллельном вводе в них чисел, невысокой точностью, обусловленной методическими погрешностями приближенного интегрирова-tния и округления чисел в процессе вычисления,, а также сравнительно большими емкостями сумматоров, что повышает вероятность сбоев в процессе работы. Известен цифровой частотомер, в состав которого входят генератор тактовой частоты, два управляемых вентиля, вычиг тающий счетчик, формирователь, блок управления, система импульсно-потенциальных ключей, датчик калиброванных интервале времени, уоравл$1ющий триггер, делитель частоты, две схемы логического сложения н суммирующий счетчик 2. Недостатком такого частотомера является большое время измерения, которое заметно превосходит период входного сиг нала на величину калиброванного временного интервала, причем этот интервал должен, быть тем больще, чем меньшую погрешность измерения необходимо обеспечивать. Кроме того, к недостаткам частотомера следует отнести методическую погрешность, обусловленную неравномерностью следования импульсов обратной связи. Наиболее близким по технической сущности к предлагаемому является цифровой частотомер, позволяющий измерять

частоту за один период входного сигнала, который содержит формирователь импульсов, генератор эталонной частоты, счетчкки периода и частоты, сумматор, две группы вентилей переноса, элемент задер1Кки, вентили управления и трнггеРыИ.

Указанному частотомеру присуще ограниченное быстродействие, обусловленное наличием переходных прс«ессов в сумматоре.

Цель изобретения - повьпиение быстродействия измерений.

Указанная цель достигается тем, что в цифровой частотомер, содержащий сумматор, формирователь импульсов, выход которого подключен к первому входу блока управления, второй вход которого соединен с выходом генератора образцовой часгготы, первый выход блока управления соединен со входом счетчика периода, введены перемножитель кодов, шифратор и дешифратор, причем и выходов счетчика периода подключены к первой группе входов перемнонсителя кодов, вторая группа входов которого соединена с П-выходами сумматора, управляющий вход перемножителя кодов соединен со вторым выходом блока утфавления, управляющим входом шифратора, входом реверса суммато}: и (KI + 1) - выходом счетчика периода, остальные выходы которого начиная с (11+2) -го через дешифратор ПОДКЛЕО- чены ко входу адреса шифратора, выход Которого соединен со.входом сумматора, Y младших разрядов которого подключены к выходам перемножителя кодов.

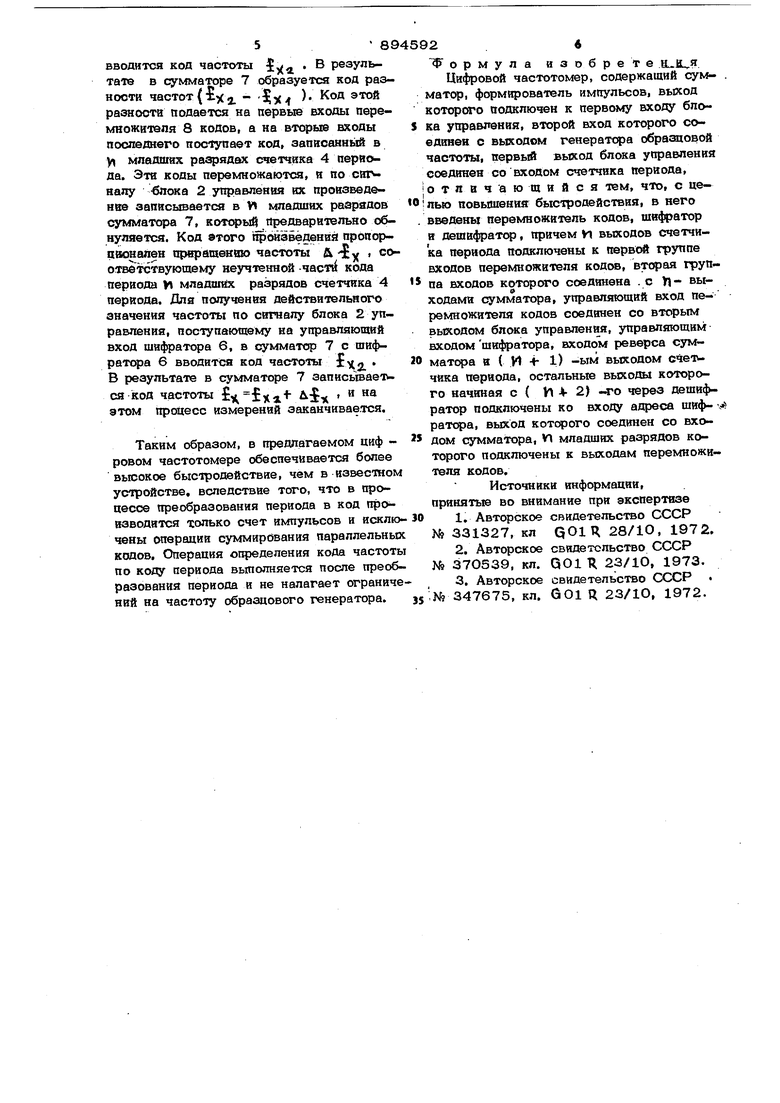

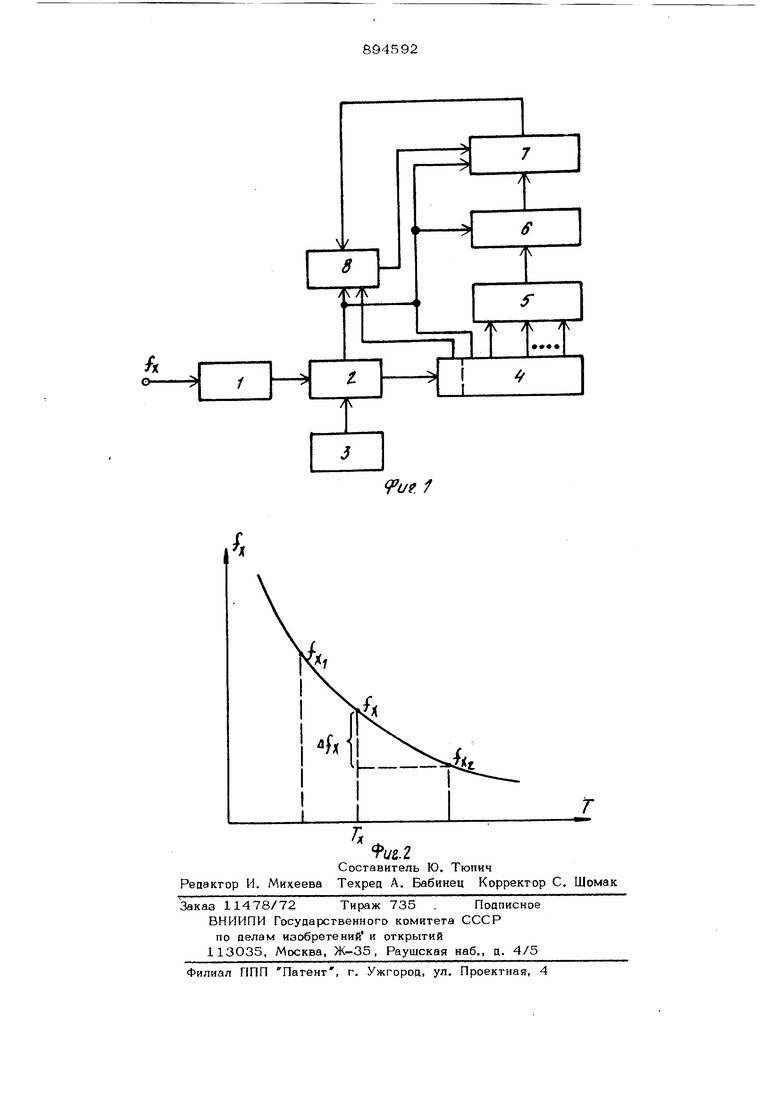

На фиг. 1 приведена блок-схема цифрового частотомера; на фиг, 2 - график, поясняющий его работу.

Устройство содержит формирователь 1 импульсов, блок 2 управления, генератор 3 образцовой частоты, счетчик 4 периода , дешифратор 5, шифратс э 6, сумматор 7 к перемножнтель 8 кодов.

Вход формирователя 1 импульсов яв . ляется входом устройства, выход его подключен к одному входу блока 2 управления, другой вход которого соединен с выходом генератора 3 образцовой частоты ПерВБ1Й выход блока 2 управления поДгключен к счетчику 4 периода, к выходам разрядов которого начиная с ( И 2)-го подключен дешифратор 5, соединенный выходом со входом адреса шифратора 6, . Шифратор б поразрядно подключен к сумматору 7, который выполнен реверсивным. Выходы Л- младших разрядов счетчика 4 периода подключены к первой группе входов перемножителя 8 кодов, вторая группа входов которого соединена с; выходами сумматора 7. Выходы перемножитепя 8 кодов подключены к У) младшим разрядам сумматора 7, Управляющие входы перемножителя 8 кодов и шифратора 6, вход реверса сумматора 7 и { И + 1) разряд счетчика 4 периода объединены между собой и подключены ко второму

выходу блока 2 управления.

Устройство работает следующим образом.

В исходном состоянии счетчик 4 -периода и сумматор 7 находятся в нулевом

5 состоянии. Измерение производится в два этапа. На первом этапе производится преобразование периода Т измеряемой частоты в код путем заполнения периода. которьй вьшеляется блоком 2 управпения по сигналам формирователя 1 импульсов, соответствующим переходам входного сигнала через нуль, импульсами с генератора 3 образцовой частоты ,

На втором этапе по коду Ту. определяется код частоты методу кусочнолинейной аппроксимации вычисления нелинейньк функций. Для этого шифратор 6 схемно выполнен таким, что в завнсимооти от сигнала на одном из его адресных входов и на его выходах формируется код частоты, соответствующий коду рериода в узлах аппроксимации. АдресньШ вход шифратора 6, а следовательно , в код частоты задаются дешифратором 5, который подключен к выходам разрядов счетчйка 4 периода начиная о ( Vl-+ 2)РО. Это означает, что код периода в общем случае берется с недостатком, если в v младших разрядах счетчика 4 периода имеется код. Пусть, напрмер, этому коду периода соответствует частота (фиг. 2), которая, очевидно, оказывается больше действительной, т. е. fy. Код частоты -Цл сигналу блока 2 управления записывается в сумматор 7 на суммирование.

Затем это значение указанной частоты уточняется интерполированием. Для этого в ( И + 1)-ый разряд счетчика 4 периода вводится единица по сигналу бл.

ка 2 управления, с дешифратора 5 подается разрешающий потенциал на еле дующий адресный вход шифратора 6, сот ответствующий ближайшему меньшему значению частоты, например, ху причем

V

5 5

у-.7 л Сигналом блока 2 управления, подаваемым на вход реверса сумматора 7, последний переводится в режим вычитания, а затем в него с шифратора 6 вводится код частоты $у . В результате в сумматоре 7 образуется код разности частот (. - ). Код этой разности подается на первые входы перемножитзпя 8 кодов, а на вторью входы последнего поступает код, записанный в у младших разрядах счетчика 4 периода. Эти коды перемножаются, и по сш%налу блока 2 управления их произведение записывается в Vf младших разрадоз сумматора 7, который предварительно обнуляется. Код Этого произведения пропорционален ггрвращеншо частоты ответствующему неучтенной -частп кода периода V младших разрядов счетчика 4 периода. Для получения действительного значения частоты по сигналу блока 2 управления, поступающему на управляющий вход шифратора 6, в сумматор 7 с ши4 ратсра 6 вводится код частоты . В результате в сумматоре 7 записываети ся код частоты $ц этом процесс измерений заканчивается. Таким образом, в предлагаемом циф ровом частотомере обеспечивается более высокое быстродействие, чем в известном ус ойстве, вследствие тсго, что в процессе преобразования периода в код про изводнтся только счет импульсов и исклю чены сотерации суммирования параллельны кодов. Операция определения коДа частоты по коду периода вьтолняется после преоб разования периода и не налагает ограниче ний на частоту образцового генератора. Формула изобрете BLJai H Цифровой частотомер, содержащий сум- . матор, формирователь импульсов, выход KOTopcsro подключен к первому входу блока управления, второй вход которого соединен с выходом генератора образцовой частоты, первый выход блока управления соединен со входом счетчика периода, отличающийся тем, что, с цепью повышения быстродействия, в него введены перамножитель кодов, шифратор и дешифрат(чэ, причем И выходов счетчика периода подключены к первой группе входов перемножитепя коасъ, вторая группа входов которого соединена .с выходами сумматора, управляющий вход перемножителя кодов соединен со вторым выходом блока управления, управляющим входом шифратора, входом реверса сумматора и ( И -f 1) -ым выходом счети чика периода, остальные выходы которого начиная с ( И 4- 2) -го через дешифратор подключены ко входу адреса шиф- v ратора, выход которого соединен со вхоДом сумматора, VI младших разрядов которого подключены к выходам перемножителя кодов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР М 331327, кл QO1R 28/10, 1972. 2.Авторское свидетельство СССР N 370539, кл. Q01 Я 23/1О, 1973. 3.Авторское свидетельство СССР М 347675, кл. GOI R 23/1О, 1972.

Авторы

Даты

1981-12-30—Публикация

1980-05-05—Подача