Изобретение относится к контрольно-измерительной технике и может быть использовано в системах автоматического измерения, регулирования и аварийной защиты, в которых исходная информация, подлежащая анализу, представлена в частотной форме.

Известен способ измерения частоты импульсов [1], основанный на формировании эталонных меток времени с периодом То и образцовых интервалов времени Тоб, а также числа М периодов измеряемой частоты в образцовом интервале с последующим вычислением текущей частоты по формуле Fтек=M/Тоб, причем границы образцовых интервалов устанавливаются по моментам прихода импульсов измеряемой частоты, положение этих границ определяется по числу эталонных меток времени от начала предельного интервала, выбираемого большим или равным периоду низшей измеряемой частоты, до начала (Nн) и конца (Nк) образцового интервала, а длительность образцового интервала определяется как Tоб=To·(Nк-Nн).

Первым существенным недостатком этого способа является его низкая надежность измерения частоты, обусловленная возможностью сбоев в измерении, вызванных асинхронностью (неразделенностью во времени) некоторых процессов счета импульсов и запоминания полученной информации, а также асинхронностью процессов запоминания полученных в результате счета чисел М, Nн, Nк и считывания этих чисел микропроцессорной системой (ПЭВМ) для вычисления значения частоты. Случайное совпадение по времени этих асинхронных процессов может привести к искажению информации и тем самым к недопустимо большим значениям погрешности измерения, что равнозначно сбою в измерении.

Вторым существенным недостатком рассматриваемого способа измерения частоты является сложность его аппаратурной и программной реализации, что вызвано прежде всего наличием четырех опорных интервалов времени и многоступенчатой системы передачи и запоминания полученной в результате измерения информации. Кроме того, при измерении может оказаться, что Nк<Nн, поэтому алгоритм определения частоты должен включать в себя дополнительные операции, связанные с определением знака разности Nк-Nн и вычислением частоты по более сложной формуле.

Известен также способ измерения частоты [2], заключающийся в преобразовании исследуемых сигналов частоты Fx в исследуемую последовательность импульсов той же частоты Fx, в осуществлении одновременного счета n импульсов исследуемой последовательности импульсов и N счетных импульсов частоты Fсч, в определении значения частоты исследуемых сигналов по формуле Fx=n·Fсч/N, в создании последовательности импульсов образцовой частоты Fо из которой формируют счетные импульсы с частотой Fсч, причем фронт каждого такого импульса формируют на срезе соответствующего импульса образцовой частоты, а также формируют первую последовательность импульсов с периодом следования Δt1, формируют вторую последовательность импульсов с периодом следования Δt2, фронт каждого импульса которой соответствует фронту импульса исследуемой последовательности импульсов, появившегося сразу после фронта соответствующего импульса первой последовательности импульсов, после фронта каждого импульса второй последовательности импульсов и окончания действующего во время этого фронта импульса образцовой частоты или окончания возникшего после этого же фронта импульса образцовой частоты на фронте очередного импульса образцовой частоты начинают выполнять с тактом Ti, равным периоду То следования импульсов образцовой частоты, тактируемую последовательность операций, причем на первом такте Т1 запрещают счет n импульсов исследуемой последовательности импульсов и N счетных импульсов, на втором такте Т2 фиксируют значения чисел n и N, полученные в результате предыдущего счета соответственно импульсов исследуемой последовательности импульсов и счетных импульсов, на третьем такте Т3 формируют сигнал RDY готовности зафиксированных значений чисел n, N и осуществляют подготовку нового счета, на четвертом такте Т4 начинают новый одновременный счет n импульсов исследуемой последовательности и N счетных импульсов, а определение частоты Fx исследуемых сигналов осуществляют по сигналу RDY готовности зафиксированных значений чисел n и N или в любое время в течение нового одновременного счета n импульсов исследуемой последовательности и N счетных импульсов.

Из описания принципа действия частотомеров, работающих в режиме измерения периода Тх [3], следует способ измерения частоты, принятый за прототип и заключающийся в измерении длительности периода Тх следования сигналов и в последующем определении частоты fx как величины, обратной измеренному периоду, причем для измерения периода Тх используют двоичный счетчик, в котором в процессе измерения каждого периода Тх в диапазоне от Txmin до Тхmax получают соответствующие числа Nт, предварительно определяют число nmin младших разрядов этого счетчика, обеспечивающих измерение минимального периода Тхmin с погрешностью дискретности, не превышающей допустимого значения δт, определяют частоту fсч заполнения счетчика с учетом величины Txmin и числа Nтmin, получаемого в счетчике при измерении Txmin, определяют общее число nmax разрядов счетчика исходя из величины максимального периода Тхmax измеряемой частоты, после окончания каждого периода Тх полученное в результате измерения число Nтк передают в микропроцессорную систему, где производят вычисление частоты fx=1/Тх=1/(Nтк·Тсч)=fсч/Nтк.

Существенным недостатком способа-прототипа, как и рассмотренных выше двух аналогов, является низкая надежность измерения частоты, обусловленная сложностью преобразования гиперболической функции fx=1/Tx и применением для этой цели микропроцессорной системы, использование которой в каждом периферийном модуле измерения частоты и в центральном блоке многоканальной системы измерения, контроля управления исследуемым объектом усложняет эту систему и тем самым делает ее ненадежной.

Рассматриваемую гиперболическую функцию, помимо микропроцессорной системы, можно реализовать [4] с помощью функционального преобразователя, специальных блоков, суммирующих код Nтк до определенного числа N0 или вычитающих этот код из числа N0 до 0 или другими способами. Однако такие решения получаются не менее сложными, чем выполнение этой функции с помощью микропроцессорной системы, и, кроме того, они не обеспечивают высокой точности и быстродействия преобразования.

Применение для этой цели микропроцессорной системы загружает ее выполнением рутинных вычислительных операции, не позволяет использовать эту систему для решения задач более высокого уровня, связанных с измерением, контролем нескольких параметров и управлением исследуемым объектом.

Известное устройство [5], принятое за аналог, выполняет измерение частоты по методу функционального кодирования периода при воспроизведении гиперболической зависимости вида fx=1/Tx.

Устройство состоит из входного формирователя импульсов, формирователя измерительного интервала, двоичных счетчиков периодов и частоты, двоичных комбинированного и накапливающего сумматоров, двоичного счетчика результата, блока цифровой индикации и элемента И.

Первым существенным недостатком этого устройства является сложная аппаратурная реализация: в 1 его состав входят 4 двоичных счетчика, 2 двоичных комбинационных сумматора, 2 одновибратора, регистр памяти, 7 установочных кодовых шин и другие логические элементы.

Вторым существенным недостатком рассматриваемого устройства является сложность алгоритма его работы, включающего процедуру воспроизведения траектории гиперболы.

Третьим существенным недостатком устройства является то, что оно не обеспечивает непрерывного (период за периодом) измерения частоты: в нем такт измерения частоты, в начале которого производится установка всех блоков устройства в исходное состояние, должен превосходить длительность самого большого периода измеряемой частоты. В результате этого при работе на высокой частоте измерение частоты производится только в течение первого периода, длительность всех последующих периодов составляет «мертвую зону», в которой измерение не выполняется.

Четвертым существенным недостатком этого устройства является ограниченный диапазон измерения частоты, так как при измерении частоты в широком диапазоне существенно увеличивается «мертвая зона».

Перечисленные четыре недостатка значительно снижают надежность измерения частоты.

Наиболее близким по технической сущности и достижимому положительному эффекту к заявленному устройству - прототипом является устройство [6], включающее в себя (фиг.1) формирователь импульсов 1, блок управления 2, генератор 3 образцовой частоты, блок 4 счета импульсов образцовой частоты, регистр 5, формирователь 8 сигнала «Готовность» и блок 15 ключей.

В устройстве осуществляется преобразование каждого периода Тх следования сигналов в код Nтк, по которому затем может быть определено соответствующее значение частоты fx=к/Nтк, где к - коэффициент пропорциональности.

Существенным недостатком рассматриваемого устройства является то, что использование его для измерения частоты сопряжено со сложностью процесса вычисления обратной функции fx=1/Tx и необходимостью применения для этой цели микропроцессорной системы.

Все рассмотренные ранее аналоги и прототипы предлагаемых способа измерения частоты и устройства для его осуществления имеют, кроме отмеченных выше недостатков, один общий существенный недостаток, снижающий надежность измерения частоты и заключающийся в том, что в них не предусмотрено представление результатов измерения частоты в компактной форме, удобной для передачи и записи в систему телеметрии и для обработки данных в системе контроля и управления исследуемым объектом.

Задачей предлагаемого способа измерения частоты и устройства для его осуществления является повышение надежности измерения частоты путем упрощения процесса преобразования кода периода в код частоты посредством использования постоянного запоминающего устройства (ПЗУ), а также путем формирования результатов измерения частоты в компактной форме, представляющей собой мантиссу с числом nmin двоичных разрядов, обеспечивающих требуемую точность измерения, и двоичный код порядка полученного значения частоты.

Поставленная задача достигается тем, что в способе измерения частоты, заключающемся в измерении длительности периода Тх следования сигналов и в последующем определении частоты fx как величины, обратной измеренному периоду, причем для измерения периода Тх используют двоичный счетчик, в котором в процессе измерения каждого периода Тх в диапазоне от Txmin до Тхmax получают соответствующие числа Nт, предварительно определяют число nmin младших разрядов этого счетчика, обеспечивающих измерение минимального периода Тхmin с погрешностью дискретности, не превышающей допустимого значения δт, определяют частоту fсч заполнения счетчика с учетом величины Тхmin и числа Nткmin, получаемого в счетчике при измерении Txmin, определяют общее число nmax разрядов счетчика исходя из величины максимального периода Тхmax измеряемой частоты, в отличие от прототипа:

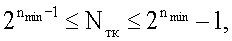

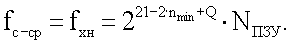

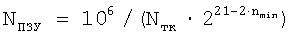

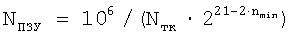

1) задают значение частоты fсч, округленное в сторону увеличения до ближайшей величины fсч=2Q·106 Гц, где Q - целое положительное или отрицательное число, подают числа Nтк, получаемые после окончания измерения периода Тх в nmin младших разрядах счетчика, на адресные входы ПЗУ, в ячейках памяти которого хранятся предварительно записанные числа NПЗУ, пропорциональные соответствующим значениям fc частоты сигналов, причем при предварительной записи в ПЗУ для каждого значения Nтк в диапазоне от  до

до  определяют значения чисел NПЗУ:

определяют значения чисел NПЗУ:

при измерении частоты, величина Nтк периода которой занимает nmin младших разрядов счетчика и отвечает условию  частоту исследуемых сигналов определяют по формуле:

частоту исследуемых сигналов определяют по формуле:

fхн=NПЗУ·2с1, где с1=21-2·nmin+Q,

при измерении частоты, величина Nтк периода которой занимает число nизм младших разрядов счетчика и при этом выполняются условия nmin<nизм≤nmax, nизм=nmin+m1, производят m1 раз сдвиг числа Nтк в сторону младших разрядов, запоминают число m1 проведенных сдвигов и определяют частоту fx1 исследуемых сигналов по формуле:

fх1=fхн·2-m1=NПЗУ·2-m1·2с1.

2) в отличие от п.1 подают числа Nтк, получаемые в nmin старших (вместо младших по п.1) разрядах счетчика, на адресные входы ПЗУ, при измерении частоты, величина Nтк периода которой занимает nизм младших разрядов счетчика и при этом выполняются условия nmin≤nизм<nmax, nизм=nmax-m2, производят m2 раза сдвиг числа Nтк в сторону старших разрядов, запоминают число m2 проведенных сдвигов и определяют частоту fх2 исследуемых сигналов по формуле:

fx2=NПЗУ·2m2·2с2, где с2=21-nmax-nmin+Q.

Поставленная задача достигается тем, что в устройство для измерения частоты, содержащее формирователь импульсов, блок управления, генератор образцовой частоты, блок счета импульсов образцовой частоты, регистр и формирователь сигнала «Готовность», причем вход устройства соединен через формирователь импульсов с первым входом блока управления, третий вход которого подключен к первому выходу генератора образцовой частоты, второй выход этого генератора соединен с первым входом блока счета импульсов образцовой частоты, второй вход которого подключен к первому выходу блока управления, третий вход - к второму выходу блока управления, а выход данных подключен шиной к входу данных регистра, выход формирователя сигнала «Готовность» соединен с одноименным выходом устройства, при этом в состав блока счета импульсов образцовой частоты входит двоичный счетчик, количество nmin разрядов которого определяется значением δт допустимой погрешности дискретности измерения минимального Тхmin периода, а общее число nmax разрядов этого счетчика задается исходя из величины максимального периода Тхmax измеряемой частоты, в отличие от прототипа:

1) введены постоянное запоминающее устройство, счетчик числа сдвигов кода и буферный регистр, а вместо регистра применен регистр сдвига, входы адреса ПЗУ соединены шиной с выходами nmin старших разрядов регистра сдвига, вход данных которого подключен к выходу «Код периода» устройства, старший разряд выхода данных регистра сдвига соединен с четвертым входом блока управления, второй вход которого подключен к второму выходу генератора образцовой частоты, а третий, четвертый и пятый выходы блока управления подключены соответственно к двум входам выбора режима и тактовому входу регистра сдвига, выход данных ПЗУ соединен шиной с первым входом данных буферного регистра, второй вход данных которого подключен шиной к выходу данных счетчика числа сдвигов кода, третий вход - к восьмому выходу блока управления, четвертый вход - к входу «Считывание» устройства, а выход данных буферного регистра подключен шиной к выходу данных устройства, седьмой выход блока управления соединен с входом обнуления счетчика числа сдвигов кода, тактовый вход которого подключен к шестому выходу блока управления, девятый выход блока управления соединен с первым входом формирователя сигнала «Готовность», второй вход которого подключен к десятому выходу блока управления;

2) в отличие от п.1 входы адреса ПЗУ соединены шиной с выходами nmin младших (вместо старших по п.1) разрядов регистра сдвига и в него введен элемент ИЛИ-НЕ, входы которого подключены к Δn=nmax-nmin старшим разрядам регистра сдвига, кроме того, в нем четвертый вход блока управления отключен от старшего разряда регистра сдвига и подключен к выходу элемента ИЛИ-НЕ.

Сопоставительный анализ заявленного технического решения с прототипом способа показывает, что оно отличается от известного тем, что в нем:

1) задают значение частоты fсч, округленное в сторону увеличения до ближайшей величины fсч=2Q·106 Гц, где Q - целое положительное или отрицательное число;

2) подают числа Nтк, получаемые после окончания измерения периода Тх в nmin младших разрядах счетчика, на адресные входы постоянного запоминающего устройства, в ячейках памяти которого хранятся предварительно записанные числа NПЗУ, пропорциональные соответствующим значениям fc частоты сигналов, причем при предварительной записи в ПЗУ для каждого значения Nтк в диапазоне от  до

до  определяют значения чисел NПЗУ:

определяют значения чисел NПЗУ:

;

;

3) при измерении частоты, величина Nтк периода которой занимает nmin младших разрядов счетчика и отвечает условию  частоту исследуемых сигналов определяют по формуле:

частоту исследуемых сигналов определяют по формуле:

fхн=NПЗУ·2с1, где с1=21-2·nmin+Q;

4) при измерении частоты, величина Nтк периода которой занимает число nизм младших разрядов счетчика и при этом выполняются условия nmin<nизм≤nmax, nизм=nmin+m1, производят m1 раз сдвиг числа Nтк в сторону младших разрядов, запоминают число m1 проведенных сдвигов и определяют частоту fx1 исследуемых сигналов по формуле:

fх1=fхн·2-m1=NПЗУ·2-m1·2с1;

5) в отличие от п.2-4 подают числа Nтк, получаемые в nmin старших (вместо младших по п.2 формулы) разрядах счетчика, на адресные входы ПЗУ, при измерении частоты, величина Nтк периода которой занимает nизм младших разрядов счетчика и при этом выполняются условия nmin≤nизм<nmax, nизм=nmax-m2, производят m2 раза сдвиг числа Nтк в сторону старших разрядов, запоминают число m2 проведенных сдвигов и определяют частоту fх2 исследуемых сигналов по формуле:

fx2=NПЗУ·2m2·2с2, где с2=21-nmax-nmin+Q.

Сопоставительный анализ заявленного технического решения с прототипом устройства показывает, что оно отличается от известного тем, что в нем:

1) введены постоянное запоминающее устройство, счетчик числа сдвигов кода и буферный регистр;

2) вместо регистра применен регистр сдвига;

3) входы адреса ПЗУ соединены шиной с выходами nmin старших разрядов регистра сдвига, вход данных которого подключен к выходу «Код периода» устройства, старший разряд выхода данных регистра сдвига соединен с четвертым входом блока управления, второй вход которого подключен к второму выходу генератора образцовой частоты, а третий, четвертый и пятый выходы блока управления подключены соответственно к двум входам выбора режима и тактовому входу регистра сдвига, выход данных ПЗУ соединен шиной с первым входом данных буферного регистра, второй вход данных которого подключен шиной к выходу данных счетчика числа сдвигов кода, третий вход - к восьмому выходу блока управления, четвертый вход - к входу «Считывание» устройства, а выход данных буферного регистра подключен шиной к выходу данных устройства, седьмой выход блока управления соединен с входом обнуления счетчика числа сдвигов кода, тактовый вход которого подключен к шестому выходу блока управления, девятый выход блока управления соединен с первым входом формирователя сигнала «Готовность», второй вход которого подключен к десятому выходу блока управления;

4) в отличие от п.3 в устройстве входы адреса ПЗУ соединены шиной с выходами nmin младших (вместо старших по п.3) разрядов регистра сдвига и в него введен элемент ИЛИ-НЕ, входы которого подключены к Δn=nmax-nmin старшим разрядам регистра сдвига, кроме того, в нем четвертый вход блока управления отключен от старшего разряда регистра сдвига и подключен к выходу элемента ИЛИ-НЕ.

Перечисленные отличия предлагаемого способа измерения частоты и устройства для его осуществления позволяют сделать вывод о соответствии заявленного технического решения критерию «новизна». Эти признаки не выявлены в других технических решениях при изучении данной и смежных областей техники, позволяют получить новое качество и существенное отличие: обеспечивают повышение надежности измерения частоты путем упрощения процесса преобразования кода периода в код частоты посредством использования ПЗУ, а также путем формирования результатов измерения частоты в компактной форме, представляющей собой мантиссу с числом nmin двоичных разрядов, обеспечивающих требуемую точность измерения, и двоичный код порядка полученного значения частоты.

В таблицах 1-3 и на фиг.1-3 приняты следующие обозначения и сокращения, не отмеченные в тексте описания:

СТ, RG - соответственно двоичные счетчик и регистр;

MP, CP - соответственно младший и старший разряды СТ или RG;

№CP CT - номер старшего разряда счетчика;

емк. - емкость CT, RG или их разрядов;

Nт - числа (коды), 1 формируемые в счетчике в процессе преобразования периода Тх в код;

Nтк - число (код), полученный в счетчике по окончании периода Тх;

Nтк-15, Nтк-8 - числа, записанные соответственно в СТ или RG, имеющие 15 разрядов, или в их часть, состоящую из 8 разрядов;

nmin - минимальное число разрядов СТ, обеспечивающих требуемую точность измерения периода;

nmin-мр, nmin-ср - число nmin соответственно младших и старших разрядов СТ или RG;

обозначения типа:

поз.1 - позиция 1, строка под №1 в таблице;

fx(1), fсч(3/1), ТМ(2-3), И(2-5) - сигналы, поступающие соответственно из выхода формирователя 1, первого выхода генератора 3, выхода триггера 3 блока 2, схемы И 5 блока 2;

Nст(7), Nтк(4-1), NRG(5), NAD(6), NПЗУ(6) - числа, имеющиеся соответственно в счетчике 7, в счетчике 1 блока 4, в регистре 5, на адресном входе AD и на выходе ПЗУ 6;

D2/CP, D5(9) - числа, имеющиеся соответственно в старшем разряде шины D2 и на шине D5 буферного регистра 9 (на шине 12 устройства).

Шины данных, приведенные на блок-схемах фиг.1 и 2, имеют следующие разряды:

D1[0÷(nmax-1)]; D2[0÷(nmin-2)]; D2/CP(nmin-1); D3[0÷(nmin-1)];

D4[0÷(к-1)]; D5[0÷(nmin+к-1)]; D6=D1; D6/1(nmax); D7(0÷nmax).

На фиг.1-4 представлены:

- фиг.1 - блок-схема устройства-прототипа;

- фиг.2 - блок-схема предлагаемого устройства;

- фиг.3 - временные диаграммы работы предлагаемого устройства.

В таблицах 1÷3 представлены:

- табл.1 - разряды двоичного счетчика, их емкости, а также некоторые значения частоты fc, коэффициентов к1 к и чисел NПЗУ;

- табл.2 - иллюстрация процесса сдвига двоичного кода Nтк в сторону старших разрядов;

- табл.3 - иллюстрация процесса сдвигов двоичного кода числа 1250 в сторону младших и старших разрядов.

В предлагаемом способе измерения частоты определяют число nmin младших разрядов счетчика, обеспечивающих измерение минимального периода Txmin с погрешностью дискретности, не превышающей допустимого значения δт. Пусть, например, задано δт=0,01=1%. Такому требованию будет удовлетворять число nmin=8 (табл.1), при котором запись «1» в восьмой разряд равнозначна подаче на вход счетчика Nткmin=128 импульсов, что будет соответствовать погрешности измерения Txmin, равной δт=1/128=0,78%.

Пусть, например, необходимо измерять частоту сигналов в диапазоне от fmin=5 Гц до fmax=500 Гц. Тогда Txmin=1/fmax=2 мс, Txmax=1/fmin=200 мс. Период Тсч и частота fсч счетных импульсов с учетом Nткmin в нашем примере определятся:

Тсч=Тхmin/Nткmin=2/128 мс=15,6 мкс, fсч/Тсч=64,0 кГц.

В предлагаемом способе частота fсч счетных импульсов должна быть равной fсч=2Q·106 Гц. При Q=-3 будет иметь место fсч=125 кГц, при Q=-4 fсч=62,5 кГц. В соответствии с предлагаемым способом задаем значение частоты fсч, округленное в сторону увеличения до ближайшей величины fсч=2Q·106 Гц, которое в данном случае равно fсч=125 кГц (Q=-3, Тсч=8 мкс).

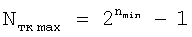

Общее число nmax разрядов счетчика определится следующим образом. При измерении периода Тxmax в счетчике будет получено число Nткmax=Txmax/Tсч=200000/8=25000. Для записи этого числа счетчик должен иметь nmax=15 разрядов.

Преобразователь периода в код с полученными параметрами обеспечит измерение частоты в следующем диапазоне. Так как полная емкость 15-разрядного счетчика равна Nткmax=215-1=32767, то максимальное значение периода измеряемой частоты Tсmax=Nткmax·Tсч=262,1 мс и минимальное значение частоты fcmin=1/Тсmax=3,8 Гц. Максимальное значение диапазона измерения частоты определится:

Txmin=Nткmin·Тсч=128-8 мкс=1024 мкс; fxmax=1/Тхmin=977 Гц.

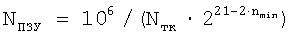

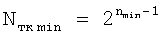

Уравнение для определения записываемых в ПЗУ чисел NПЗУ, приведенное в формуле изобретения, получим следующим образом. Пусть определено значение nmin и дано fсч=106 Гц. Тогда емкость разряда nmin счетчика равна  а максимальная емкость счетчика с nmin разрядами равна

а максимальная емкость счетчика с nmin разрядами равна  (табл.1). Запись «1» в разряд nmin счетчика равнозначна подаче на вход счетчика импульсов с частотой fc, равной:

(табл.1). Запись «1» в разряд nmin счетчика равнозначна подаче на вход счетчика импульсов с частотой fc, равной:

fсmax=1/Tcmin=1/(Nткmin·Тсч)=fсч/Nткmin.

Записанному в счетчик числу Nткmax соответствует частота fcmin=fcч/Nткmax. Например, при nmin=8 и fсч=106 Гц, имеем:

Nткmin=128, fсmax=106/128 Гц=7812 Гц (поз.1 табл.1),

Nткmax=255, fcmin=106/255 Гц=3922 Гц (поз.2 табл.1).

Таким образом, при записи чисел Nтк, имеющих разрядность nmin и определяющих адреса ячеек ПЗУ, на выходе ПЗУ могут получаться числа fc, существенно отличающиеся по разрядности от nmin. В частности, в рассматриваемом примере для записи чисел fcmax=7812 Гц и fcmin=3922 Гц необходимо иметь 13 разрядов (поз.16 табл.1).

Таких дискретных значений чисел fc будет  (поз.1 и 2 табл.1). В нашем примере их всего 128 и разница между двумя соседними значениями fc будет представлять существенную величину, например Δfc=5208-5181=27 (поз.3 и 4 табл.1).

(поз.1 и 2 табл.1). В нашем примере их всего 128 и разница между двумя соседними значениями fc будет представлять существенную величину, например Δfc=5208-5181=27 (поз.3 и 4 табл.1).

Сохранение на выходе ПЗУ чисел с разрядностью, превышающей nmin, не повышает точность измерения частоты, а усложняет реализацию ПЗУ. Поэтому представляется целесообразным трансформировать записываемые в ПЗУ числа таким образом, чтобы они имели разрядность, равную разрядности адресных чисел Nтк, то есть разрядность nmin.

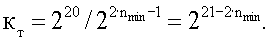

При ориентировочном определении значения коэффициента трансформации кт записываемых в ПЗУ чисел исходим из того, что большему значению fcmax должно соответствовать число Nткmax (коэффициент кт1), или из условия, что меньшему значению fcmin должно соответствовать число Nткmin (коэффициент кт2):

Учитывая, что  , имеем

, имеем

Аналогичным образом получим кт2=кт1=кт.

Принимая fсч=106 Гц≈220 Гц, из выражения для кт1 получим:

При этом значения записываемых в ПЗУ чисел NПЗУ определятся по формуле:

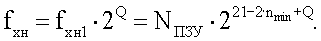

Поэтому при подаче чисел Nтк, получаемых в nmin младших разрядах счетчика  , на адресные входы ПЗУ измеряемая частота определится:

, на адресные входы ПЗУ измеряемая частота определится:

В таблице 1 представлены результаты расчета по приведенным формулам коэффициентов кт1 кт и чисел NПЗУ для предельных значений  и

и  диапазона записи Nтк при величинах nmin, равных 6, 8, 10, 12 и 13.

диапазона записи Nтк при величинах nmin, равных 6, 8, 10, 12 и 13.

Повышение счетной частоты fcч в 2Q раз приводит к такому же увеличению числа NТК в счетчике и понижению частоты fxн1. Для компенсации такого изменения частоты fхн1 в формулу для ее определения введен множитель 2Q:

В формуле и описании изобретения принято значение счетной частоты fсч=106 Гц. В принципе может быть принято другое приемлемое значение счетной частоты. Однако величина fсч=106 Гц имеет преимущество в краткости написания и в удобстве выполнения вычислений.

При подаче чисел Nтк, сформированных в nmin младших разрядах счетчика, на адресные входы ПЗУ (по п.1 формулы изобретения) каждый сдвиг чисел Nтк в сторону младших разрядов увеличивает частоту fc в 2 раза (поз.7, 5 и 1, 8, 6 и 2 табл.1). Ввод в уравнение для fхн множителя 2-m1 позволяет восстановить значение частоты и в результате получаем уравнение, приведенное в п.1 формулы изобретения:

fх1=fхн·2-m1=NПЗУ·2-m1·2с1, где с1=21-2·nmin+Q.

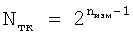

В пункте 2 формулы изобретения предусмотрена подача чисел Nтк, получаемых в nmin старших разрядах счетчика, на адресные входы ПЗУ (табл.2). Запись «1» в разряд nизм счетчика означает, что в счетчик подано  импульсов и возможно это при измерении частоты

импульсов и возможно это при измерении частоты  (поз.1 табл.2). Учитывая, что nизм=nmax-m2 (табл.2), получим:

(поз.1 табл.2). Учитывая, что nизм=nmax-m2 (табл.2), получим:

После сдвига числа Nтк m2 раза в сторону старших разрядов в nmin старших разрядах будет записано число  , то будет восприниматься как подача на вход счетчика сигналов с частотой

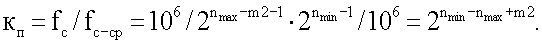

, то будет восприниматься как подача на вход счетчика сигналов с частотой  (поз.2 табл.2). При этом коэффициент пропорциональности кп между этими частотами равен:

(поз.2 табл.2). При этом коэффициент пропорциональности кп между этими частотами равен:

Отсюда следует fc=кп·fc-сp.

С другой стороны, при подаче числа Nтк-ср на адресные входы ПЗУ получим значение частоты

Поэтому при измерении по п.2 формулы изобретения искомая частота определится:

где с2=21-nmax-nmin+Q.

На конкретном примере рассмотрим, как по предлагаемому способу осуществляется измерение частоты. Пусть в условиях приведенного ранее примера, где необходимо было измерять частоту в пределах fx=5÷500 Гц с погрешностью дискретности измерения периода δт≤1% и выяснено, что для этого необходимо иметь счетчик с nmin=8, nmax=15 и частоту счетных импульсов с Q=-3, Тсч=8 мкс, требуется измерить конкретное значение частоты, например fх=100 Гц.

В этом случае приведенные в формуле изобретения зависимости конкретизируются следующим образом:

При fx=100 Гц имеем Tc=l/fc=106/100 мкс=10000 мкс, Nтк=Тс/Тсч=1250=1024+128+64+32+2. Это число разместится в 11 разрядах счетчика (поз.1 табл.3).

При измерении частоты в соответствии с п.1 формулы изобретения число Nтк(15)=1250 будет смещено m1=3 раза в сторону младших разрядов (поз.2 табл.3) и получим новое число Nтк-8=156, для которого в ПЗУ предварительно будет записано число NПЗУ=31250/Nт=31250/156=200. В результате получим fx1=4·NПЗУ·2-m1=4·200·2-3 Гц=100 Гц.

При измерении частоты по п.2 формулы изобретения число Nтк(15)=1250 будет смещено m2=4 раза в сторону старших разрядов (поз.3 табл.3) и получим число Nтк-8=156, затем число NПЗУ=200. В результате определим частоту fx2=1/32-NПЗУ·2m2=1/32·200·24 Гц=100 Гц.

В рассмотренном примере информация о значении измеряемой частоты fx может быть представлена в компактной форме - в виде И-разрядного двоичного числа, 8 разрядов которого представляют собой мантиссу частоты fx, а число к=3 других разрядов - код порядка мантиссы. Так, например, при измерении частоты fx в соответствии с п.2 формулы изобретения будет сформировано в качестве мантиссы двоичное число NПЗУ=200, а в качестве кода порядка - число m2=4.

Коэффициент 1/32 в выражении для fх2 означает, что число NПЗУ=200 должно быть разделено на 32 (1/32=2-5=2r), то есть сдвинуто на r=5 разрядов в сторону младших разрядов, а полученный коэффициент m2=4 требует сдвига числа NПЗУ=200 на 4 разряда в сторону старших разрядов.

Информация о величине NПЗУ и m2 в виде 11-разрядного слова может быть передана в систему телеметрии или в микропроцессорную систему контроля и управления исследуемым объектом, где априори известно значение r=5 и простым смещением кода мантиссы на r-m2=5-4=1 разряд в сторону младших разрядов будет восстановлена естественная форма записи числа fx2.

В состав предлагаемого устройства для измерения частоты входят (фиг.2): формирователь 1 импульсов, блок 2 управления, генератор 3 образцовой частоты, блок 4 счета импульсов образцовой частоты, регистр 5 сдвига, ПЗУ 6, счетчик 7 числа сдвигов кода, формирователь 8 сигнала «Готовность» и буферный регистр 9, причем вход 10 устройства соединен через формирователь 1 импульсов с первым входом блока 2 управления, третий вход которого подключен к первому выходу генератора 3 образцовой частоты, второй выход этого генератора соединен с первым входом блока 4 счета импульсов образцовой частоты, второй вход которого подключен к первому выходу блока 2 управления, третий вход - к второму выходу блока 2 управления, а выход данных подключен шиной к входу данных регистра 5 сдвига, выход формирователя 8 сигнала «Готовность» соединен с одноименным выходом устройства, входы адреса ПЗУ 6 соединены шиной с выходами nmin старших разрядов регистра 5 сдвига, вход данных которого подключен к выходу 11 «Код периода» устройства, старший разряд выхода данных регистра 5 сдвига соединен с четвертым входом блока 2 управления, второй вход которого подключен к второму выходу генератора 3 образцовой частоты, а третий, четвертый и пятый выходы блока 2 управления подключены соответственно к двум входам выбора режима и тактовому входу регистра 5 сдвига, выход данных ПЗУ 6 соединен шиной с первым входом данных буферного регистра 9, второй вход данных которого подключен шиной к выходу данных счетчика 7 числа сдвигов кода, третий вход - к восьмому выходу блока 2 управления, четвертый вход - к входу 13 «Считывание» устройства, а выход данных буферного регистра 9 подключен шиной к выходу 12 данных устройства, седьмой выход блока управления 2 соединен с входом обнуления счетчика 7 числа сдвигов кода, тактовый вход которого подключен к шестому выходу блока 2 управления, девятый выход блока 2 управления соединен с первым входом формирователя 8 сигнала «Готовность», второй вход которого подключен к десятому выходу блока 2 управления.

Кроме того, в соответствии с п.4. формулы изобретения во втором варианте предлагаемого устройства входы адреса ПЗУ 6 соединены шиной с выходами nmin младших (вместо старших по п.3) разрядов регистра 5 сдвига и в него введен элемент ИЛИ-НЕ, входы которого подключены к Δn=nmax-nmin старшим разрядам регистра 5 сдвига, кроме того, в нем четвертый вход блока 2 управления отключен от старшего разряда регистра 5 сдвига и подключен к выходу элемента ИЛИ-НЕ (на блок-схеме фиг.2 элемент ИЛИ-НЕ и его связи не показаны).

Предлагаемое устройство работает следующим образом (фиг.3). Генератор 3 со своего первого выхода непрерывно выдает импульсы fсч, а со второго выхода - инвертированные импульсы  . Формирователь 1 из поступающих на вход 10 устройства сигналов вырабатывает импульсы fx(1), которые подаются на первый вход блока 2 управления. С приходом каждого такого импульса происходит обнуление триггера 2-1 и счетчика-дешифратора 2-2. После окончания каждого импульса fx(l) и следующего за ним импульса

. Формирователь 1 из поступающих на вход 10 устройства сигналов вырабатывает импульсы fx(1), которые подаются на первый вход блока 2 управления. С приходом каждого такого импульса происходит обнуление триггера 2-1 и счетчика-дешифратора 2-2. После окончания каждого импульса fx(l) и следующего за ним импульса  генератора 3 на переднем фронте импульсов fсч этого генератора счетчик-дешифратор 2-2 вырабатывает такты управления T1÷T(L+2).

генератора 3 на переднем фронте импульсов fсч этого генератора счетчик-дешифратор 2-2 вырабатывает такты управления T1÷T(L+2).

Для упрощения описания далее рассматривается работа конкретного варианта предлагаемого устройства, приведенного ранее в примере, где nmin=8, nmax=15, fх=100 Гц, Nтк=1250 и производился сдвиг кода Nтк в сторону старших разрядов (поз.1 и 3 табл.3). При этом с целью компактного и наглядного представления временных диаграмм упомянутые такты управления на фиг.3 изображены на одной временной оси на двух чередующихся уровнях ординаты. В рассматриваемом варианте устройства таких тактов всего 13: Т0÷Т12.

На первом такте Т1 обнуляется триггер 2-3 и сигнал с его выхода запрещает счет импульсов в счетчике 4-1. Последующее включение этого триггера происходит на такте Т4, после чего счет импульсов в счетчике 4-1 возобновляется.

На такте Т2 передается число Nтк из счетчика 4-1 в регистр 5. Для этого из блока 2 управления подаются необходимые сигналы на установочные 5/(2, 3) и синхронизирующий 5/4 входы регистра 5.

На такте Т3 производится начальная установка счетчика 4-1. При этом число «2», равное числу импульсов fсч, не поступивших в счетчик 4-1 из-за запрета счета, передается из установочной шины D(4-3) в счетчик 4-1. Кроме того, на такте Т3 выполняется опрос состояния старшего разряда D2/CP регистра 5 сдвига.

Если в этом разряде записан «0», то сигнал с его выхода, пройдя через инвертор 2-8, поступит на третий вход элемента И 2-6 в качестве открывающего напряжения. При этом положительный импульс fсч, пройдя через элементы И 2-6 и ИЛИ-НЕ 2-7, будет подан в виде отрицательного импульса на тактовый вход 4 регистра 5 сдвига. На заднем фронте этого импульса произойдет сдвиг кода числа Nтк, записанного в регистре 5.

Такой сдвиг кода в регистре 5 будет повторяться и на следующих тактах управления до тех пор, пока на такте Т6 в старшем разряде регистра 5 не появится «1». В этом случае с выхода D2/CP старшего разряда регистра 5 через инвертор 2-8 на вход схемы И 2-6 будет подан запрещающий сигнал и сдвиг кода в регистре 5 на такте Т7 и на всех последующих тактах не будет производиться.

Одновременно с выполнением сдвигов кода в устройстве осуществляется счет числа произведенных сдвигов. Для этого импульсы с выхода элемента И 2-6 подаются на тактовый вход счетчика 7, где фиксируется их количество.

После окончания сдвигов кода с выхода регистра 5 на вход ПЗУ 6 подается число Nтк, определяющее адрес ячейки ПЗУ 6, в которой хранится требуемое число NПЗУ.

На такте Т10 с выхода формирователя 8 будет снят сигнал «Готовность». На следующем такте Т11 произойдет передача числа NПЗУ с выхода ПЗУ 6 и числа m2 со счетчика 7 в буферный регистр 9. На последнем такте Т12 происходит восстановление сигнала «Готовность» и блокировка работы счетчика-дешифратора 2-2.

С приходом каждого очередного сигнала fx(l) цикл измерения частоты повторяется.

В предлагаемом устройстве информация о полученном значении частоты передается из буферного регистра 9 по шине 12 во внешнюю систему при поступлении на вход 13 устройства сигнала «Считывание» RD.

Рассмотренный вариант реализации предлагаемого устройства предусматривает сдвиги кода числа Nтк в сторону старших разрядов (по п.3 формулы изобретения) до тех пор, пока в старшем разряде D2/CP регистра 5 не будет записана «1».

В варианте реализации устройства, в котором выполняется сдвиг кода числа Nтк в сторону младших разрядов (по п.4 формулы изобретения), сдвиги кода в регистре 5 выполняются до появления записи «0» во всех (nmax-nmin) старших разрядах регистра 5. Признаком такого состояния регистра 5 является наличие «1» на выходе вновь введенного элемента ИЛИ-НЕ (вместо наличия «1» на выходе старшего разряда регистра 5 в устройстве по п.3 формулы). Этот вариант реализации предлагаемого устройства незначительно сложнее по составу (он имеет дополнительный элемент ИЛИ-НЕ).

Выбор варианта реализации устройства в конечном счете определяется требованиями по его схемной минимизации при заданной элементной базе.

Предлагаемые способ и устройство измерения частоты позволяют дополнительно осуществлять быстродействующий (в течение периода Тх) пороговый (допусковый) контроль частоты. При этом в процессе преобразования каждого периода Тх в код получаемые в счетчике числа Nт должны сравниваться с заданными пороговыми величинами fпорj=2Q·106/fпорj, где fпорj - пороговые значения частоты, j - число порогов, и в соответствии с алгоритмом контроля частоты смогут формироваться управляющие сигналы.

Для этой цели в предлагаемом устройстве (фиг.2) имеется выходная шина 11 «Код периода», по которой информация о числе Nn может непрерывно передаваться во внешний блок обработки кода (на фиг.2 не показан). В этом блоке текущие значения числа NT будут сравниваться с заданными порогами и по результатам сравнения сформируются управляющие сигналы.

Один из таких блоков применен в устройстве [7], в котором алгоритм порогового контроля частоты реализован аппаратно. В состав блока обработки кода входят дешифратор 7, триггеры 8-10, 24, пороговые накопители 20-22, формирователь выходных команд 25 и логические элементы ИЛИ и И. Дешифратор 7 вырабатывает на заданных пороговых уровнях NT импульсы, которые управляют состоянием триггеров, а те, в свою очередь, посредством схем И управляют работой пороговых накопителей, определяющих состояние формирователя 25 выходных команд.

Предлагаемое устройство для измерения частоты может быть выполнено на серийно выпускаемых интегральных микросхемах. Так, например, формирователь 1 может быть реализован на компараторе 521САЗ бКО.347.015ТУ2, блок 2 - на счетчике-дешифраторе 564ИЕ9 бКО.347.064ТУ или на счетчике 1554ИЕ10 и дешифраторе 1554ИД7 АЕЯР.431.200.093ТУ и логических элементах серии 564 или 1554, генератор 3 - на кварцевом генераторе ГК56-П АФТП.433.520.004ТУ, блок 4 - на счетчике 1554ИЕ10 и других элементах этой серии, регистр 5 - на регистре сдвига 1533ИР13, ПЗУ 6 - на однократно программируемой микросхеме 541РТ2 6КО.347.236-05ТУ, счетчик 7 и формирователь 8 - соответственно на счетчике 1554ИЕ10 и триггере 1554ТМ2, регистр 9 - на буферном регистре 1533ИР33.

Возможны также варианты реализации предлагаемого устройства для измерения частоты на микросхеме одного из базовых матричных кристаллов, например, на Н1537ХМ1 бКО.347.551ТУ, или на программируемой логической интегральной схеме (ПЛИС), например, на ПЛИС серии Spartan-II XC2S100 фирмы «XILINX» и конфигурационном постоянном запоминающем устройстве ХС1700 этой же фирмы.

Таким образом, предлагаемый способ измерения частоты и устройство для его осуществления позволяют:

1. Существенно упростить процесс преобразования кода периода Nтк в код частоты NПЗУ, что достигнуто применением ПЗУ.

2. Получить компактную форму передачи информации, представляющую собой мантиссу с числом nmin двоичных разрядов, обеспечивающих требуемую точность измерения, и двоичный код порядка значения частоты. Причем эта форма позволяет сократить количество разрядов в значении частоты, а также обеспечивает простое преобразование (путем сдвига кода NПЗУ) чисел из компактной формы в обычную форму двоичного числа.

3. Освободить микропроцессорную систему от сложных вычислений гиперболической функции NПЗУ=к/Nтк. При этом микропроцессорная система может быть применена для решения задач более высокого уровня, например, в многоканальной системе она может осуществлять контроль состояния объекта с учетом корреляционных связей измеряемых параметров, управлять работой исследуемого объекта.

4. Реализовать на их основе быстродействующий (в течение периода Тх) пороговый (допусковый) контроль частоты.

В итоге предлагаемый способ измерения частоты и устройство для его осуществления позволяют реализовать быстродействующие непрерывные измерение и контроль частоты с повышенной надежностью.

Выполненные по этому способу устройства в виде модулей могут быть включены в состав систем измерения, управления и аварийной защиты различных объектов повышенного быстродействия, таких, например, как газотурбинные авиационные двигатели [8]. При этом существенно повысится эффективность систем аварийной защиты, что позволит защитить от разрушения исследуемые объекты и испытательные стенды и в итоге значительно снизить затраты на создание изделий новой техники.

СПИСОК ЛИТЕРАТУРЫ.

1. Патент RU N2.173.857, МПК7 G01R 23/00, опубл. 20.09.2001.

2. Патент RU N2.300.112 С2, МПК G01R 23/10, опубл. 27.05.2007.

3. Орнадский П.П. Автоматические измерения и приборы. Киев: «Вища школа», 1973 г., стр.404, 405.

4. Гитис Э.И., Пискунов Е.А. Аналого-цифровые преобразователи. М.: Энергоиздат, 1981 г., стр.165, 166.

5. Патент RU N2.097.774, МПК6 G01R 23/00, опубл. 27.11.1997.

6. Патент RU N2.178.908, МПК7 G04F 10/04, опубл. 27.01.2002.

7. Авторское свидетельство SU 1677639 А1, МПК5 G01Р 3/48, опубл. 15.09.91.

8. Севрюгин Н.Н., Потапов И.А., Попов А.Н., Цирихов A.M. Опыт автоматизации процесса испытаний авиационных газотурбинных двигателей. // Приборы и Системы. Управление, контроль, диагностика. 2001, №5.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| Способ измерения частоты | 2024 |

|

RU2832003C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ СИГНАЛА | 2011 |

|

RU2478213C2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2352059C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2353052C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2352057C1 |

| СПОСОБ ФОРМИРОВАНИЯ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2010 |

|

RU2439791C1 |

| Цифровой фазометр | 1983 |

|

SU1187100A2 |

| СПОСОБ ФОРМИРОВАНИЯ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2352058C1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА К ЭЛЕКТРОМАГНИТНОМУ МНОГОЧАСТОТНОМУ СТРУКТУРОСКОПУ | 1999 |

|

RU2178945C2 |

Заявленная группа изобретений относится к контрольно-измерительной технике и может быть использована в системах автоматического измерения, регулирования и аварийной защиты. Устройство для измерения частоты содержит: формирователь импульсов, блок управления, генератор образцовой частоты, блок счета импульсов образцовой частоты, формирователь сигнала «Готовность», счетчик числа сдвигов кода, буферный регистр, регистр сдвига, постоянное запоминающее устройство. Особенностью заявленного способа измерения частоты является то, что задают значение частоты fсч, округленное в сторону увеличения до ближайшей величины fcч=2Q·106 Гц. Подают числа Nтк, получаемые после окончания измерения периода Тх в nmin младших или старших разрядах счетчика, на адресные входы ПЗУ. При предварительной записи в ПЗУ для каждого значения Nтк в диапазоне от  до

до  определяют значения чисел NПЗУ. При выполнении условия nmin<nизм≤nmах, nизм=nmin+m1 или nmin≤nизм<nmах, nизм=nmах-m2 производят m1 или m2 раз сдвиг числа Nтк в сторону младших или старших разрядов. Запоминают число m1 или m2 проведенных сдвигов и определяют частоту fx1 или fx2 исследуемых сигналов. Техническим результатом группы изобретений является повышение надежности и точности измерения частоты. 4 н.п. ф-лы, 3 ил, 3 табл.

определяют значения чисел NПЗУ. При выполнении условия nmin<nизм≤nmах, nизм=nmin+m1 или nmin≤nизм<nmах, nизм=nmах-m2 производят m1 или m2 раз сдвиг числа Nтк в сторону младших или старших разрядов. Запоминают число m1 или m2 проведенных сдвигов и определяют частоту fx1 или fx2 исследуемых сигналов. Техническим результатом группы изобретений является повышение надежности и точности измерения частоты. 4 н.п. ф-лы, 3 ил, 3 табл.

1. Способ измерения частоты, заключающийся в измерении длительности периода Тх следования сигналов и в последующем определении частоты fx как величины, обратной измеренному периоду, причем для измерения периода Тх используют двоичный счетчик, в котором в процессе измерения каждого периода Тх в диапазоне от Txmin до Тхmах получают соответствующие числа Nт, предварительно определяют число nmin младших разрядов этого счетчика, обеспечивающих измерение минимального периода Txmin с погрешностью дискретности, не превышающей допустимого значения δт, определяют частоту fсч заполнения счетчика с учетом величины Txmin и числа Nткmin, получаемого в счетчике при измерении Txmin, определяют общее число nmах разрядов счетчика исходя из величины максимального периода Тхmах измеряемой частоты, отличающийся тем, что задают значение частоты fсч, округленное в сторону увеличения до ближайшей величины fcч=2Q·106 Гц, где Q - целое положительное или отрицательное число, подают числа Nтк, получаемые после окончания измерения периода Тх в nmin младших разрядах счетчика, на адресные входы постоянного запоминающего устройства (ПЗУ), в ячейках памяти которого хранятся предварительно записанные числа NПЗУ, пропорциональные соответствующим значениям fс частоты сигналов, причем при предварительной записи в ПЗУ для каждого значения Nтк в диапазоне от  до

до  определяют значения чисел NПЗУ:

определяют значения чисел NПЗУ:

,

,

при измерении частоты, величина Nтк периода которой занимает nmin младших разрядов счетчика и отвечает условию  , частоту исследуемых сигналов определяют по формуле:

, частоту исследуемых сигналов определяют по формуле:

fxн=NПЗУ·2с1, где c1=21-2·nmin+Q,

при измерении частоты, величина Nтк периода которой занимает число nизм младших разрядов счетчика и при этом выполняются условия nmin<nизм≤nmах, nизм=nmin+m1, производят m1 раз сдвиг числа Nтк в сторону младших разрядов, запоминают число m1 проведенных сдвигов и определяют частоту fx1 исследуемых сигналов по формуле:

fх1=fхн·2-m1=NПЗУ·2-m1·2c1.

2. Способ измерения частоты, заключающийся в измерении длительности периода Тх следования сигналов и в последующем определении частоты fx как величины, обратной измеренному периоду, причем для измерения периода Тх используют двоичный счетчик, в котором в процессе измерения каждого периода Тх в диапазоне от Txmin до Тхmах получают соответствующие числа Nт, предварительно определяют число nmin младших разрядов этого счетчика, обеспечивающих измерение минимального периода Txmin с погрешностью дискретности, не превышающей допустимого значения δт, определяют частоту fсч заполнения счетчика с учетом величины Txmin и числа Nткmin, получаемого в счетчике при измерении Txmin, определяют общее число nmах разрядов счетчика исходя из величины максимального периода Тхmах измеряемой частоты, отличающийся тем, что задают значение частоты fcч, округленное в сторону увеличения до ближайшей величины fcч=2Q·106 Гц, где Q - целое положительное или отрицательное число, подают числа Nтк, получаемые после окончания измерения периода Тх в nmin старших разрядах счетчика, на адресные входы ПЗУ, в ячейках памяти которого хранятся предварительно записанные числа NПЗУ, пропорциональные соответствующим значениям fc частоты сигналов, причем при предварительной записи в ПЗУ для каждого значения Nтк в диапазоне от  до

до  определяют значения чисел NПЗУ:

определяют значения чисел NПЗУ:

,

,

при измерении частоты, величина Nтк периода которой занимает число nизм младших разрядов счетчика и при этом выполняются условия nmin≤nизм<nmах, nизм=nmах-m2, производят m2 раз сдвиг числа Nтк в сторону старших разрядов, запоминают число m2 проведенных сдвигов и определяют частоту fx2 исследуемых сигналов по формуле:

fx2=NПЗУ·2m2·2c2, где с2=21-nmax-nmin+Q.

3. Устройство для измерения частоты, содержащее формирователь импульсов, блок управления, генератор образцовой частоты, блок счета импульсов образцовой частоты, регистр и формирователь сигнала «Готовность», причем вход устройства соединен через формирователь импульсов с первым входом блока управления, третий вход которого подключен к первому выходу генератора образцовой частоты, второй выход этого генератора соединен с первым входом блока счета импульсов образцовой частоты, второй вход которого подключен к первому выходу блока управления, третий вход - к второму выходу блока управления, а выход данных подключен шиной к входу данных регистра, выход формирователя сигнала «Готовность» соединен с одноименным выходом устройства, при этом в состав блока счета импульсов образцовой частоты входит двоичный счетчик, количество nmin разрядов которого определяется значением δт допустимой погрешности дискретности измерения минимального Txmin периода, а общее число nmах разрядов этого счетчика задается исходя из величины максимального периода Тхmах измеряемой частоты, отличающееся тем, что в него введены постоянное запоминающее устройство, счетчик числа сдвигов кода и буферный регистр, а вместо регистра применен регистр сдвига, причем входы адреса ПЗУ соединены шиной с выходами nmin старших разрядов регистра сдвига, вход данных которого подключен к выходу «Код периода» устройства, старший разряд выхода данных регистра сдвига соединен с четвертым входом блока управления, второй вход которого подключен к второму выходу генератора образцовой частоты, а третий, четвертый и пятый выходы блока управления подключены соответственно к двум входам выбора режима и тактовому входу регистра сдвига, выход данных ПЗУ соединен шиной с первым входом данных буферного регистра, второй вход данных которого подключен шиной к выходу данных счетчика числа сдвигов кода, третий вход - к восьмому выходу блока управления, четвертый вход - к входу «Считывание» устройства, а выход данных буферного регистра подключен шиной к выходу данных устройства, седьмой выход блока управления соединен с входом обнуления счетчика числа сдвигов кода, тактовый вход которого подключен к шестому выходу блока управления, девятый выход блока управления соединен с первым входом формирователя сигнала «Готовность», второй вход которого подключен к десятому выходу блока управления.

4. Устройство для измерения частоты, содержащее формирователь импульсов, блок управления, генератор образцовой частоты, блок счета импульсов образцовой частоты, регистр и формирователь сигнала «Готовность», причем вход устройства соединен через формирователь импульсов с первым входом блока управления, третий вход которого подключен к первому выходу генератора образцовой частоты, второй выход этого генератора соединен с первым входом блока счета импульсов образцовой частоты, второй вход которого подключен к первому выходу блока управления, третий вход - к второму выходу блока управления, а выход данных подключен шиной к входу данных регистра, выход формирователя сигнала «Готовность» соединен с одноименным выходом устройства, при этом в состав блока счета импульсов образцовой частоты входит двоичный счетчик, количество nmin разрядов которого определяется значением δт допустимой погрешности дискретности измерения минимального Тхmin периода, а общее число nmах разрядов этого счетчика задается исходя из величины максимального периода Тхmах измеряемой частоты, отличающееся тем, что в него введены постоянное запоминающее устройство, счетчик числа сдвигов кода, буферный регистр и элемент ИЛИ-НЕ, а вместо регистра применен регистр сдвига, причем входы адреса ПЗУ соединены шиной с выходами nmin младших разрядов регистра сдвига, вход данных которого подключен к выходу «Код периода» устройства, второй вход блока управления подключен к второму выходу генератора образцовой частоты, а третий, четвертый и пятый выходы блока управления подключены соответственно к двум входам выбора режима и тактовому входу регистра сдвига, выход данных ПЗУ соединен шиной с первым входом данных буферного регистра, второй вход данных которого подключен шиной к выходу данных счетчика числа сдвигов кода, третий вход - к восьмому выходу блока управления, четвертый вход - к входу «Считывание» устройства, а выход данных буферного регистра подключен шиной к выходу данных устройства, седьмой выход блока управления соединен с входом обнуления счетчика числа сдвигов кода, тактовый вход которого подключен к шестому выходу блока управления, девятый выход блока управления соединен с первым входом формирователя сигнала «Готовность», второй вход которого подключен к десятому выходу блока управления, входы элемента ИЛИ-НЕ подключены к Δn=nmax-nmin старшим разрядам регистра сдвига, четвертый вход блока управления подключен к выходу элемента ИЛИ-НЕ.

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДА В КОД | 2000 |

|

RU2178908C1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| ОРНАДСКИЙ П.П | |||

| Автоматические измерения и приборы | |||

| - Киев: Вища школа, 1973, с.404, 405 | |||

| ГИТИС Э.И., ПИСКУНОВ Е.А | |||

| Аналого-цифровые преобразователи | |||

| - М.: Энергоиздат, 1981, с.165, 166 | |||

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2173857C1 |

| Сигнализатор предельных значений частоты вращения | 1989 |

|

SU1677639A1 |

Авторы

Даты

2010-10-20—Публикация

2008-12-15—Подача