1

; Изобретение относится к устройст вам импульсной техники и может быть использовано при построении измерительных приборов и узлов цифровой вычислительной техники.

Известен двоичный счетчик, содержащий счетных вход и п разрядов, каждый из которых содержит RSтриггер на логических элементах И-НЕ(ИЛИ-НЕ), и три логических элемента И-НЕ(ИЛИ-НЕ), кроме того, празряд содержит четвертый элемент И-НЕ{ИЛИ-НЕ), причем выход первого элемента каждого разряда соединен с S-входом триггера и входом третьего элемента этого разряда, R-входами триггеров и входами первых элементов предшествующих разрядов, выход второго элемента каждого разряда, кроме п-го, соединен со входами первого и третьего элементов последующего разряда, выход второго элемента п-го разряда соединен со входом четвертого элемента пгго разряда, выход третьего элемента каждого разряда соединен со входами первого и второго элементов этого разряда, выход четвертого элемента п-го разряда соединен с R-входами триггеров и входами первых элементов всех разрядов.

а счетный вход соединен со входами первых элементов всех разрядов и четвертого элемента п-го разряда l. Недостатком этого двоичного счетчика является сравнительно низкое быстродействие.

Известен также N-разрядный двоичный счетчик, содержащий N RS-триггеров, многоустойчивый элемент и

10 дополнительных элементов И-НЕ(ИЛИ-НЕ), каждый RS-триггер содержит первый и второй элементы И-НЕ.(ИЛИ-НЕ) , входы которых соединены с выходами соответственно второго и первого элементов И-НЕ(ИЛИ-НЕ) того же RS-триггера, многоустойчивый элемент содержит N-H вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого из которых соединен с

20 входами всех остальных вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого i-oro вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входом первого элемента И-НЕ(ИЛИ-НЕ)

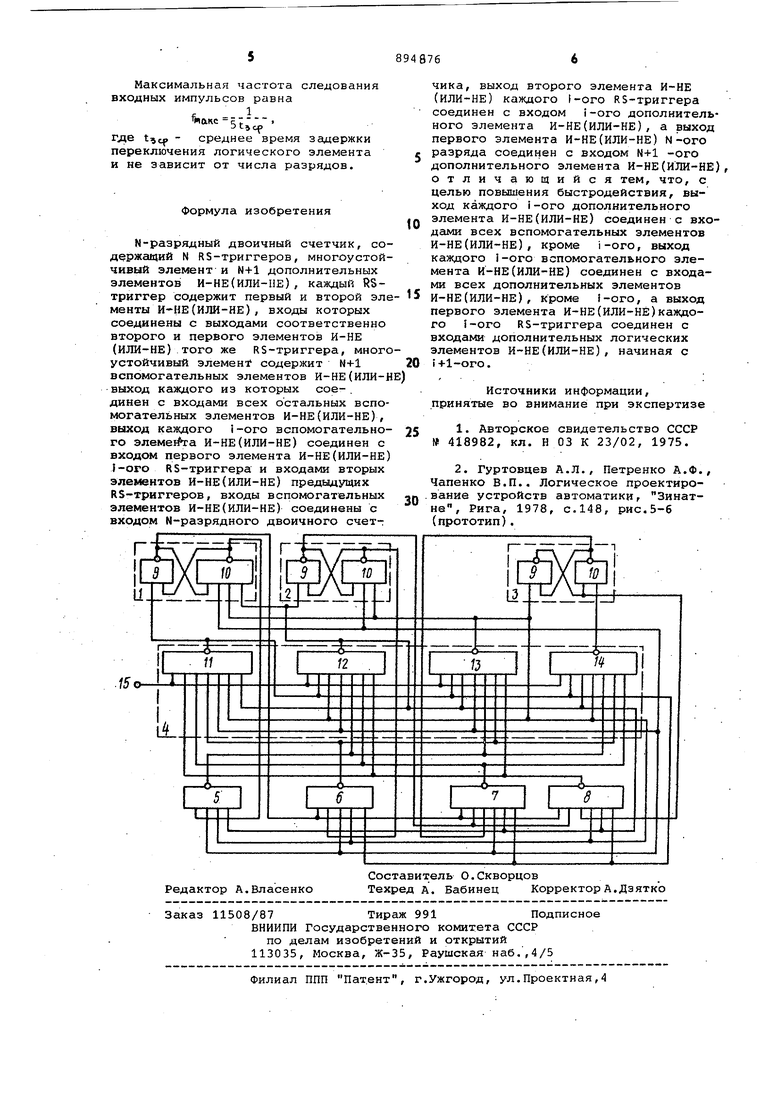

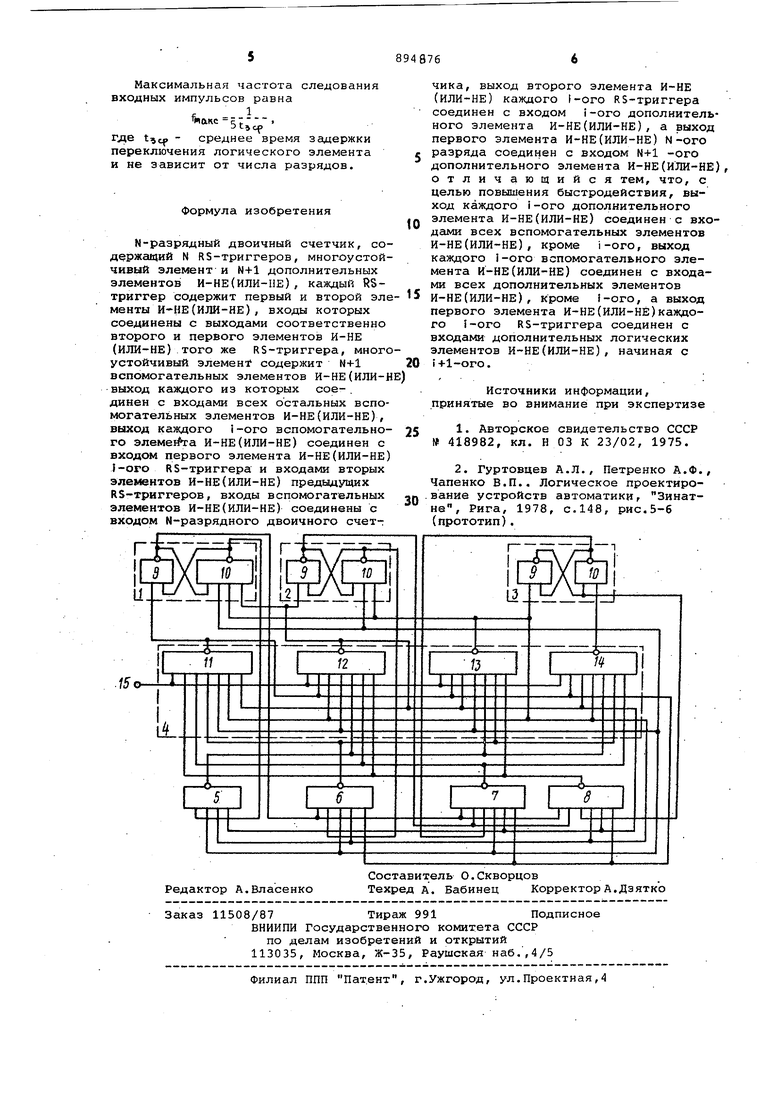

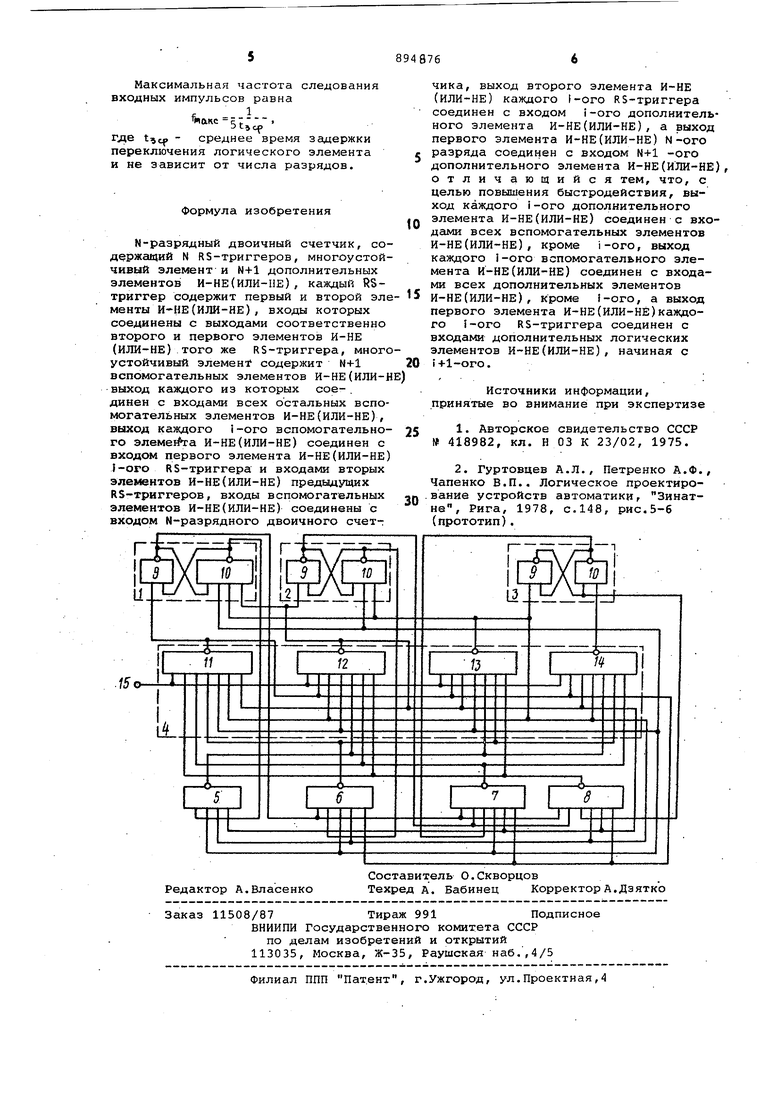

25 i-oro RS-триггера и входами вторых элементов И-НЕ(ИЛИ-НЕ) предьщущих RS-триггеров, входы вспомогательных элементов И-НЕ(ИЛИ-НЕ) соединены с входом N-разрядного двоичного счетчика, выход второго элемента И-НЕ(ИЛИ-НЕ) каждого i-его RS-триггера соединен с входом i-ог дополнительного элемента И-НЕ(ИЛИ-Н а выход первого элемента И-НЕ(ИЛИ-Н N-oro разряда соединен с входом N ого дополнительного элемента И-НЕ(ИЛИ-НЕ)2. Недостатком этого N-разрядного двоичного счетчика является орав-- нительно низкое быстродействие. Цель изобретения - повьзшение быс родействия. Поставленная цель достигается те что в N-разрядном двоичном счетчике содержащем N RS-триггеров, многоустойчивый элемент и Nd-1 дополнител ных элементов И-НЕ (ИЛИ-НК), каждый RS-триггер содержит первый и второй элементы Й-НЕ{ИЛИ-НЕ), входы которы соединены с выходами соответственно второго и первого элементов И-НЕ(ИЛЙ-НЕ) того же RS-триггера, многоустойчивый элемент содержит N 1 вспомогательных элементов И-НЕ{ИЛИ-НЕ), выход каждого из кото рьах соединен с входами всех остальных вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого i-oro вспомогательного элемента И-НЕ(ИЛИсоединен с входом первого элемента И-НЕ(ИЛИ-«Е) i-oro RS-триггера и входами вторых элементов И-НЕ(ИЛИ-Н предыдущих RS-триггеров, входы вспо могательных элементов И-НЕ(ИЛИ-НЕ) соединены с входом М-разрядного , двоичного счетчика, выход второго элемента И-НЕ(ИЛИ-НЕ) каждого 1-ог RS-триггера соединен с входом i-oro дополнительного элемента И-НЕ(ИЛИ-Н а выход первогб элемента И-НЕ(ИЛИ-Н Н-ого разряда соединен с входом N4-1-ого дополнительного элемента И-НЕ(ИЛИ-НЕ), выход каждого i-oro дополнительного элемента И-НЕ(ИЛИ-Н соединен с входами всех вспомогател ных элементов И-НЕ(ИЛИ-НЕ).кроме I -ого,выход каждого i -ого вспомогательного элемента И-НЕ (ИЛИ-НЕ) соединен с вхрдами всех дополнительных элементов Й-НЕ(Ш1И-НЁ),кроме 1-ого, а выход первого элемента И-НЕ(ИЛИ-НЕ) каждого 1-ого RS-триггера соединен с входами дополнительных логических элементов И-НЕ(ИЛИ-НЕ), начиная с . На чертеже показана структурная схема первых трех разрядов N-разрядного двоичного счетчика. Двоичный счетчик содержит RS-три геры 1-3, многоустойчивый элемент 4 и четыре дополнительных элемента 5-8 И-НЕ(ИЛИ-НЕ), каждый Re-триггер содержит первый 9 и второй 10 элеме 5ты И-НЕ (ИЛИ-НЕ) , входы которых соединены с выходами соответственно второго 10 первого 9 элементов И-НЕ(ИЛИ-НЕ)того же RS-триггера, многоустойчивый элемент содержит четыре вспомогательных элемента 1114 И-НЕ(ИЛИ-НЕ), выход каждого из которых соединен с входами всех остальных вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого f-oro вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входом первого элемента И-НЕ(ИЛИ-НЕ)-ого RS-триггера и входами вторых 10 элементов И-НЕ(ИЛИ-НЕ) преднцущих RS-триггеров, входы вспомогательных элементов 11-14 И-НЕ(ИЛИ-НЕ) соединены с входом 15 двоичного счетчика, а выход второго элемента 10 И-НЕ(ЙЛИ-НЕ) каждого i-oro RS-триггера соединен с входом i-oro дополнительного элемента И-НЕ (иЛИ-Нв) а выход первого элемента 9 И-НЕ (ИЛИ-НЕ) последнего разряда соедин.ен с входом посладнего дополнительного элемента И-НЕ(ИЛИ-НЕ), выход каждого i.-roro дополнительного элемента И-НЕ(ИЛИ-НЕ) соединен с входами всех вспомогательных элементов И-НЕ (ИЛИ-НЕ), кроме С-ого, выход каждого i-ого вспомогательного элемента И-НЕ (ИЛИ-НЕ) соединен с входами всех дополнительных элементов И-НЕ(ИЛИ-НЕ), кроме 1-ого, а выход первого элемента И-НЕ(ИЛИ-НЕ) каждого {-ого RS-триггера соединен с входами дополнительных логических элементов И-НЕ(ИЛИ-НЕ), начиная с t-1-ого. Двоичный счетчик работает следующим образом. При состоянии логического нуля на входе 15 в зависимости от состояния RS-триггеров 1,2 или 3 один из элементов 5-8 установлен в нулевое логическое состояние, а все остальные установлены в состояние логической единицы. Так, если элемент 10 И-НЕ() первого RS-триггера установлен в состояние.логического нуля, а в единичное состояние установлен элемент 5 И-НЕ(ИЛИ-НЕ). Фронт счетного импульса на входе 15 вызывает переключение в нулевое логическое состояние одного из элементов 11-14 И-НЁ(ИЛИ-НЕ), после чего происходит перек;яочение RS-триггеров разрядов таким образом, что в единичное состояние устанавливается RS-триггер соответствующего разряда, а все RS-триггеры младших разрядов устанавливгиотся в состояние логического нуля. Затем один из элементов 5-8 И-НЕ(ИЛИ-НЕ) переключается из нулевого логического состояния в единичное. Срез счетного импульса на входе 15 вызывает переключение из состояния логического нуля в состояние логической единицы одного из элементов 11-14 И-НЕ(ИЛИ-НЕ), после чего устанавливается состояние логического нуля на выходе одного из элементов 5-7 или 14 И-НЕ(ИЛИ-НЕ) Дсшее процесс счета повторяется аналогичнЕлм образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1980 |

|

SU892739A1 |

| Счетное устройство | 1981 |

|

SU1023664A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1023335A1 |

| Счетчик импульсов с управляемымКОэффициЕНТОМ пЕРЕСчЕТА | 1979 |

|

SU801257A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Счетчик в коде Грея | 1987 |

|

SU1492474A1 |

| Функциональный генератор | 1981 |

|

SU1010617A1 |

| Реверсивный счетчик | 1979 |

|

SU824449A1 |

| Преобразователь прямого кода в дополнительный | 1977 |

|

SU748406A1 |

Авторы

Даты

1981-12-30—Публикация

1979-12-26—Подача