ну управления, блок управления содержит N{N+1)-входовых элементов И-Н и N i-входовых элементов И-НЕ, выход 1-ого из них соединен с С-входом J 1-ого -К триггера, первый вход - С; шиной тактовых импульсов, а остальные i-1 входы с выходами предыдущих -нх 1-К триггеров (т i); первый

вход i-ого (N+1)-входового элемента И-НЕ соединен с i-ым разрядом шины управления, остальные N входов с выходами всех I-Ктриггеров, а выход с I и К входами i-ого I -К триггера, где i 1,N.

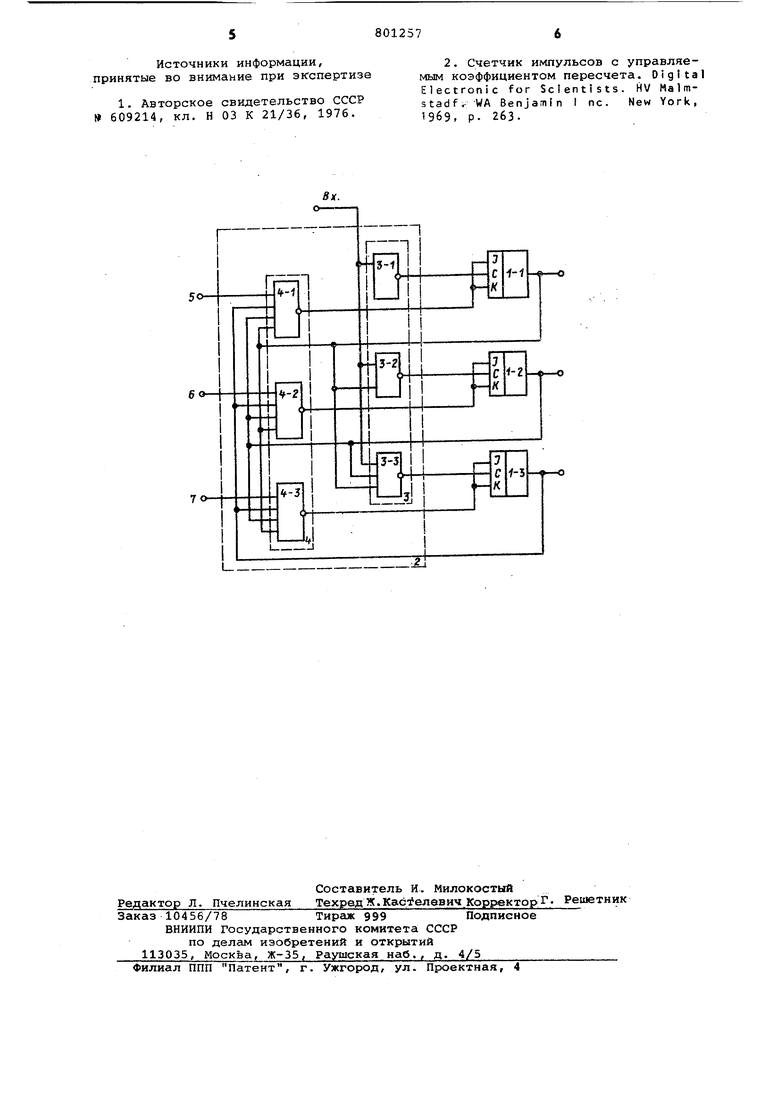

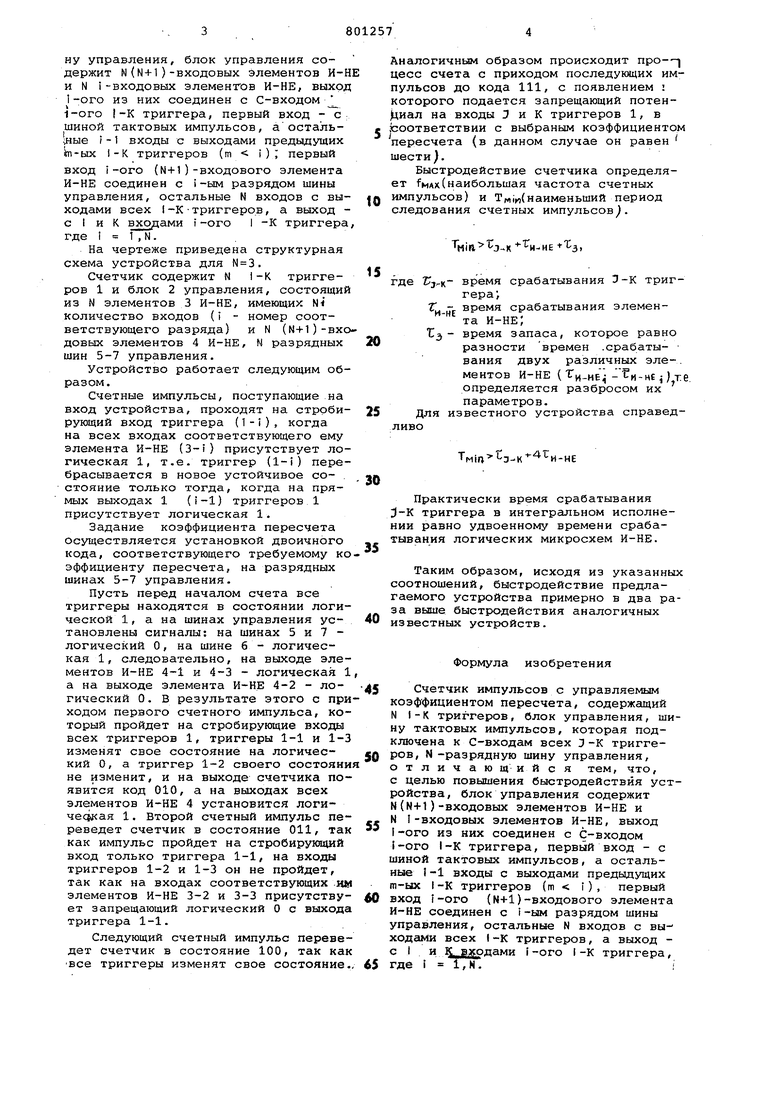

На чертеже приведена структурная схема устройства для .

Счетчик содержит N I-К триггеров 1 и блок 2 управления, состоящий из N элементов 3 И-НЕ, имеющих N количество входов (i - номер соответствующего разряда) и N (N+1)-входовых элементов 4 И-НЕ, N разрядных шин 5-7 управления.

Устройство работает следующим образом.

Счетные импульсы, поступающие на вход устройства, проходят на стррбирующий вход триггера (1 -i), когда на всех входах соответствующего ему элемента И-НЕ (3-i) присутствует логическая 1, т.е. триггер (1-i) перебрасывается в новое устойчивое состояние только тогда, когда на прямых выходах 1 (i-1) триггеров 1 присутствует логическая 1.

Задание коэффициента пересчета осуществляется установкой двоичного кода, соответствующего требуемому коэффициенту пересчета, на разрядных шинах 5-7 управления.

Пусть перед началом счета все триггеры находятся в состоянии логической 1, а на шинах управления установлены сигналы: на шинах 5 и 7 логический О, на шине 6 - логическая 1, следовательно, на выходе элементов И-НЕ 4-1 и 4-3 - логическая 1 а на выходе элемента И-НЕ 4-2 - логический 0. В результате этого с приходом первого счетного импульса, который пройдет на стробирующие входы всех триггеров 1, триггеры 1-1 и 1-3 изменят свое состояние на логический О, а триггер 1-2 своего состояни не изменит, и на выходе счетчика появится код 010, а на выходах всех элементов И-НЕ 4 установится логичесфкая 1. Второй счетный импульс переведет счетчик в состояние 011, так как импульс пройдет на стробирукадий вход только триггера 1-1, на входы триггеров 1-2 и 1-3 он не пройдет, так как на входах соответствующих им элементов И-НЕ 3-2 и 3-3 присутствует запрещающий логический О с выхода триггера 1-1.

Следующий счетный импульс переведет счетчик в состояние 100, так как Все триггеры изменят свое состояние.

Аналогичным образом происходит про--) цесс счета с приходом последующих импульсов до кода 111, с появлением : которого подается запрещающий потенДиал на входы :j и К триггеров 1, в соответствии с выбраным коэффициентом пересчета (в данном случае он равен шести).

Быстродействие счетчика определяет fHAx( наибольшая частота счетных импульсов) и Тм;„(наименьший период следования счетных импульсов.

.

где время срабатывания 3-К триггера;Т.. -, время срабатывания элемен та И-НЕ;

Гз время запаса, которое равно разности времен .срабаты- вания двух различных эле-.

ментов И-НЕ (TH-HE J- Ри-нЕ т определяется разбросом их параметров.

Для известного устройства справедливо

Тм1п э-к и-нЕ

Практически время срабатывания ;J-K триггера в интегральном исполнении равно удвоенному времени срабатывания логических микросхем И-НЕ.

Таким образом, исходя из указанных соотношений, быстродействие предлагаемого устройства примерно в два раза выше быстродействия аналогичных известных устройств.

Формула изобретения

Счетчик импульсов с управляемым коэффициентом пересчета, содержащий N 1-К триггеров, блок управления, шину тактовых импульсов, которая подключена к С-входам всех J-к триггеров, N-разрядную шину управления, отлич ающий с я тем, что, с целью повышения быстродействия устройства, блок управления содержит N(N+1)-входовых элементов И-НЕ и N 1-входовых элементов И-НЕ, выход I-ого из них соединен с С-входом i-oro 1-К триггера, первый вход - с шиной тактовых импульсов, а остальные -1 входы с выходами предыдущих iti-ых 1-К триггеров (т i), первый вход i-oro (N+1)-входового элемента И-НЕ соединен с i-ым разрядом шины управления, остальные N входов с выходс1Ми всех 1 -к триггеров, а выход с I и К.входами i-oro 1-К триггера, где i 1,N.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 609214, кл, Н 03 К 21/36, 1976.

2, Счетчик импульсов с управляемьом коэффициентом пересчета. Digital Electronic for Scientists. HV Malmstadf WA Benjamin I nc. New York, 1969, p. 263.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1072266A1 |

| Устройство для передачи цифровой информации | 1981 |

|

SU980115A1 |

| N-разрядный двоичный счетчик | 1979 |

|

SU894876A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Кольцевой счетчик | 1980 |

|

SU940311A1 |

| Генератор псевдослучайной последовательности | 1979 |

|

SU857984A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU970632A1 |

Авторы

Даты

1981-01-30—Публикация

1979-03-05—Подача