Изобретение относится к вычисли тельной технике и может быть исполь зовано в аппаратуре контроля дискретных устройств.

Известно устройство для параллельного .счета количества единиц ( нулей)в двоичном числе, содержащее входной и выходной регистры, а также EogVj Vi групп сумматоров по V1/2K сумматоров в каждой группе (и - число разрядов кода .), .а также три элемента И, два элемента ИЛИ, элемент НЕ и триггер .режима 1}

Недостатками данного устройства йвляются его невысокое быстродействие, обусловленное тем, что время: задержки в устройстве складывается из времени пробега сигнала суммы вдоль сумматоров первой группы и времени пробега сигнаша переноса вдоль последних сумматоров групп, а также невозможность подсгчета числа единиц в произвольном количестве разрядов.

Наиболее близким к изобретению является устройство для определения количества единиц в двоичном числе, содержащее счетчик, два элемента И., элемент И-НЕ, а в каждом из разрядов два.элемента и, элемент ИЛИ и триггер t2 .

К недостаткам известного устройства относятся: невысокое быстродействие, связанное с тем, что период тактовых импульсов зависит от задержки сигнала управления в разрядных элементах И и ИЛИ, которая составляет величину VI (.pyi+tviAM), (где : п-количество разрядов числа t kfii vtвремя задержки сигнала управления в элементе И и элементе ИЛИ)} отсутствие контроля на четность двоичного числа, а также отсутствие возможности подсчета числа единиц в произвольном количестве разрядов; двоичное число может состоять из операционной (операнд) и вспомогательной (признаки, контрольные разряды, метки и т.д.) частей.. Часто возникает необходимость подсчета числа единиц только в операционной части двоичного числа, т.е. устройство должно обеспечивать два режима работы 1 - подсчет числа единиц во всех разрядах двоичного числа и 2 подсчет числа единиц в оп эеделенных разрядах двоичного числа, причем эти разряды могут быть размещены в числе самым произвольным образом.

Цель изобретения - повышение быстродействия и расширение фунйцнонёшьных возможностей устройства путем контроля на чётность двоичного числа и обеспечения воэмсжности подсчета единиц в произвольном количёс ве разрядов двоичного числа.

Поставленная цель достигается тем, что в устройство для определения количества единиц в двоичном числе , содержащее счетчик, два элемента И, элемент И-НЁ,И разрядных триггеров, Vi разрядных элементов Н, И разрядных элементов ИЛИ, причем первый вход первого элемента И является входом тактовых импульсов устройства, второй вход первого элемента И соединен с первыми входами элемента И-НЕ, второго элемента И, разт рядногоэлемента И первого разряда :и является управляющим входс 1 устройства, второй вход второго элемента И соединен с вторым входом элемента И-тНЕ, выход которого соединен с третьим входом первого элемента И, выход которого соединен с синхронизирующими входами разрядных триггеров и входом счетчика, выходы которого являются информационными выходами устройства, выход второго элемента И является выходом конца счета устройства, единичные выходы разрядных триггеров соединены с первыми входами соответствующих разрядных элементов ИЛИ, выход разрядного элемента ИЛИ i.-го разряда (-1 1тП-1) соединен с первым входом разрядного элемента И (1+1 )-го разряда, вторые входы разрядных элементов И являются группой прямых Входов устройства, введены контрольный, триггер и третий элемент И, причем выход первого элемента И соеди-г нен со счетным входом контрольного триггера, вых.од которого является контрольным выходом устройства, вторые и третьи входы разрядных элементов ИЛИ образуют соответственно группу инверсных входов устройства и группу входов маски устройства, Еиходы разрядных элементов ИЛИ соединены а соответствукячими входами третьего элемента И, выход которого соединен с вторым входом второго элемента И, выход разрядного элемента ИЛИ i-го разряда соединен с соответствующими входами всех последующих разрядных элементов И, начиная с (+ 2) -го разряда.

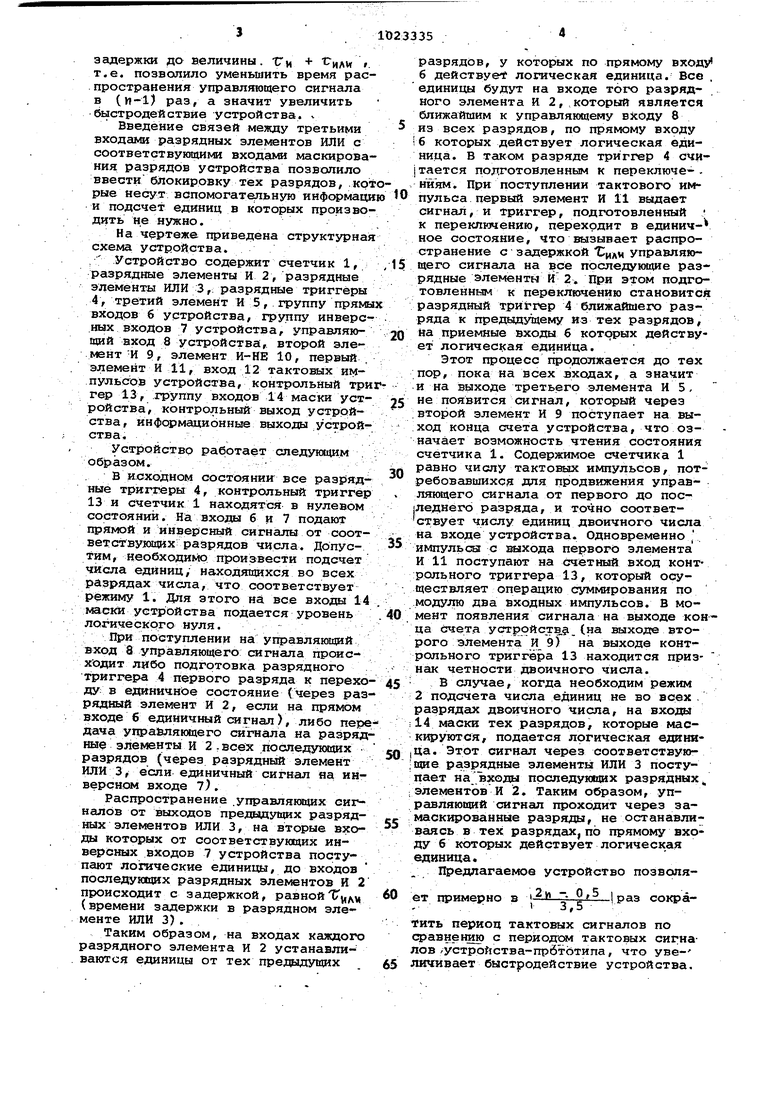

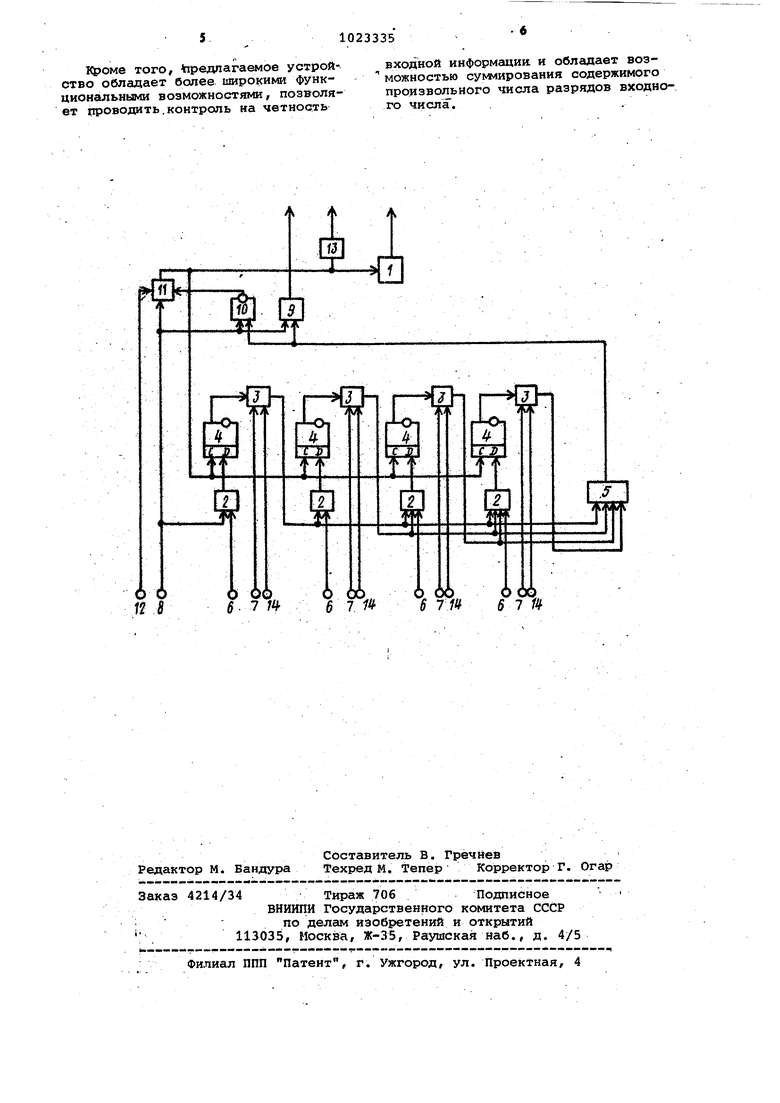

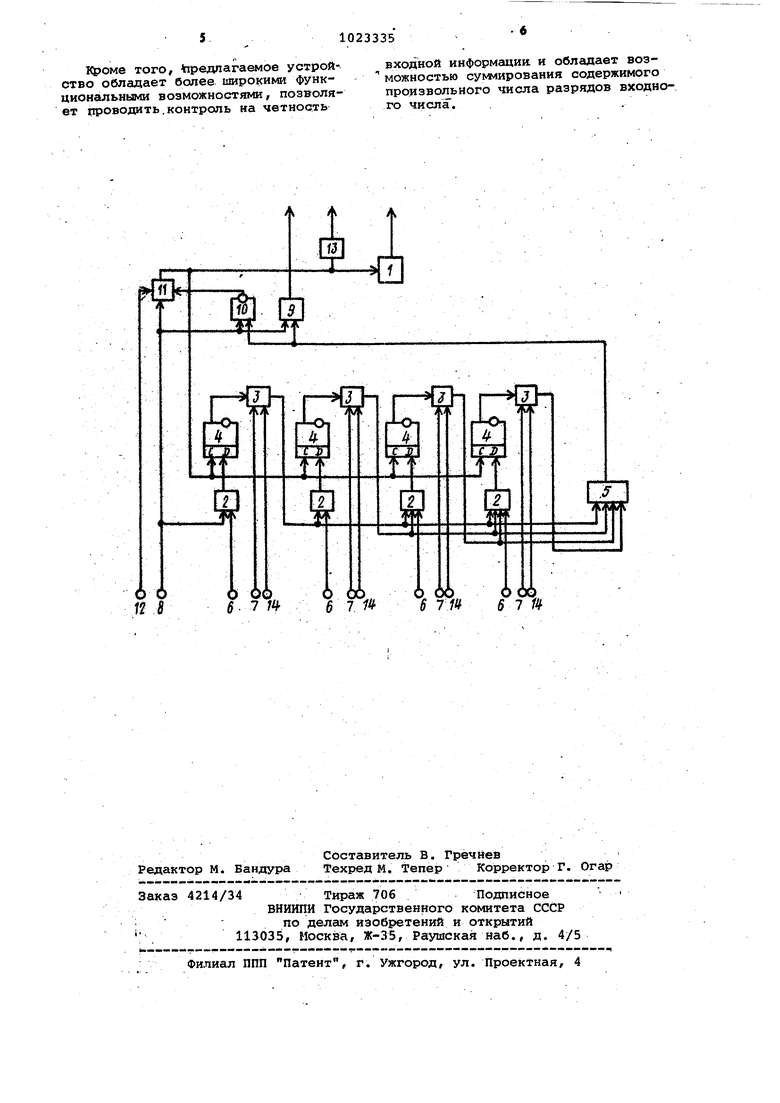

Введение триггера со счетным входом позволяет проводить контроль на четность параллельйо с подсчетом Числа единиц за время, равное количеству тактов по числу единиц в двоичном числе или в его части. Введение; связей между выходами предьщущих разрядных элементов ИЛИ с входами всех последующих разрядных элементов И, а также введение дополнительного элемента И, присоединенного к входам с выходами всех разрядных элементов ИЛИ, а вьОсодом с вторыми входами элементов И-НЕ и второго элемента И позволило организовать цепь параллельного запрета от предыдущих единичных разрядов на последующие, что сократило время задержки до величины. Т и + Силк . т.е. позволило уменьшить время распространения управляющего сигнала в (и-1) раз, а значит увеличить быстродействие устройства, v Введение связей между третьими входами разрядных элементов ИЛИ с соответствующими входами маскирова ния разрядов устройства позволило ввести блокировку тех разрядов, .кррые несут вспомогательную информаци и подсчет единиц в которых производить не нужно. На чертеже приведена структурная схема устройства. / Устройство содержит счетчик 1, разрядные элементы И 2, разрядные элементы ИЛИ 3, разрядные триггеры 4, третий элемент И 5,.группу прямы входов 6 устройства, группу инверсных входов 7 устройства, управляющий вход 8 устройства, второй элемент И 9, элемент И-НЁ 10, первый , элемент И 11, вход 12 тактовых импульсов устройства, контрольный три гер 13, группу входов 14 маски устройства, контрольный выход устррйства, информационные выходы устройства, . - . - . . Устройство работает следующим . об разом. В исходном состоянии все разрядные триггеры 4, контрольный триггер 13 и счетчик 1 находятся в нулевом состояний. На входы б и 7 подают прямой и инверсный сигналы от соответствующих разрядов числа. ДопусТИМ, необходимо произвести подсчет числа единиц, находящихся во всех разрядах числа, что соответствует режиму 1. Для этого на все входы 14 маски устройства подается уровень логического нуля. При поступлении на ущзавляющий вход 8 управляющего сигнала происходит либо подготовка разрядного триггера 4 первого разряда к перехо ду в единичное состояние (через раз рядный элемент И 2, если на прямом входе б единичный сигнал), либо пере дача упраЬляющего сигнала на раэряд ны«е; элементы И 2 .всех йосдедуюиих разрядов (через разрядный элемент ИЛИ 3, если единичный сигнал на инверсном входе 7), Распространение .управляющих сигналов от выходов предыдущих разрядных элементов ИЛИ 3, на вторые входы которых от соответствующих инверсных входов 7 устройства поступают логические единицы, до входов последующих разрядных элементов И 2 происходит с задержкой, равнойСу,ду| (времени задержки в раэрядном элементе ИЛИ 3). Таким образом, на входах каждого разрядного элемента И 2 устанавливаются единицы от тех предыдущих разрядов, у которых по прямому входу 6 действует логическая единица. Все , единицы будут на входе того разрядного элемента и 2, который является ближайшим к управляющему входу 8 из всех разрядов, по прямому входу 6 которых действует логическая единица. В таком разряде триггер 4 считается подготовленным к переключе- . ниям. При поступлении тактового импульса первый элемент И 11 выдает сигнал, и триггер, подготовленный к переключению, перехрдит в единичное состояние, что вызывает распространение с задержкой управляющего сигнала на сё последующие разрядные элементы И 2. При этом подготовленным к переключению становитсА разрядный триггер 4 ближайшего разряда к предыдущему из тех разрядов, на приемные входы б которых действует логическая единица. Этот процесс продолжается до тех пор, пока на всех входах, а значит и на выходе третьего элемента И 5не появится сигнал, который через второй элемент И 9 поступает на выход конца счета устройства, что означает возможность чтения состояния счетчика 1. Содержимое счетчика 1 равно числу тактовых импульсов, потребовавшихся для продвижения управляющего сигнала от первого до пос|Леднег6 разряда, и точно соответстгвует числу единиц двоичного числа на входе устройства. Одновременно , импульсы с выхода первого элемента И 11 поступают на счетный вход контрольного триггера 13, который осуществляет операцию суммирования по модулю два входных импульсов. В момент появления сигнала на выходе кон ца счет.а устройству (на выходе второго элемента И 9) на выходе контрольного триггера 13 находится признак четности двоичного числа. В случае, когда необходим режим 2 подсчета числа единиц не во всех . разрядах двоичного числа, на входы 14 маски тех разрядов, которые масшфуются, подается лргическая единица. Этот сигнал через соответствуюwfie разрядные элементы ИЛИ 3 поступает на Ъходы прследуюидах разрядных элементов И 2, Таким образом, управляющий сигнал проходит через замаскированные разряды, не останавливаясь в тех разрядах, по прямому входу б которых действует логическая единица. Предлагаемое устройство позволя|2и -.0,5 раз сокрает примерно в - 3,5 тить период тактовых сигналов по сравнению с периодом тактовых сигналов /устройства-прбтРтипа, что увеличивает быстродействие устройства.

Кроме того, предлагаемое устройство обладает более широкими функциональными возможностями, позволяет проводить.контроль на четность

входной информации, и обладает возможностью суммирования содержимого произвольного числа разрядов входного числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU997038A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1084797A1 |

| Устройство для определения количества единиц в двоичном числе | 1988 |

|

SU1547072A2 |

| Устройство для подсчета числа нулей в двоичном коде | 1984 |

|

SU1241232A2 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ НЕПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ | 2023 |

|

RU2798197C1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

УСТРОЙСТВО дацЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В ДБОИЧНОМ ЧИСЛЕ, содержшцее счетчик, два элеиданта И, элемент И-НЕ, М разрядных триггеров, h разрядных элементов И, vi разг .рядных элет ентов.ЙЯЙ, причем первый вход первого элемента И является входом тактовых импульсов устройства, второй вход первого элемента И соединен с первыми входами элемента И-НЕ, второго элё;«гнта И, разрядного зЛ&м&та И nepBOtx) разряда и является уп авлякя1щм входом устройства, второй вход второго И соединен с вторым входом элемента И-НЕ, выход которого соединен с третьим входе первого элемента И/ выход которого соединён с синхронизирующими входами разрядных триггеров и входом счетчика, выходы которого явлйются информационньини выходами устройства, выход второго злемента И является выходом конца счета устройства, единичные выходы разрядных триггеров соединены с первьпли I ;входами соответствующих разрядных элементов ИЛИ, выход разрядного элемента ИЛИ i -го разряда ( f n-1) соединен с первым входом разрядного элемента и (± + 1)-го разряда, вторые входа разрядных элементов И являются группой прямых входов устройства, о т л и ч а. ю щ е е с я тем, что, с целью побыиения быстродействия и расширения функциональных возможностей устройства путем контроля на четность двоичного числа и обеспечения возможности подсчета единиц в прризвольном количестве разрядов двоичного числа, в него введены контрольный триг- g .гер и третий элемент И, причем выход первого элемента И соединен со СЛ счетным ВХОДСЯ4 контрольного тригге- т ра, выход которого является контроль тал выходом устройства, вторые и § третьи входы разрядных элементов ИЛИ образуют соответственно группу инверсных входов устройства и группу входов маски устройства, г:1ходы разрядных элементов ИЛИ соединены с соответствующими входами третьего 9Л@4ента И, выход которого соединен Ь9 с вторш входом второго элемента И, СО яахрд разрядного элемента ИЛИ 4-го .разряда соединен с соответствуняцими оэ входами всех последующих разрядных со ел элементов и, начиная с (i +2)-го 5 аряда.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1979 |

|

SU781811A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения количества едениц в двоичном числе | 1977 |

|

SU716041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-15—Публикация

1982-01-20—Подача