Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении арифметических устройств. 5

Известен преобразователь двоичного кода в дополнительный, содержащий триггерный регистр, группу элементов ИЛИ, выходы которых соединены со счетными входами триггеров 10 регистра, группу элементов И, входы которыгг соединены с выходами триггеров регистра, а выходы элементов И соединены со входами элементов ИЛИ ij.

Недостатком известного устройст- 5 ва является относительно невысокое быстродействие и невозможность осуществления наряду с преобразованием в дополнительный код преобразования в обратный код .и передачи в выходной 20 регистр входного кода без преобразования. ,

Наиболее близким к предлагаемому по технической сущности и схемному решению являетсяпреобразователь пря-25 мого кода в дополнительный, содержащий триггерный регистр , п-2 элементов ИЛИ, где п - число разрядов преобразуемого кода, п-2 элементов И, i-тый вход j-ого элемента И 30

(j З-п), (i 1- j-1) соединен с входной шиной - го разряда, первая и вторая группы установочных входов (п-2) разрядов триггерного регистра соединены соответственно с первой и второй группами входов Н

; Кроме того, данный преобразователь содержит вторую труппу элементов И, выходы которых соединены со вторыми установочными йходамй триггеров piafftcTpa: .

Недостатком данного преобразова -, теля является невозможность осуществ ления наряду с преобразованием двоичного кода в дополнительный преобразования в обратный и невозмо йностЬ передачи входного кода без преобразования.

Цель изобретения - расширение функциональных возможностей путем обеспечения преобразования прямого кода в обратный.

Это достигается за счет того, что преобразователь содержит элемент И, элемент И-НЕ, первый и второй элементы ИЛИ и группу из п элементов ИЛИ-НЕ, выходы группы элемен-. тов ИЛИ-НЕ и всех элементов ИЛИ соединены соответственно с первой

ивторой группой входов записи триг герного регистра, первый вход элемента И-НЕ, первые входы элементов ИЛЙ-НЕ и ИЛИ соединены с первой шиной управления, управляющие входьа всех элементов И соединены со iefoрой шиной управления, со вторыми входа.ми элемен та ИЛИ-НЕ младшего разря да группы элементов ИЛИ-НЕ, первого элемента ИЛИ, элемента И-НЕ, выход которого соединен с третьей группой входов триггерного регистра, первый установочный вход первого разряда триггерного регистра соединен с шиной младшего разряда первой группы

входов и с информационным входом

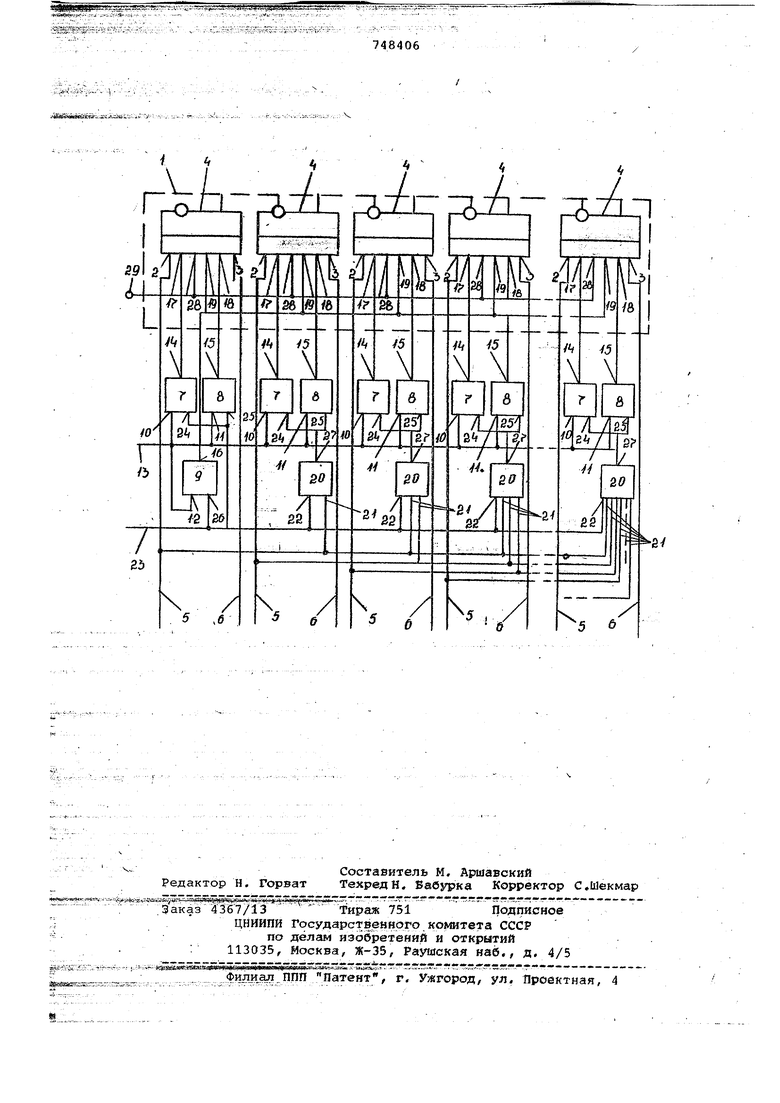

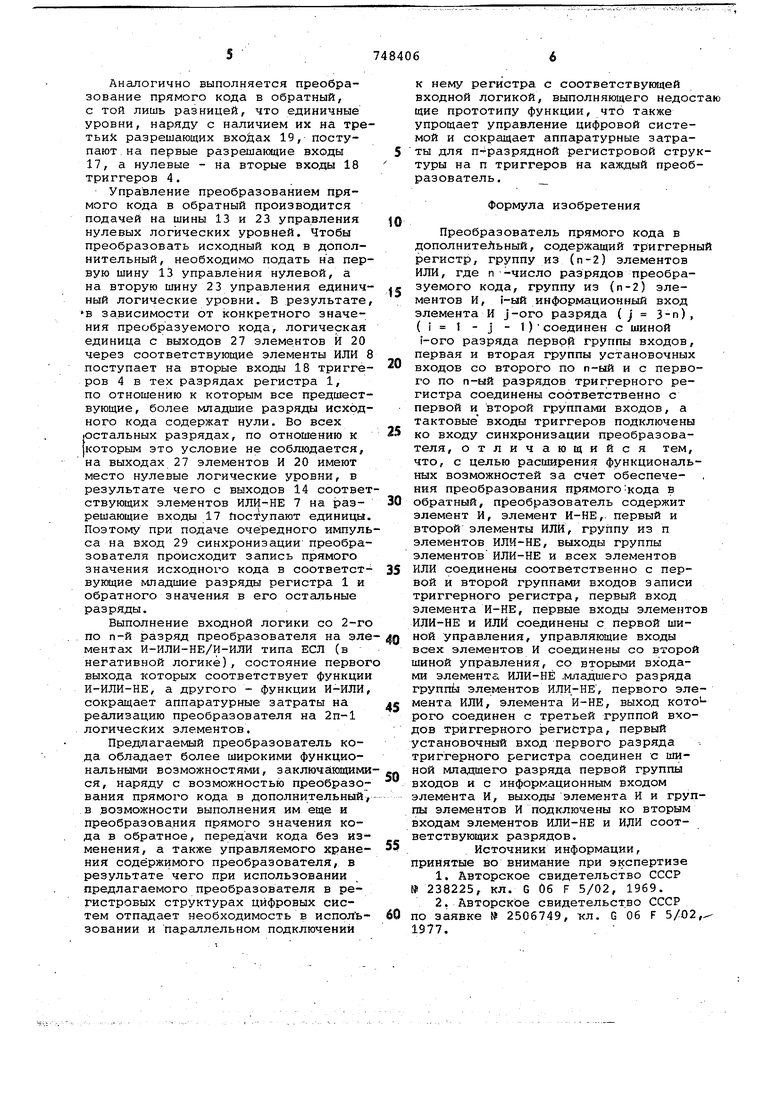

элемента И, выходы элемента И и группы элементов И подключены ко втЪрыМ входам элементов ИЛИ-НЕ и ИЛИ соответствующих разрядов.- На чертеже приведена блок-схема предлагаемого преобразователя,

Преобразователь содержит .триггерный регистр 1, первые и вторые установочные 2 и 3 триггеров 4,которые подключены ко входам перво и второй группы 5 и б, группу элементов ИЛИ-НЕ -7, элементы. ИЛИ 8 й. элемент И-НЕ 9, первьге входы 10, 11 и 12 которых .подключены к первой шине 13 управления, а выходы 1.4, 15 и .16 соотве.Тственно подключены к первой, второй и третьей группе 17, 18 и 19 (1, 2 и 3) триггеров 4, первые два из которых конъюнтйвно связаны с.соответствующими установочными входами 2 и 3, элементы И 20, информационные входы .21 которых подключены ко входам предыдущих разрядов, входы 22 - ко второй шине 23 управления, ко вторым входам 24 и; 25, элементов ИЛИ-НЕ 7 и ИЛИ 8 млашего, разряда и ко второму входу 26. элемента И-НЕ 9, а выходы.27 - ко вторым вхоДам 24 и 25 элементов ИЛИ-НЕ 7 и ИЛИ 8 со 2-го по п-й разряд, тактовые входы 28 (С)триггеров 4, конъюнктивно связанные с третьими входами 19, подключены к входу 29 синхронизации прёобразоватеjift, -, . ..

Преобразователь работает спвдующим о.бразом. ;

Прямое и обратное значение парафазно представленного исходного кода в йиде соответствующих логичес.ких. уровней подается через входы 5 и 6 Hk первые и вторые, установочные входы 2 и 3 триггеров 4. В зависимости от того, на какой из входов 18 или 17 поступает единичный логический; уровень, подготавливается запись в срответствующйё триггеры

4 или прямоз70или обра(. поставленных им в . соответствие

разрядов йСхО,цного кода.

Так, если уровень логической единицы поступает на первый вход 17, то подготав.ливается запись втриггер 4 обратного значения данного разряда исходного кода, так как вход 17 разрешает запись в триггер 4 состояния первого установочного входа 2, соединенного с шиной 5 инверсного кода. Если же логическая

единица поступает на второй вход 18, то этим подготавливается запись в триггер 4 прямого значения данного разряда исходного кода, так как вход

10 18 разрешает зайись в триггер 4 состояния второго установочного входа 3, соединенного с входом 6.

П|эеобразователь приводится в действие частотой синхронизации. Им.- пульсы соответствующей частоты синхронизации, подаваемой непосредственно на вход 29 синхронизации преобразователя, поступают затем на тактовые входы 28 всех триггеров 4 регистра 1. Однако каждый отдельный такто20 вый; импульс только в том случае осуществляет установку триггера 4 в . состояние, определяемое .комбинацией

состояний на их входах записи и уста. новрчных входах 17, 18 и 2, 3, если

25 на их третьи входы 19, конъюнктивно связанные с тактовыми входами 28, подана логическая единица, В противном случае импульсы частоты синхронизации никакого воздействия на

0 состояния триггеров 4 не оказывают.

Выбор режимов работы преобразователя производится путем подачи соответствующей двухразрядной комбинации- двоичных логических уровней на

- первую и вторую шиьйл 13 и 23 управления. Режим хранения выполняется при наличии на шинах 13 и 23 единичных уровней. В этом случае с выхода 16 элемента И-НЕ 9 на третьи входы 19 триггеров 4 поступает нулевой логический уровень, запрещая . переключающее воздейств.ие. импульсов частоты синхронизации на преобр зователь.

Продолжительность хранения содержимого преобразователя определяется временем поддержания единичных . уровней на шинах 13 и 23 управления. Передача.прямого кода (запись в регистр 1 преобразователя прямого

Q значения исходного кода) производится путем подачи и шины 13 и 23 управления единичного и нулевого уровней соответственно. При этом с выходов 15 элементов ИЛИ 8 и с вы- хода 16 элемента И-НЕ 9 на вторые

и третьи входы 18 и 19 соответственно всех триггеров 4 поступает единичный уровень, в то время, как на первые входы 17 триггеров 4 с выходов 14 элёйёнтов ИЛИ-НЕ 7 подает0 ся логический нуль, благодаря чему очередной импульс частоты синхронизации устанавливает все триггеры 4 регистра 1 в состояние, соот.ветствующее прямому значению исходного

5 кода. Аналогично выполняется преобразование прямого кода в обратный, с той лишь разницей, что единичные уровни, наряду с наличием их на тре тьих разрешающих входах 19, поступают на первые разрешающие входы 17, а нулевые - на вторые входы 18 триггеров 4. Управление преобразованием прямого кода в обратный производится подачей на шины 13 и 23 управления нулевых логических уровней. Чтобы преобразовать исходный код в дополнительный , необходимо подать на пер вую шину 13 управления нулевой, а на вторую шину 23 управления единич ный логические уровни. В результате в за,висимости от конкретного значения преобразуемого кода, логическая единица с выходов 27 элементов И 20 через соответствующие элементы ИЛИ поступает на вторые входы 18 тригге ров 4 в тех разрядах регистра 1, по отношению к которым все предшест вующие, более младшие разряды исход ного кода содержат нули. Во всех .остальных разрядах, по отношению к {которым это условие не соблюдается, на выходах 27 элементов И 20 имеют место нулевые логические уровни, в результате чего с выходов 14 соответ ствующих элементов ИЛИ-НЕ 7 на разрешающие входы 17 поступают единицы Поэтому при подаче очередного импуль са на вход 29 синхронизации преобразователя происходит запись прямого значения исходного кода в соответст вукяцие младшие разряды регистра 1 и обратного значения в его остальные разряды. Выполнение входной логики со 2-го по п-й разряд преобразователя на эле ментах И-ИЛИ-НЕ/И-ИЛИ типа ЕСЛ (в негативной логике), состояние первог выхода которых соответствует функции И-ИЛИ-НЕ, а другого - функции И-ИЛИ сокращает аппаратурные затраты на реализацию преобразователя на 2п-1 логических элементов. Предлагаемый преобразователь кода обладает более широкими функциональными возможностями, заключаюпдами ся, наряду с возможностью преобразования прямого кода в дополнительный в .возможности выполнения им еще и преобразования прямого значения кода в обратное, передачи кода без изменения, а также управляемого хранения содержимого преобразователя, в результате чего при использовании предлагаемого преобразователя в регистровых структурах цифровых систем отпадает необходимость в использовании и параллельном подключений к нему регистра с соответствукицей входной логикой, выполняющего недостаю щие прототипу функции, что также упрощает управление цифровой системой и сокращает аппаратурные затратн для п- разрядной регистровой структуры на п триггеров на каждый преобразователь. Формула изобретения Преобразователь прямого кода в дополнительный, содержащий триггерный регистр, группу из (п-2) элементов ИЛИ, где п -число разрядов преобразуемого кода, группу из (п-2) элементов И, i-ый информационный вход элемента И j-oro разряда (j 3-п), ( i 1 - j - 1)соединен с шиной i-oro разряда первой группы входов, первая и вторая группы установочных входов со второго по п-ый и с первого по п-ый разрядов триггерного регистра соединены соответственно с первой и второй группами входов, а тактовые входы триггеров подключены ко входу синхронизации преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения преобразования прямого кода в обратный, преобразователь содержит элемент И, элемент И-НЕ,. первый и второй элементы ИЛИ, группу из п элементов ИЛИ-НЕ, ВЕЛХОДЫ группы элементов ИЛИ-НЕ и всех элементов ИЛИ соединены соответственно с первой и второй группами входов записи триггерного регистра, первый вход элемента И-НЕ, первые входы элементов ИЛИ-НЕ и ИЛИ соединены с первой шиной управления, управляющие входы всех элементов И соединены со второй шиной управления, со вторыми входами элемента ИЛИ-НЁ младшего разряда rpynnij элементов ИЛИ-НЕ, первого элемента ИЛИ, элемента И-НЕ, выход кото рого соединен с третьей группой входов триггерного регистра, первый установочный вход первого разряда триггерного регистра соединен с шиной младщего разряда первой группы входов и с информационным входом элемента И, выходы элемента И и группы элелдантоЕ И подключены ко вторым входам элементов ИЛИ-НЕ и ИЛИ соответствующих разрядов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 238225, кл. 6 Об F 5/02, 1969. 2.Авторское свидетельство СССР по заявке 2506749, кл. G 06 F 5/02, 1977.

.ii№Aai sii

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь прямого кода в дополнительный | 1977 |

|

SU702376A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

Авторы

Даты

1980-07-15—Публикация

1977-10-11—Подача