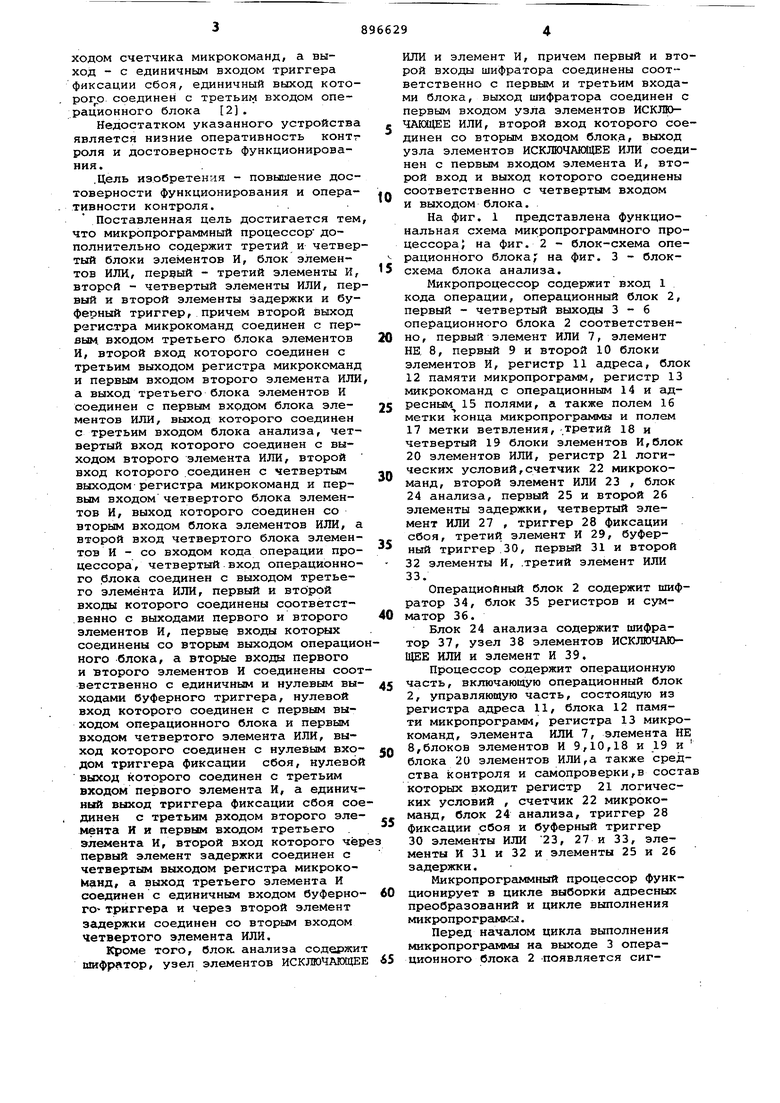

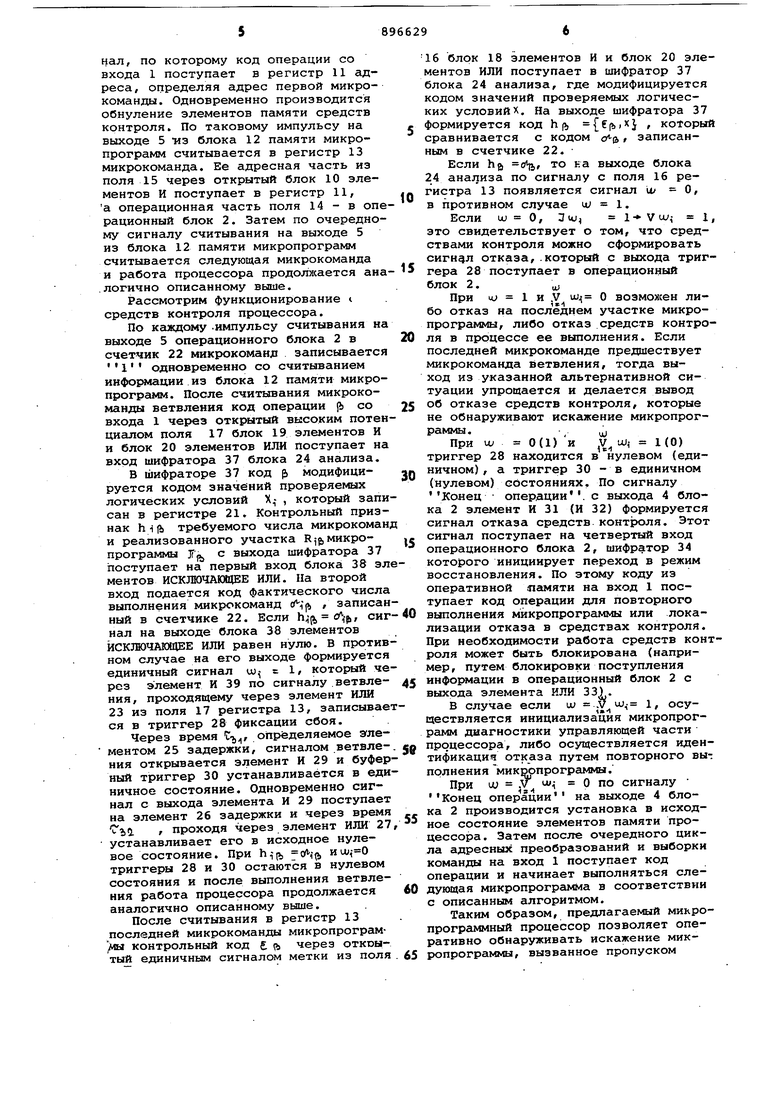

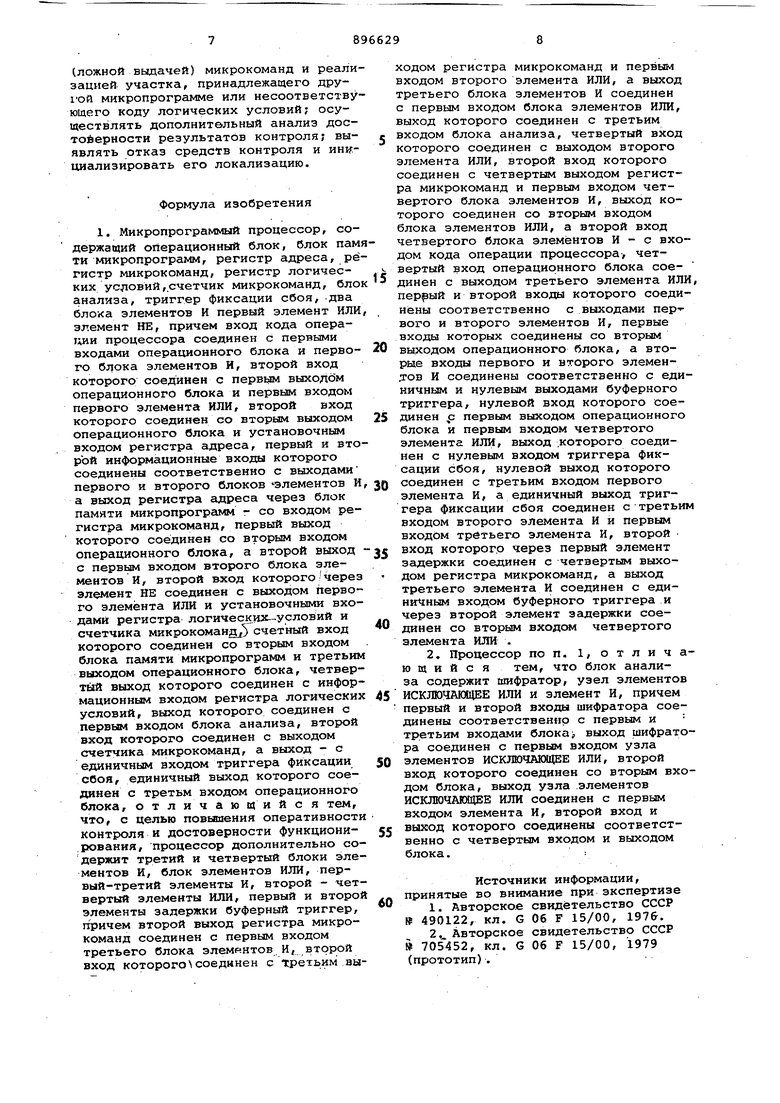

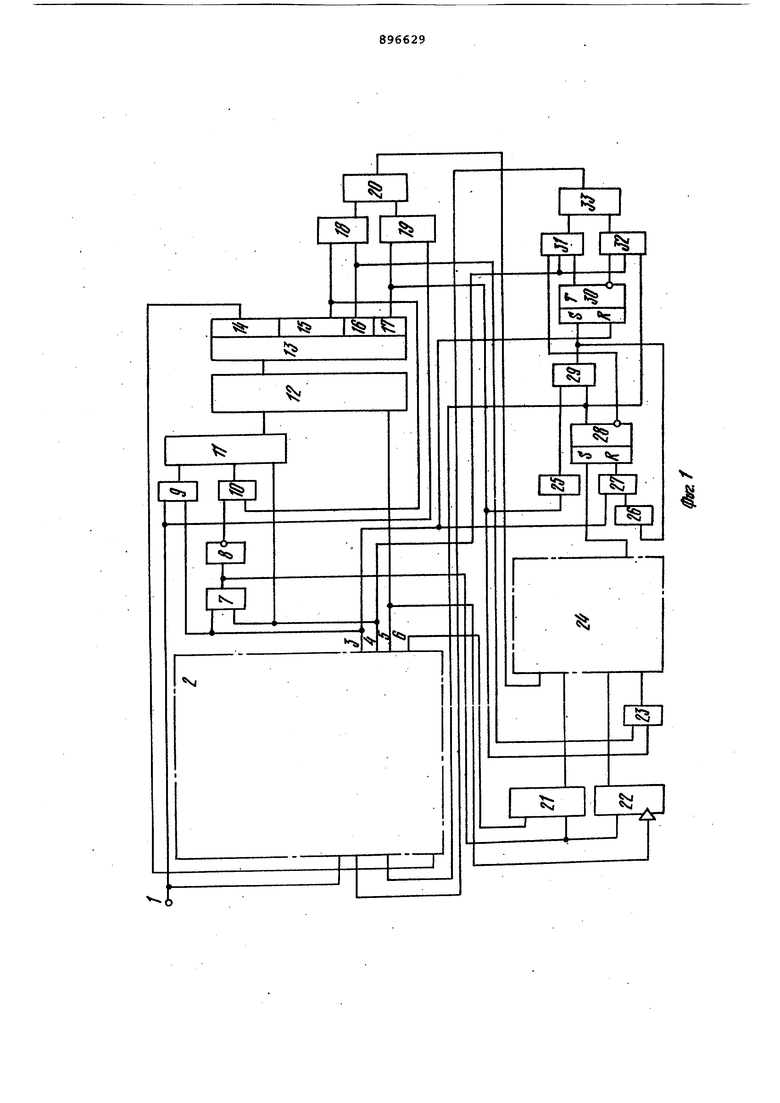

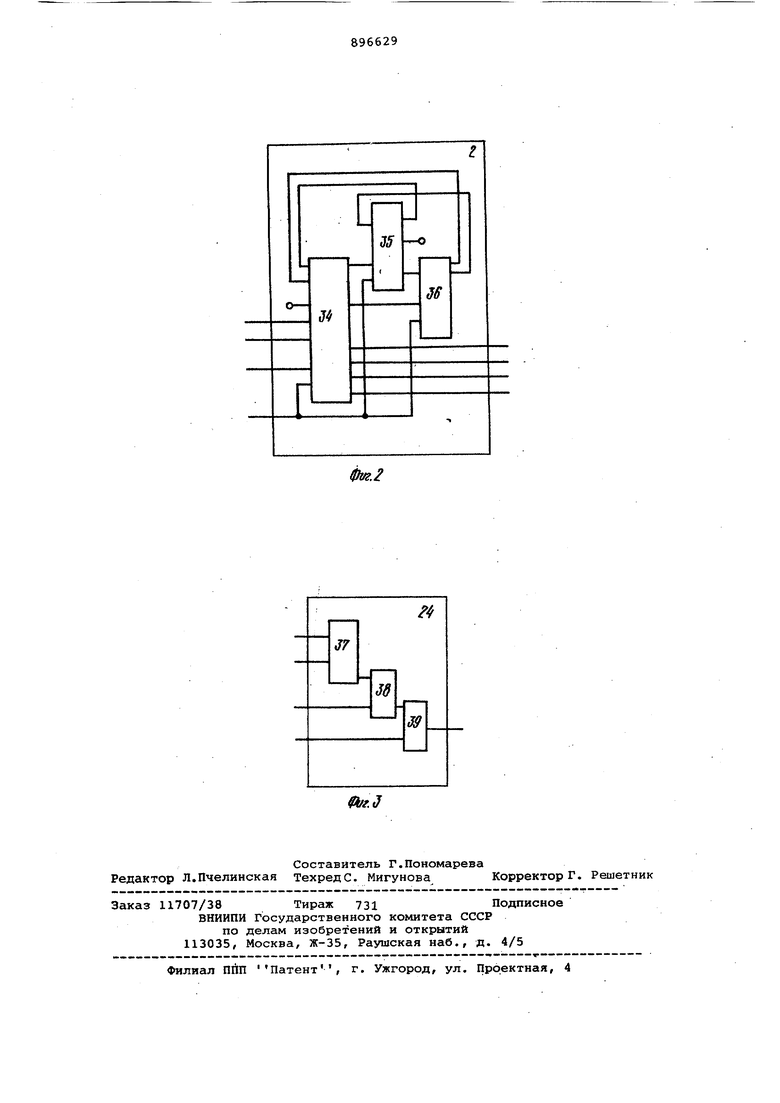

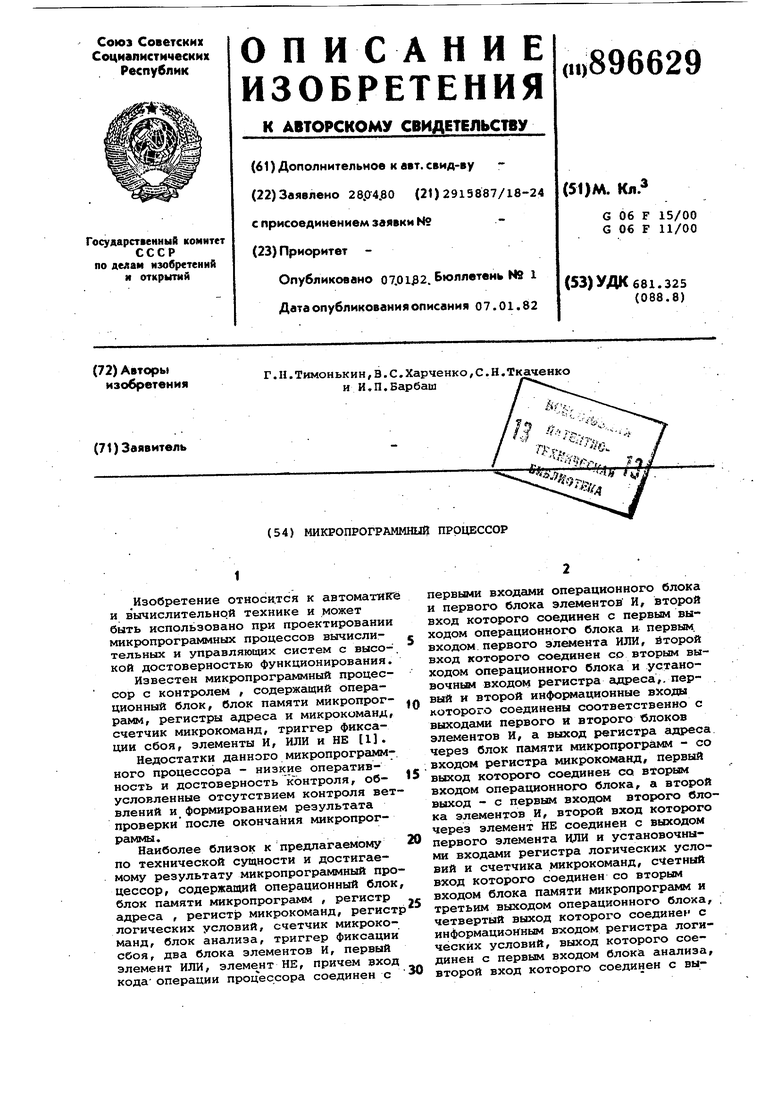

ходом счетчика микрокоманд, а выход - с единичным входом триггера фиксации сбоя, единичный выход которог о соединен с третьим входом операционного блока 2. Недостатком указанного устройства является низние оперативность контг роля и достоверность функционирования. .Цель изобретения - повышение достоверности функционирования и оперативности контроля. Поставленная цель достигается тем что микропрограммный процессор дополнительно содержит третий и четвер тый блоки элементов И, блок элементон ИЛИ, пердый - третий элементы И, второй - четвертый элементы ИЛИ, пер вый и второй элементы задержки и буферный триггер, причем второй выход регистра микрокоманд соединен с первым, входом третьего блока элементов И, второй вход которого соединен с третьим выходом регистра микрокоманд и первым входом второго элемента ИЛИ а выход третьего блока элементов И соединен с первым входом блока элементов ИЛИ, выход которого соединен с третьим входом блока анализа, четвертый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого .соединен с четвертым выходом регистра микрокоманд и первым входом четвертого блока элементов И, выход которого соединен со вторым входом блока элементов ИЛИ, а второй вход четвертого блока элементов И - со входом кода операции процессора, четвертый вход операционного .блока соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены со вторым выходом операцио ного блока, а вторые входы первого и второго элементов И соединены соот ветственно с единичным и нулевым выходами буферного триггера, нулевой вход которого соединен с первым выходом операционного блока и первым входом четвертого элемента ИЛИ, выход которого соединен с нулевым входом триггера фиксации сбоя, нулевой выход которого соединен с третьим входом первого элемента И, а единичный выход триггера фиксации сбоя сое динен с третьим рходом второго элемента И и первым входом третьего . элемента И, второй вход которого чер первый элемент задержки соединен с четвертым выходом регистра микрокоманд, а выход третьего элемента И соединен с единичным входом буферноГО триггера и через второй элемент задержки соединен со вторым входом четвертого элемента ИЛИ. Кроме того, блок, анализа содержит шифратор, узел элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем первый и второй входы шифратора соединены соответственно с первым и третьим входами блока, выход шифратора соединен с первым входом узла элементов ИСКЛЮ- ЧАКХЦЕЕ ИЛИ, второй вход которого соединен со вторым входом блок.а, выход узла элементов ИСКЛЮЧАКВДЕЕ ИЛИ соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с четвертым входом и выходом блока. На фиг. 1 представлена функциональная схема микропрограммного процессора) на фиг. 2 - блок-схема операционного блока; на фиг. 3 - блоксхема блока анализа. Микропроцессор содержит вход 1 кода операции, операционный блок 2, первый - четвертый выходы 3-6 операционного блока 2 соответственно , первый элемент ИЛИ 7, элемент НЕ. 8, первый 9 и второй 10 блоки элементов И, регистр 11 адреса, блок 12 памяти микропрограмм, регистр 13 микрокоманд с операционным 14 и адресным 15 полями, а также полем 16 метки конца микропрогргичмы и 17 метки ветвления, -.третий 18 и четвертый 19 блоки элементов И,блок 20 элементов ИЛИ, регистр 21 логических условий,счетчик 22 микрокоманд, второй элемент ИЛИ 23 , блок 24 анализа, первый 25 и второй 26 элементы задержки, четвертый элемент ИЛИ 27 , триггер 28 фиксации сбоя, третий элемент И 29, буферный триггер .30, первый 31 и второй 32 элементы И, .третий элемент ИЛИ 33. Операциойный блок 2 содержит шифратор 34, блок 35 регистров и сумматор 36. Блок 24 анализа содержит шифратор 37, узел 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ И элемент И 39. Прюцессор содержит операционную часть, включающую операционный блок 2, управляющую часть, состоящую из регистра адреса 11, блока 12 памяти микропрограмм, регистра 13 микрокоманд, элемента ИЛИ 7, элемента НЕ 8,блоков элементов И 9,10,18 и 19 и блока 20 элементов ИЛИ,а также средства контроля и самопроверки,в состав которых входит регистр 21 логических условий , счетчик 22 микрокоманд, блок 24 анализа, триггер 28 фиксации сбоя и буферный триггер 30 элементы ИЛИ 23, 27 и 33, элементы И 31 и 32 и элементы 25 и 26 задержки. Микропрограммный процессор функционирует в цикле выборки адресных преобразований и цикле выполнения микропрограммы. Перед началом цикла выполнения микропрограммы иа выходе 3 операионного блока 2 -появляется сигнал, по которому код операции со входа 1 поступает в регистр 11 адреса, определяя адрес первой микрокоманды. Одновременно производится обнуление элементов памяти средств контроля. По таковому импульсу на выходе 5 -из блока 12 памяти микропрограмм считывается в регистр 13 микрокоманда. Ее адресная часть из поля 15 через открытый блок 10 элементов И поступает в регистр 11, а операционная часть поля 14 - в оп рационный блок 2. Затем по очередно му сигналу считывания на выходе 5 из блока 12 памяти микропрограмм считывается следующая микрокоманда и работа процессора продолжается ан .логично описанному выше. Рассмотрим функционирование t средств контроля процессора. По каждому .импульсу считывания н выходе 5 операционного блока 2 в счетчик 22 микрокоманд записываетс 1 одновременно со считыванием информации из блока 12 памяти микроnporpctMM. После считывания микрокоманды ветвления код операции (Ь со входа 1 через открытый высоким поте циалом поля 17 блок 19 элементов И и блок 20 элементов ИЛИ поступает на вход шифратора 37 блока 24 анализа. В шифраторе 37 код |i модифицируется кодом значений проверяемых логических условий X,- , который запи сан в регистре 21. Контрольный приз нак h i fb требуемого числа микрокоман и реализованного участка R,-j,микропрограммы Jp. с выхода шифратора 37 поступает на первый вход блока 38 эл ментов ИСКЛЮЧАЮЩЕЕ ИЛИ. Па второй вход подается код фактического числа выполнения микрокоманд , , записа ный в счетчике 22. Если ) сЛгр,, си нал на выходе блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ равен нулю. В против ном случае на его выходе формируется единичный сигнал ш 1, который че рез элемент И 39 по сигналу ветвления, проходящему через элемент ИЛИ 23 из поля 17 регистра 13, записывае ся в триггер 28 фиксации сбоя. Через время С-,, определяемое элементом 25 задержки, сигналом ветвлеНИН открывается элемент И 29 и буфер ный триггер 30 устанавливается в еди ничное состояние. Одновременно сигнал с выхода элемента И 29 поступает на элемент 26 задержки и через время . f проходя через элемент ИЛИ 27 устанавливает его в исходное нулевое состояние. При h,; f°i b И1л;, триггеры 28 и 30 остаются в нулевом состояния и после выполнения ветвления работа процессора продолжается аналогично описанному выше. После считывания в регистр 13 последней микрокоманды микропрограм)иы контрольный код . ft через откоытый единичным сигналом метки из поля 16 блок 18 элементов И и блок 20 элементов ИЛИ поступает в шифратор 37 блока 24 анализа, где модифицируется кодом значений проверяемых логических условийX. На выходе шифратора 37 формируется код hft {e|biXJ , который сравнивается с кодом o, записанным в счетчике 22. Если hg 1 то ка выходе блока 24 анализа по сигналу с поля 16 регистра 13 появляется сигнгш ш 0, в противном случае w 1. Если , 3uj, ,- 1, это свидетельствует о том, что средствами контроля можно сформировать сигнал отказа,.который с выхода триггера 28 поступает в операционный блок 2. При UJ 1 и .V uj О возмохсен либо отказ на последнем участке микропрограммы, либо отказ средств контроля в процессе ее выполнения. Если последней микрокоманде предшествует микрокоманда ветвления, тогда выход из указанной альтернативной ситуации упрощается и делается вывод об отказе средств контроля, которые не обнаруживают искажение микропрограммы.. При 0(1) и V uj, 1(0) триггер 28 находится внулевом (единичном), а триггер 30 - в единичном (нулевом) состояниях. По сигналу Коиец опердции. с выхода 4 блока 2 элемент И 31 (И 32) формируется сигнал отказа средств КОНТ|ЕЮЛЯ. Этот сигнал поступает на четвертый вход операционного блока 2, шифра1тор 34 которого инициирует переход в режим восстановления. По этому коду из оперативной яамяти на вход 1 поступает код операции для повторного выполнения микропрограммы или локализации отказа в средствах контроля. При необходимости работа средств контроля может быть блокирована (например, путем блокировки поступления информации в операционный блок 2 с выхода элемента ИЛИ 33V. В случае если ш 1 осуществляется инициализация микропрограмм диагностики управляющей части процессора, либо осуществляется идентификации отказа путем повторного выг прлнения микропрограммы. При IW .V О по сигналу Конец операции на выходе 4 блока 2 производится установка в исходное состояние элементов памяти процессора. Затем пос.пе очередного цикла адресных преобразований и выборки команды на вход 1 поступает код операции и начинает выполняться слеующая микропрограмма в соответствии с описанным алгоритмом. Таким образом, предлагаемый микропрограммный процессор позволяет опеативно обнаруживать искажение микопрограммы, вызванное пропуском (ложной вьщачей) микрокоманд и реали зацией участка, принадлежащего дру1ой микропрограмме или несоответству ющего коду логических условий; осуществлять дополнительный анализ достойерности результатов контроля выявлять отказ средств контроля и инициализировать его локализацию. Формула изобретения 1. Микропрограммый процессор, содержащий операционный блок, блок пам ти микропрограмм, регистр адреса, ре гистр микрокоманд, регистр логических условий,.счетчик микрокоманд, бло анализа, триггер фиксации сбоя, -два блока элементов И первый элемент ИЛИ элемент НЕ, причем вход кода операции процессора соединен с первыми входами операционного блока и первого блока элементов И, второй вход которого соединен с первым выходом операционного блока и первым входом первого элемента ИЛИ, второй вход которого соединен со вторым выходом операционного блока и установочным входом регистра адреса, первый и вто рой информационные входы которого соединены соответственно с выходами первого и второго блоковэлементов И а выход регистра адреса через блок памяти микропрогрги - со входом регистра микрокоманд, первый выход которого соединен со вторым входом операционного блока, а второй выход с первым входом второго блока элементов И, второй нход которого/через элемент НЕ соединен с выходом первого элемента ИЛИ и установочными входами регистра логических-условий и счетчика микрокоманд счетный вход которого соединен со вторым входом блока памяти микропрограмм и третьим выходом операционного блока, четвертый выход которого соединен с информационным входом регистра логических условий, выход которого соединен с первым входом блока анализа, второй вход которого соединен с выходом счетчика микрокоманд, а выход - с единичным входом триггера фиксации сбоя, единичный выход которого соединен с третьм входом операционного блока, отличаю щийс я тем, что, с целью повышения оперативности контроля и достоверности функциони,рования, процессор дополнительно содержит третий и четвертый блоки элементов И, блок элементов ИЛИ, первый-третий элементы И, второй - четвертый элементы ИЛИ, первый и второй элементы задержки буферный триггер, причем второй выход регистра микрокоманд соединен с первым входом третьего блока элемянтов И, второй вход которого соединен с третьим выходом регистра микрокоманд и первым входом второго элемента ИЛИ, а выход третьего блока элементов И соединен с первым входом блока элементов ИЛИ, выход которого соединен с третьим входом блока анализа, четвертый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с четвертым выходом регистра микрокоманд и первым входом четвертого блока элементов И, выход которого соединен со вторым входом блока элементов ИЛИ, а второй вход четвертого блока элементов И - с входом кода операции процессора, четвертый вход операционного блока соединен с выходом третьего элемента ИЛИ, перрый и второй входы которого соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены со вторым выходом операционного блока, а вторые входы первого и второго элемен.тов И соединены соответственно с единичным и нулевым выходами буферного триггера, нулевой вход которого соединен р первым выходом операционного блока и первым входом четвертого элемента ИЛИ, выход .которого соединен с нулевым входом триггера фиксации сбоя, нулевой выход которого соединен с третьим входом первого элемента И, а единичный выход триггера фиксации сбоя соединен с третьим входом второго элемента И и первым входом третьего элемента И, второй вход которого через первый элемент эадержки соединен с четвертым выходом регистра микрокоманд, а выход третьего элемента И соединен с единичным входом буферного триггера и через второй элемент задержки соединен со вторым входсии четвертого элемента ИЛИ . 2. Процессор по п. 1, отличающийся тем, что блок анализа содержит шифратор, узел элементов ИСКЛЮЧАЩЕЕ ИЛИ И элемент И, причем первый и второй входы шифратора соединены соответственно с первым и третьим входами блока;, выход шифратора соединен с первым входом узла элементов ИСКЛЮЧАЮйЩЕ ИЛИ, второй вход которого соединен со вторым входом блока, выход узла элементов ИСКЛЮЧАЩЕЕ ИЛИ соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с четвертым входом и выходом блока.: Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 490122, кл. G 06 F 15/00, 197&. 2.Авторское свидетельство СССР №705452, кл. G 06 F 15/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-28—Подача