{54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОВ С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропрограммный процессор | 1980 |

|

SU896629A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммный процессор | 1980 |

|

SU980098A1 |

.,:, .-,:

Микропрограммный процессор с кбит ролем относится к области цифровой вычислительной техники и может быть использован в ЭВМ- с микропрограммньш управлением.

Известен микропрограммный процессор с контролем, содержащий операдиг онный блок, регистры адресов микрокоманд и собственно микрокоманд/ блок памяти микрокоманд, узел qpaaненияг триггер фиксации сбоя и логические элементы И, ИЛИ, НЕ

Недостатком устройства являются низкая достоверность функционирования и низкая оперативность контроля.

Наиболее близкнм по технической сущности и достигаемому эффекту из известных устройств к изобретению . является микропрограммный процессор, содержащий опергщионный блок, блок памяти микрокоманд, регистр «1кро-. команд, два регистра адреса, регистр кода операций, блок сравнения, триггер фиксации.сбоя, десять элементов И, четыре элемента ИЛИ, два элемента НЕ, элемент задержки. Шдход кода операции- операционного блока соединен с входом регистра кода операции, выход которого соединен с первым входом первого, элемента И, второй вход

которого соединеи е выходом начала оп шдии-рперационноро блока и пер1зым вход торвого элемента ИЛИ, Выс ход первого элемента. И соединен с

пёржй входом первого регистра адреса, второй вход которого соединен с BUxoscnit второго элемента И, а - С перевес вхсцдами блока па111 МЯ7И, третьего И четвертого элементов . В1сбд третьего элемента И соединен с выходом чтения микрокоманд опероциойного блоха, вторым входом блока па1у01ти микрокоманд, а также через элемент задержки с

1 первым входом пятого элемента и. &лсод третьего элемейта И соединен с neipf at входом второго «чэегистра . Выход блока памяти микрокома1|д соединен с входом регистра

2 иткрокоманд, выход м крокоманд соединен, с первым входом операционного ОяОхв адресный выход - с вторым входом операщюнного блока и первым входом sfottoro элемента И, выход

25 логических условий - с первым входом swKMBHta И. второй вход второго эледлевта и через первый элемент BE соедияея.с выходом первого элемента Wra, «торой вход которого соединен

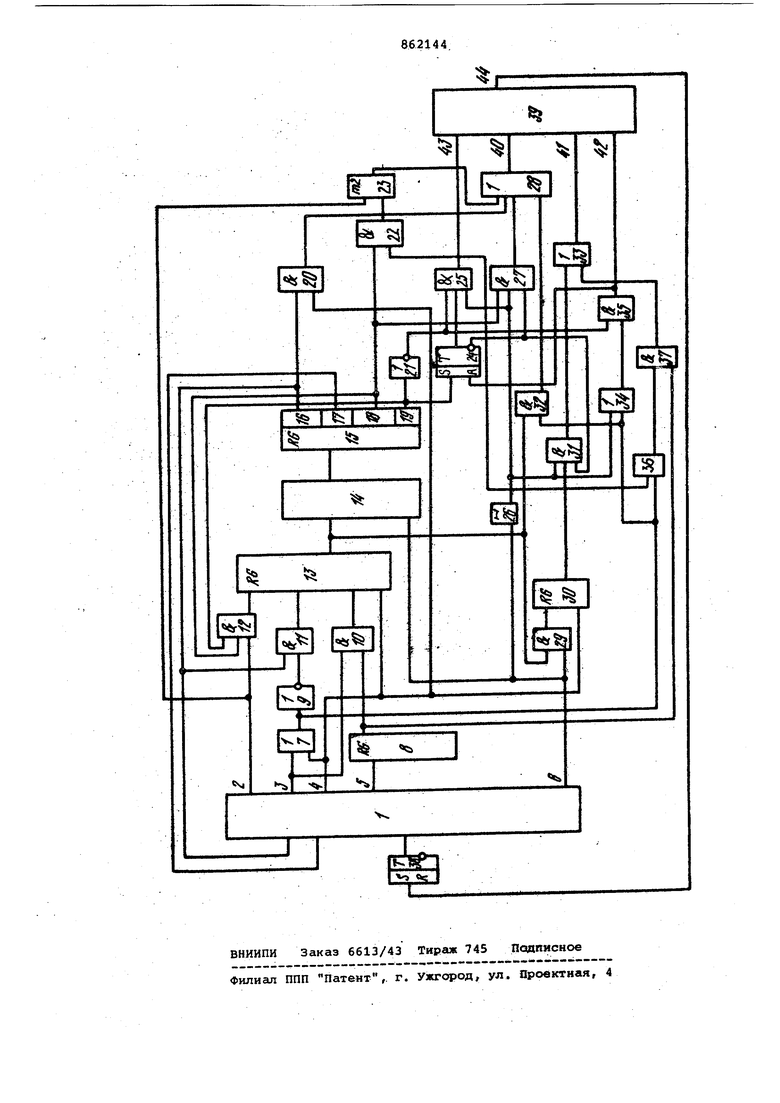

за с vt yeojUfXt конца операции операционного блока, первым входом седьмого эле мента И, третьим входом первого регистра адреса, вторым входом второго регистра адреса, выход которого соединен с вторым входом пятого элемента И. Второй вход седьмого элемента И соединен с адресным выходом регист ра микрокоманд, выход - с первым вхо дом второго элемента ИЛИ, выход кото рого соединен с первым входом блока сравнения. Второй вход второго элемента ИЛИ соединен с выходом шестого элемента И, второй вход которого сое динен с выходом элемента задержки и первым входом третьего элемента ИЛИ, второй вход которого соединен с выхо дом первого элемента ИЛИ и вторым входом четвертого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ. Первый вход восьмого элемента И соединен с выходом регистра кода операций, а выход - с первым входом четвертого эле мента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход - с вторым входом блока срав нения, третий вход которого соединен с выходом девятого рлемента И, первый вход которого соединен с выходо третьего элемента ИЛИ. Второй вход девятого элемента И через второй эле мент НЕ соединен с выходом метки регис-рра микрокоманд и первым входом десятого элемента И, второй вход которого соединен с выходом логических условий регистра микрокоманд, а третий вход - с выходом логических усло вий операционного блока, третий вход которого соединен с выходом триггера фиксации сбоя, вход которого соединен с выходом блока сравнения. Выход десятого элемента И соединен с четвертым входом первого регистра адреса Г2. Недостатком устройства является низкая оперативность контроля соответствия выполняемой микропрограммы той микропрограмме, код которой записан в регистре кода операции. Целью изобретения является повышение оперативности контроля и достоверности функционирования микропрограммного процессора. Поставленная цель достигается тем, что в микропрограммный процессор с контролем дополнительно введены триггер признака, сумматор по модулю два, одиннадцатый и двенадцатый элементы И, пятый элемент ИЛИ. Первый вход сумматора по модулю два соединен с выходом логических условий операционного блока, выход - с четвертым входом второго элемента ИЛИ, второй вход сумматора по модулюдва - с выходом одХиннадцатого эле мента И,первый вход которого соедине с выходом логических условий регистра микрокоманд, второй вход одинна,дцатого элемента И - с выходом двенадцатого элемента И, четвертым входом блока сравнения и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с вторым входом восьмого элемента И. Первый вход двенадцатого элемента И соединен с выходом второго элемента НЕ, второй вход - с единичным выходом триггера признака, единичный вход которого соединен с выходом метки регистра микрокоманд. Нулевой вход триггера признака соединен с выходом девятого элемента И, а нулевой выход - с третьими входами пятого и шестого элементов И, третий вход двенадцатого элемента И соединен с выходом элемента задержки. Сущность изобретения состоит в повышении оперативности контроля за счет увеличения числа проверок соответствия выполняемой микропрограммы заданному коду операции, а также в повышении достоверности функционирования за счет осуществления контроля правильности ветвления NgiKpoпрограммы. При этом контроль соответствия выполняемой микропрограмкы заданному коду операции и контроль правильности выполнения ветвлений в микропрограмме осуществляются одновре1 ванно общими средствами проверки. Однако временный контроль реализуется после считывания первой микрокоманды, следующей за очередным ветвлением и в микропрограмме. Это позволяет повысить оперативность контроля соответствия заданного кода операции выполняемой Л4икро про грамме и довести ее до среднего времени между ветвлениями, а также повысить достоверность функционирования за счет организации контрюля ветвлений. На чертеже приведена функциональная схема микропрограммного процессора с контролем. На чертеже использованы следующие обозначения: операционный блок 1, выходы логических условий, начала операции, конца операции, кода операции и чтения микрокоманд 2-6 соответственно, первь1й элемент ИЛИ 7, и регистр кода операций 8, первый элемент НЕ 9, первый элемент И 10, второй элемент И 11, десятый элемент И 12, первый регистр адреса 13, блок пг1Мяти микрокоманд 14, регистр микрокоманд 15 с полями адресными 16, микрокоманд 17, логических условий 18, метки 19, седьмой элемент И 20, второй элемент НЕ 21, одиннадцатый элемент И 22, сумматор по модулю два 23, триггер признака 24, двенадцатый элемент И 25, элемент задержки 26, шестой элемент И 27, второй элемент ИЛИ 28, третий элемент И 29, второй регистр адреса 30, петый элемент И 31, четаертый элемент И 32, четвертый элемент ИЛИ 33, третий элемент ИЛИ . 34j девятый элемент И 35, пятый элемент ИЛИ 36, восьмой элемент И 37, триггер фиксации сбоя 38, блок сравне НИН 39, первый - четвертый входы 4043 блока сравнения соответственно,

выход 44 блока сравнения.

Первый регистр адреса 13 предназначен для хранения адреса Очередной микрокоманды во время выполнения текущей микрокоманды.

Второй регистр адреса 30 предназначен для хранения кода адреса, поступившего с первого регистра адреса 13 на время считывания микрокоманды из блока памяти микрокоманд 14

Микропрограммный процессор работа ет следуквдим образом.

Выполнение каждой команды разделено на два цикла: цикл выборки команды и цикл ее исполнения в соответствии с кодом операции. Первый цикл является общим для всех команд, в то время как цикл исполнения состоитиз различных микропрограмм для различных команд.

В конце цикла выборки командал и адресных преобразований код операций поступает в регистр кода операций 8, и операционный блок 1 формирует сигнал начала операции. По этому сигналу код операции поступает через первый элемент И 10 в П1ервый регистр адреса 13.

Правидьность записи кода операции в регистр адреса 13 контролируется путем сравнения его содержимого с содержимым регистра кода операций 8 по сигналу начала операции, поступающего из операционного блока 1.

По этому сигналу гшрес первой микрокоманды с выхода первого регистра адреса 13 поступает через четвертый элемент И 32 на третий вход второго элемента ИЛИ 28 и далее на первый вход 40 блока сравнения 39.

Одновременно с этим сигнгш Начала операции с выхода первого элемента ИЛИ 7 поступает через пятый элемент ИЛИ 36 на второй вход восьмого элемента И 37, разрешая прохождение кода операции с выхода регистра кодг операции 8 через четвертый элемент ИЛИ 33 на второй вход блока сравнения 39. Далее происходит сравнение указанных кодов по сигналу начала опера1дии, который поступает с выхода первого элемента ИЛИ 7 через третий элемент ИЛИ 34 и открытый девятый элемент И 35 на третий вход 42 блока сравнения 39. Если коды не совпадают то на выходе 44 блока сравнения 39 формируется сигнал, который поступает на вход триггера фиксации сбоя 38 и запрещает дгшьнейшую работу операционного блока 1. Если коды совпадают, то работа процессора продолжается. На выходе чтения микрокоманд 6 операционного блока 1 формируется сигнал, по которому происходит считывание микрокоманды по соотJ ветствующему адресу из блока памяти макрокоманд 14. Этот же сигнал поступает на второй вход третьего элемента И 29, и адрес микрокоманды записывается во второй регистр адреса 30. Через время f (время считывания одной микрокоманды из блока памяти микрокоманд 14) в адресном

0 поле 16 регистра микрокоманд 15 форкируется адрес следующей микрокоманды, который поступает на первый вход второго элемента И 11, открытый элементом НЕ 9. (во время выполнения

5 микропрогрсиу1МЫ сигнала на выходах начала и конца операции и выходе элемента ИЛИ 7 отсутствуют), и на второй вход операционного блока 1. Проходя через элемент И 11, адрес

0 записывается в первый регистр адреса 13.

На первый вход операционного блока 1 поступает операционная часть считанной микрокоманды с поля микрокоманд 17 регистра микрокоманд 15.

5

С поля логических условий 18 pe гистра кмкрокоманд 15 считывается адрес исполняемой микрокоманды, который поступает на первый вход шестого элемента И 27. В это время на

0 его второй вход.поступает сигнал с выхода чтения 1«|крокоманд 6 через элемент задержки 26, а на третий вход - единичный сигнал с нулевого выхода триггера признака 24. Адрес

5 выполняемой микрокоманды через второй элемент ИЛИ 28 поступает на первый вход 40 блока сравнения 39. После записи адреса выполняемой микрокоманды во второй регистр адреса 30

0 через время Tj на первый вход пятого элемента И 31 поступит сигнал, разрешающий- передачу адреса, записанного во йтором регистре адреса, на второй вход четвертого элемента ИЛИ 33. Передача адреса возможна, посколь5ку на третий вход пятого элемента И 31 поступает единичный сигнал с нулевого выхода триггера признака 24

Через четвертый элемент ИЛИ 33

0 адрес, записанный во второй регистр адреса 30, поступает на второй вход 41 блока сравнения 39.

С выхода элемента задержки 26 чербэ BpeMsfj сигнал считывания мик5рокоманд поступает на первый вход девятого элемента И 35 через третий элемент ИЛИ 34, на второй вход которого поступает разрешающий сигнал с выхода метки 19 регистра микрокоОманд 15. Сформированный сигнал с выхода девятого элемента И 35 поступает на третий вход 42 блока сравнения 39. При этом контролируется правильность считывания микрокоманды путем сравнения поступивших на его первые

5

ва входа кодов. В зависимости от езультатов сравнения кодов адресов работа процессора аналогична описанной выше. В дальнейшем при считывании икрокоманд из блока памяти микрокоманд 14 контроль порядка и правильности их считывания осуществляется аналогично.

При выполнении микрокоманды ветвления в поле логических условий. 18 регистра.микрокоманд 15 записывается код проверяемого логического условия. Он поступает на второй вход десятого элемента И 12, на первый его вход поступает единичное значение с выхода метки 19 регистра микрокоманд 15, а на третий - значение проверяемого логического условия. В результате формируется (модифицируется) адрес следующей Микрокоманды. Единичным сигналом с выхода Метки 19 регистра микрокоманд 15 триггер признака 24 устанавливается в единичное состояние, и на его единичном выходе появляется разрешающий сигнал, который поступает на второй вход двенадцатого элемента И 25..

При этом не происходит сравнения значений кодов, записанных в поле логических условий 18 регистра микрокоманд 15, и содержимого второго регистра адреса 30, поскольку на второй вход девятого элемента И 35 поступает нулевое значение с выхода метки 19 регистра микрокоманд 15 и сигнал на разрешение сравнения отсутствует. На третий вход шестого элемента И 27 поступает нулевой сигнал с нулевого выхода триггера признака 24, запрещая передачу информации в блок сравнения 39. После считывания первой микрокоманды после ветвле 1ия в поле метки 19 регистра микрокоманд 15 появляется нулевой сигнал, который инвертируется вторым элементом НЕ 21 и поступает на первый вход Двенадцатого элемента И 25, на второй вход которого поступает единичный сигнал с выхода триггера признака 24 и с выхода чтения микрокоманд 6. На выходе формируется сигнсш разрешения, который поступает на второй вход одиннадцатого элемента И 22. На первый вход элемента И 22 поступает контрольный признак, записанный в поле логических условий 18 первой микрокоманды после ветвлений. В качестве контрольного признака выступает код операции, модифицированный значением проверяемого логического условия. Модифицированный таким образом код поступает иа второй вход сумматора по модулю два 23, на первый вход которого поступает значение пров яемого логического условия. На выходе сумматора по модулю два 23 в результате формируется фактическое значение кода операции, которое поступает на етвертый вход второго элемента ИЛИ 28 и далее на первый вход iO блока сравнения 39.

Сигнал разрешения с выхода двенадцатого элемента И 25 поступает также на первый вход пятого элемента ИЛИ 36 и с его выхода на второй вход восьмого элемента И 37. В )езультате

действительное значение .кода опе рации с.выхода регистра кода операци 8 через четвертый, элемент ИЛИ 33 поступает на второй вход 41 блока сравнния 39. Одновременно с этим на четвертый его вход 43 поступает сигнал на разрешение сравнения кодов с выхода элемента И 35, а затем сигналом с выхода элемента И 35 триггер признака 24 устанавливается в нуль. Далее работа процессора аналогична описанной выше.

Одновременно с контролем соответствия выполняемой микропрограммы заданному коду операции осуществляется контроль правильности ветвлений.

При ошибочном переходе nOJby4eHный в результате суммирования контрольного признака и значения проверяемого логического условия код не совпадает с требуекым кодом операции и на выходе 44 блока сравнения 39 формируется сигнал отказа.

В да льнейшем процессор реализует оставшуюся часть микропрограмлы, осуществляя контроль правильности считывания и порядка следования микрокоманд и проверяя принадлежность микрокоманд заданной микропрограмме по описанным выше алгоритмам.

При считывании последней микрокоманды в поле логических условий 18 регистра глнкро.команд 15 записывается адрес считанной микрокоманды, а в адресном поле 16 - код выполняемой операции. По сигналу считывания, задержанному элементом задержки 26, блок сравнения 39, аналогично описанному выше, осуществляет сравнение кодов, поступивших из поля логичес ких условий 18 регистра микрокоманд 15 и второго регистра адреса 30.

. По сигналу конца операции первый и второй регистры адреса 13 и 30 соответственно обнуляются, а блок сравнения 39 сравнивает содержимое адресного поля 16 регистра микроко(Манд 15 и регистра кода операций 8. При этом на первый вход 40 блока сравнения 39 через второй элемент ИЛИ 28 с выхода седьмого элемента И 20 поступает фактическое значение кода операции, а на второй вход 41 - Tpe6yeh« e значение кода операции с выхода регистра кода операции 8..Кроме того, на первый вход блока сравнения 30 поступает код через четвертый элемент И 32. Если суммарный код первого регистра адреса 13 и адресного поля 16 регистра микрокоманд 15 равен коду, записанному .в регистре кода операции 8, это означает, что микропрогракма выполнена в соответствии с заданным кодом операции, а первый регистр адреса 13 работоспособен и находится в нулевом состоянии. В этом случае процессор переходит к выполнению цикла выборки следующей команды.. Если сравниваемые коды не равны, блок сравнения 39 формирует сигнал, который триггер фиксации сбоя 38/передает в операционный блок 1. ё результате операционный блок 1 инициирует повторение участка микропрограм мы или выполнение диагностической микропрограко«. В процессоре проверяются также средства контроля его функционирования. При их отказе коды, сравнивае{« блоком сравнения 39, будут отличаться-, что приведет к срабатыванию триг гера фиксации сбоя 38. 7аким образом, введение новых элементов и связей позволяет существенно повысить достоверность функцио нирования микропрогракмного процессора за счет повышения полноты контроля всех этапов выполнения микро-. программы. При этом также увеличивается оперативность контроля соответствия выполняемой микропрограм№а заданному коду операции. Это, в свою очередь, позволяет более эффективно решать задачу восстановления искаженной информации и задачу локализации отказавших элементов, поскольку момент обнаружения отказа (начало, конец операщии, линейный участок, ветвление) дает возможность значительно уменьшить количество подозреваемых элементов. Формула изобретения Микропрограммный процессор е конт ролем, содержащий операционный -блок, блок памяти микрокоманд, регистр вlк рокоманд, два регистра адреса, регистр кода операций блок сравнения триггер фиксации сбоя, десять элемен тов И, четыре элемента ИЛИ, два элемента НЕ, элемент задержки, причем выход кода операции операционного блока соединен с входом регистра кода операции, выход которого соединён с первым входом первого элемента И, второй вход которого соединен с выхо дом Начала операции операционного блока и первым входом первого элемен та ИЛИ, выход первого элемента И соединен с первым входом первого регистра адреса, второй вход которого соединен с выходом второго элемента И, а выход - с первыми входами блока памяти, третьего и четвертого элементов И, второй вход третьего элемента И соединен с выходом чтения микрокоманд операционного блока, втоРИМ входом блока памяти микрокоманд,, а также через &лемент| задержки с первым входом пятого элемента И, выход третьего элемента И соединен с первым входом второго регистра адреса,, выход блока памяти микрокоманд соединен с входом регистра микрокоманд, выход микрокоманд которого соединен с первым входом операционного блока, адресный выход - с вторым входом операционного блока и первым входом второго элемента И, выход логических условий - с первым входом шестого элемента И, второй вход второго элемента И через первый элемент НЕ соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом конца операции операционного блока, первым входом седьмого элемента И, третьим входом первого регистра адреса, вторым входом второго регистра адреса, выход которого, соединен с вторым входом пятого элемента И, второй вход седьмого элемента И соединен с адресным выходомрегистра микрокоманд, выход седьмого элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом блока сравнения, второй вход второго элемента ИЛИ соединен с; выходом шестого элемента И, второй вход которого соединен с выходом элемента задержки и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента ДЛИ и вторьич входом четвертого элеяента И, выход которого соединен с третьим входом втсфого элемента ИЛИ, первый вход восьмого элемента И соединён с выходом регистра кода операций а выход - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход - с вторым входом блока сравнения, третий вход коtopoTO соедо1нен с выходом девятого элемента И, первый вход которого соединен с выходом третьего элемента ИЛИ, второй вход девятого элемента И через второй элемент НЕ соединен с выходом метки регистра микрокоманд и первым входом десятого элемента и, второй вход которого соединен с выходом логических условий .регистра микрокоманд, а третий вход - с выходом логических условий операционного блока третий вход которого соединен с выходом триггера фиксации, сбоя, вход которого соединен с выходом блока сравнения, выход десятого элемента И соединен с четвертым входом первого регистра адреса, отличаю щи и с я Тем, что, с целью повышения достоверности функциониования и оперативности контроля, в него введены Триггер признака, суматор по модулю два, одиннадцатый и

двенадцатый элементы И, пятый элемент ИЛИ, причем первый вход сумматора по модулю два соединен с выходом логических условий операционного ,блока, выход - с четвертым входом второго элемента ИЛИ, второй вход , сумматора по модулю два - с выходом одиннадцатого элемента И, первый вход которого соединен с выходом логических услорий регистра микрокоманд, второй вход - с выходом двенадцатого элемента И, четвертым входом блок сравнения и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с вторым входом восьмого элемента И, первый вход двенадцатого элемента И соединен с выходом второго элемента НЕ-, второй вход с единичным выходом триггера признака, единичный вход которЬго соединен с выводом метки регистра микрокоман нулевой вход триггера признака соединен с выходом девятого элемента И, а нулевой выход - с третьими входами пятого и шестого элементов И, третий вход двенадцатого элемента И соединен с ш ходом элемента задержки.

Источники информации, принятые во внимание при экспертизе

G 06 F 9/16, 1975.

кл. G 06 F 15/20, G 06 F 11/00, 1978 (прототип).

NX

i

N

Ч

±1

jfc: W

fe5

feb

Ч

r k

ШЛ

«S4

Ч

Авторы

Даты

1981-09-07—Публикация

1980-01-15—Подача