Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ул- равления и контроля рпспределенных цифровых систем и ЭВМ.

Целью изобретения является, повышение быстродействия и расширение области применения путем обеспечения реализации одиночных, групповых и смешанных дисциплин обслуживания запросов, поступающих от абонентов,

В предлагаемом устройстве предусмотрены следующие дисциплины обслуживания запросов;

а)обслуживание одиночных абонентов j требующих выполнения линейных последовательностей микрокоманд - безусловных алгоритг-юв проверки одиночных , объ е к тов |

б)обслужи:в анйе одиночных абонентов, требующих изменения последовательностей микрокоманд - условных алгоритмов проверки одиночных объектов;

в)обслуживание одиночных абонентов, состоящих из ряда узлов, обра- ботка заявок от которых осуществляется е соответствии с их приоритетами - условньзх алгоритмов выбора порядка проверки узлов;

г)обслуживание группируемых абонентов, вырабатывающих обобщенный сигнал запроса - алгоритмов одновременной проверки группы абонентов;

д)обслуживание абонентов, требующих выполнения микропрограммы проверки, состоящей из микропрограмм, последовательность реализации которых зависит от типа абонента.

Дисциплины & и А по сравнению с прототипом позволяют существенно повысить скорость обслуживания запросов и расширить область применения устройства.

Введение новых связей для регистров микроопераций позволяет хранить и выдавать в течение цикла работы второго блока синхронизации коды микрооперацийо

Введение новых связей для регистра запросов позволяет обеспечить их хранение и исключение обслзтаенных запросов,

Вэедение новых связей для буферного регистра позволяет запомнить .наиболее приоритетный запрос.

Введение второго блока синхрони- захщи и его связей, а также новых

2151142

связей первого блока сжхронизации позволяет синхронизировать работу устройства при обслуживании запросов,

5 Введение второго коммутатора и его связей обеспечивает подачу адреса в начальных микрокомандах с входа кода операции или nepBoj o входа логических условий устройства в 10 зависимости от состояния первого

триггера управления (режима работы),.

Введение второго узла приоритета и его связей позволяет устанавливать очередность обслуживания соот15 ветствующих условий (сигналов от разноприоритетных узлов абонентов) в процессе выполнения микропрограммы обработки соответствующего запроса,

20 Введение шифратора и его связей позволяет формировать начальный адрес микропрограммы обслуживания . выбранного запроса.

Введение комбинационного блока

25 позволяет формировать код управления мультиплексором адреса в зависш-юс- ти от сигналов логических условий и сигналов соответствующих микроопера -: - ций,

30 Введение первого и второго триггеров управленияS блоков ключей, элементов И и ИЛИ, а также элемента и обусловленных ими связей обеспечивает управление работой уст ройства в различных режимах функционирования,

В отличие от прототипа предлагаемое устройство позволяет организовать обслуживание запросов от оди40 ночных абонентов, состоящих из отдельных разноприоритетных узлов; группируемых абонентов с общим сигналом запроса; одиночных и группируемых абонентов с индивидуальными мак45 ропрограммами обслуживания.

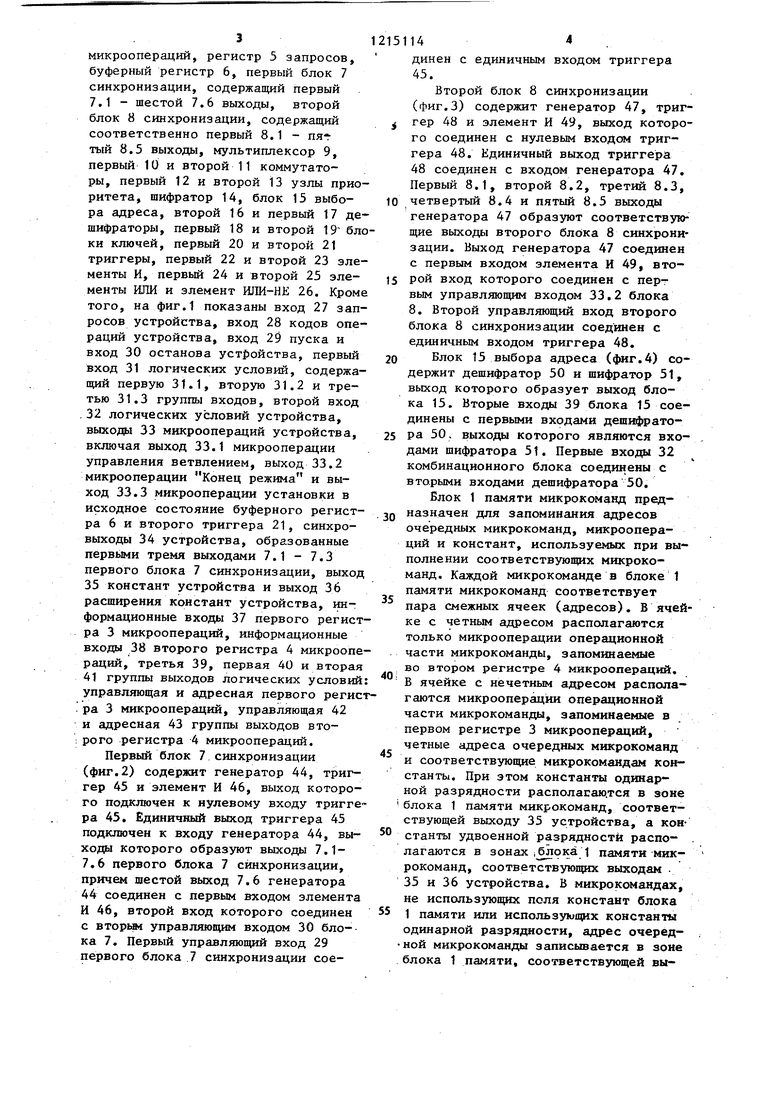

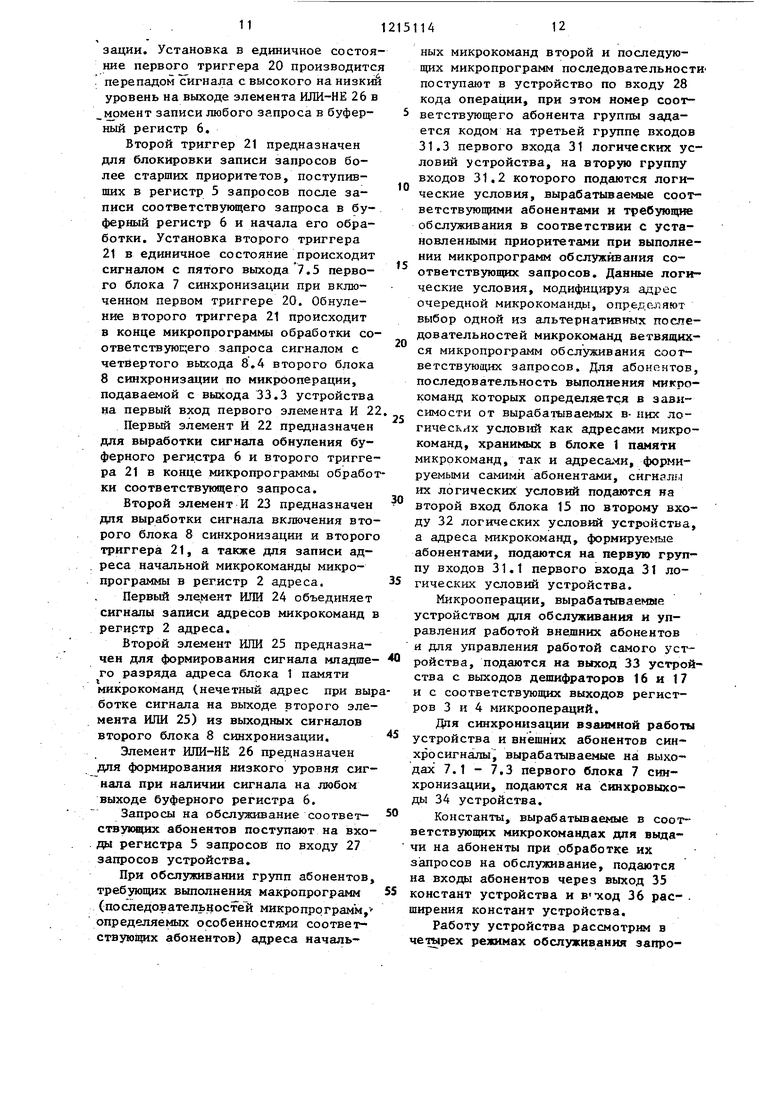

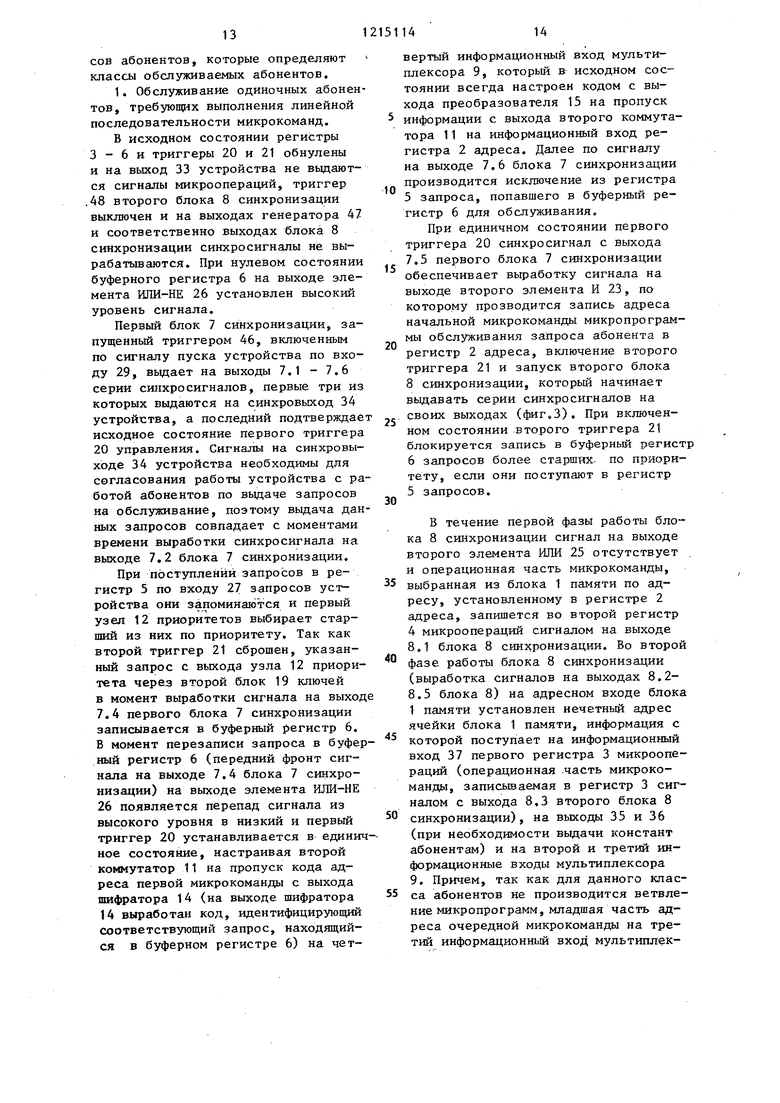

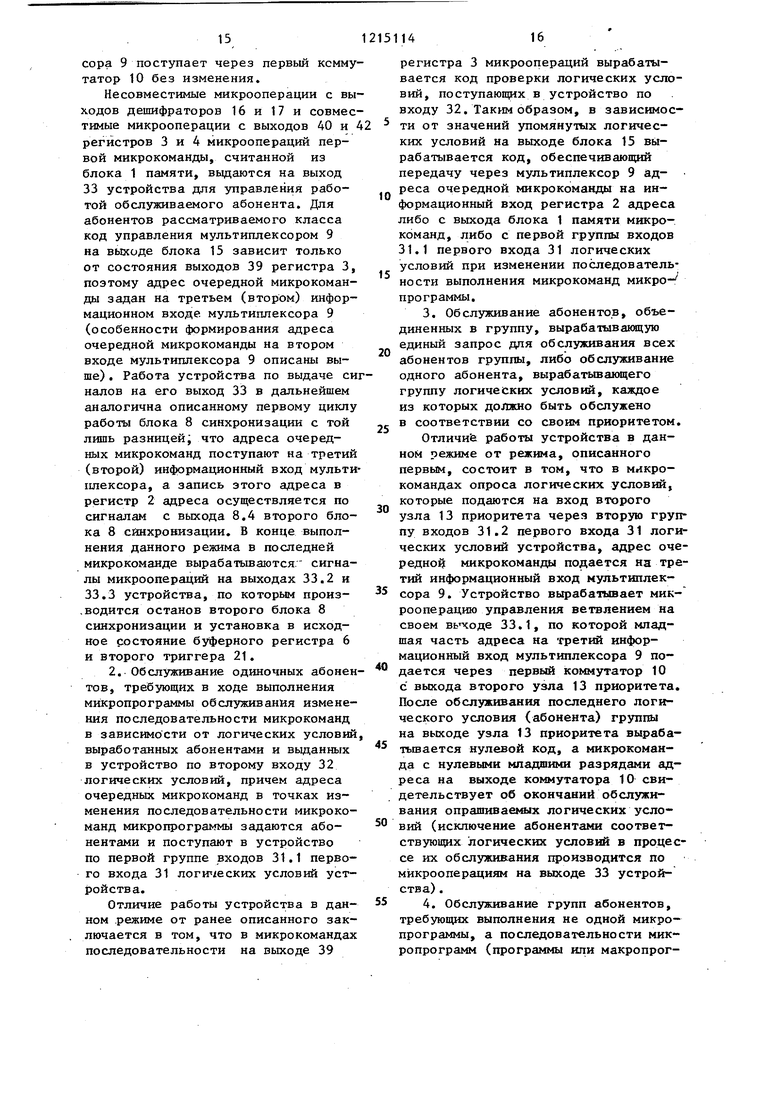

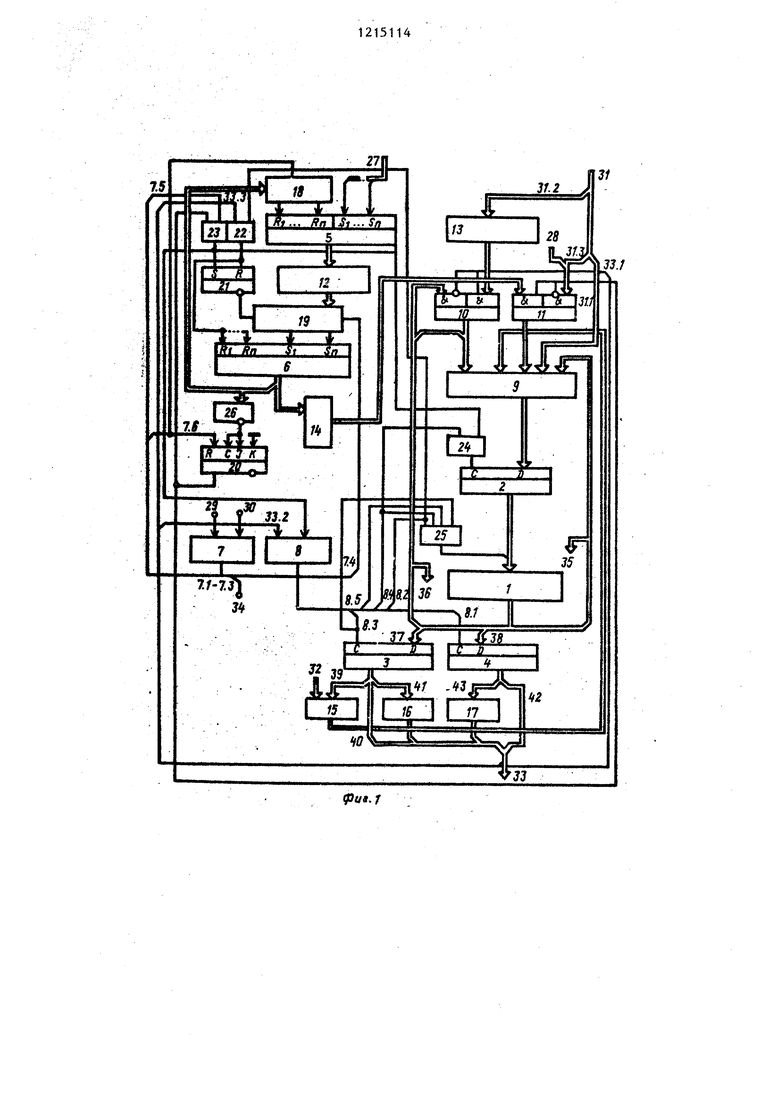

На фиго 1 приведена функциональная схема микропрограммного устройства управления и контроля распределенными объектами; на фиг.2 и 3 jQ соответственно блок-схемы первого и второго блоков синхронизации и временные диаграммы их работы; на фиг.4- блок-схема блока выбора адреса. Микропрограммное устройство- для

JJ контроля и управления распределенными объектами содержит (фиг,1) блок 1 памяти микрокоманд, регистр 2 адреса, первый 3 я второй 4 регистры

3

микроопераций, регистр 5 запросов, буферный регистр 6, первый блок 7 синхронизации, содержащий первый 7,1 - шестой 7.6 выходы, второй блок 8 синхронизации, содержащий соответственно первый 8.1 - пя- тый 8.5 выходы, мультиплексор 9, первый 10 и второй 11 коммутаторы, первый 12 и второй 13 узлы приоритета, шифратор 14, блок 15 выбо- ра адреса, второй 16 и первый 17 дешифраторы, первый 18 и второй 19 блоки ключей, первый 20 и второй 21 триггеры, первый 22 и второй 23 элементы И, первый 24 и второй 25 эле- менты ИЛИ и элемент ШШ-НЕ 26. Кроме того, на фиг.1 показаны вход 27 запросов устройства, вход 28 кодов операций устройства, вход 29 пуска и вход 30 останова уст 1ойства, первый вход 31 логических условий, содержа- 1ЦИЙ первую 31.1, вторую 31.2 и третью 31.3 группы входов, второй вход . 32 логических условий устройства, выходы 33 микроопераций устройства, включая выход 33.1 микрооперации управления ветвлением, выход 33.2 микрооперации Конец режима и выход 33.3 микрооперации установки в исходное состояние буферного регист- ра 6 и второго триггера 21, синхро- выходы 34 устройства, образованные первьтми тремя выходами 7.1 - 7.3 первого блока 7 синхронизации, выход 35 констант устройства и выход 36 расширения констант устройства, информационные входы 37 первого регистра 3 микроопераций, информационные входы 38 второго регистра 4 микроопераций, третья 39, первая 40 и вторая 41 группы выходов логических условий управляющая и адресная первого регисра 3 микроопераций, управляющая 42 и адресная 43 группы выходов второго регистра 4 микроопераций.

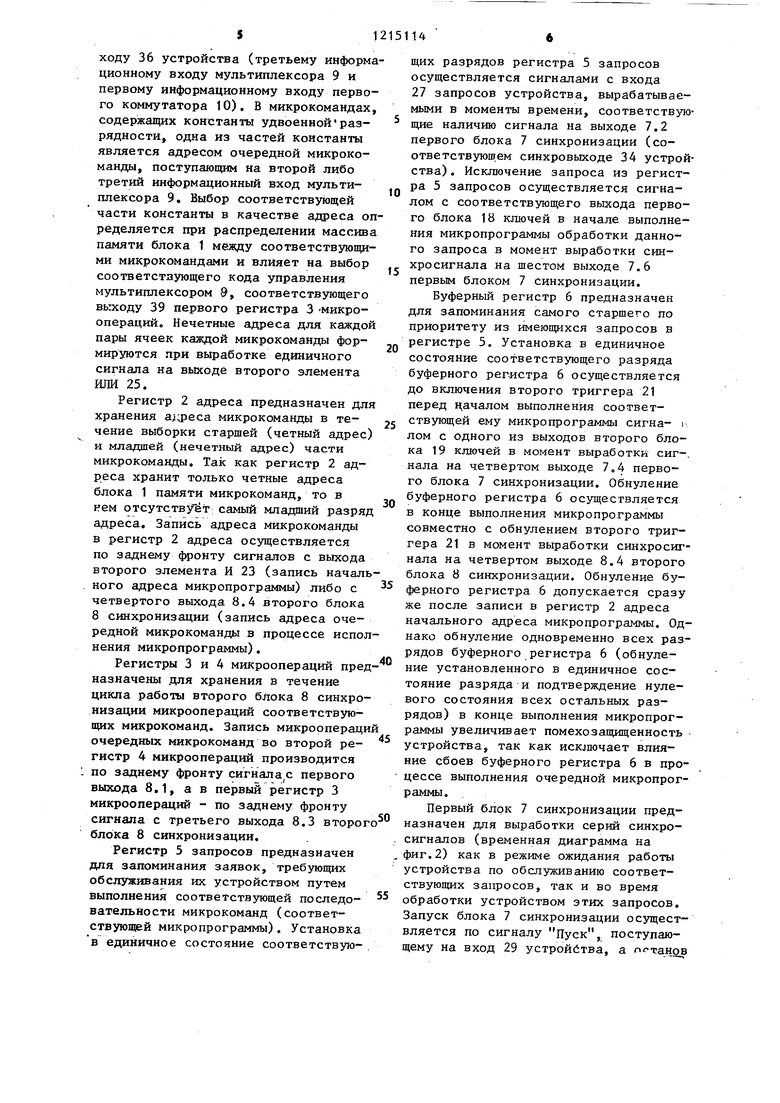

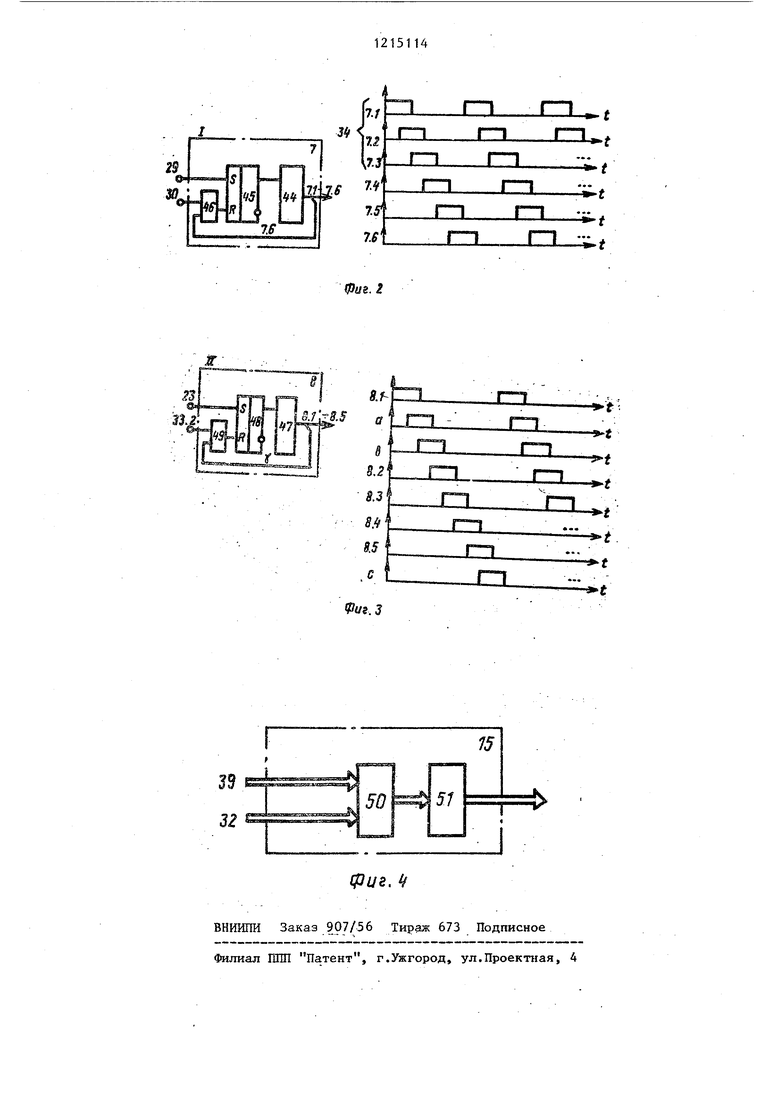

Первый блок 7 синхронизации (фиг.2) содержит генератор 44, триггер 45 и элемент И 46, выход которого подключен к нулевому входу триггера 45. Единичный выход триггера 45 подключен к входу генератора 44, вы- ходы которого образуют выходы 7.1- 7.6 первого блока 7 синхронизации, причем шестой выход 7.6 генератора 44 соединен с первым входом элемента И 46, второй вход которого соединен с втор№1 управляющим входом 30 блока 7. Первый управляющий вход 29 первого блока 7 синхронизации сое

ю )5 20 5 ,

0 5

5

144 ,

динен с единичным входом триггера

45.

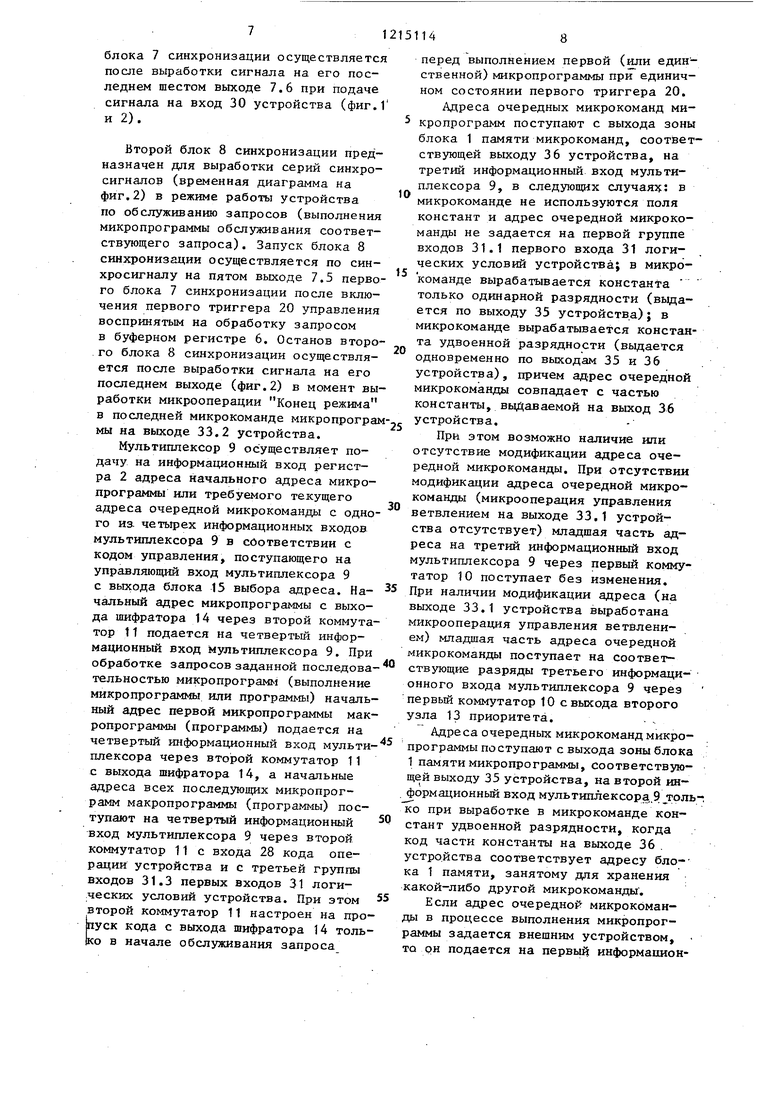

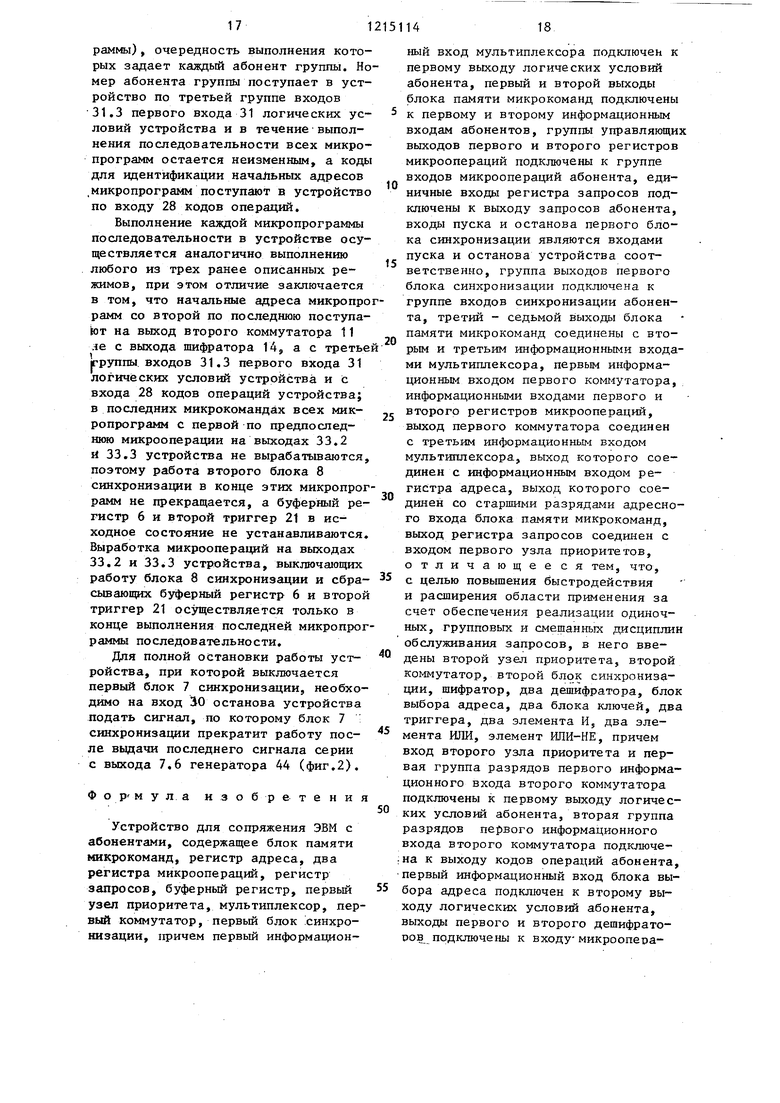

Второй блок 8 синхронизации (фиг.З) содержит генератор 47, триггер 48 и элемент И 49, выход которого соединен с нулевым входом триггера 48. Единичный выход триггера 48 соединен с входом генератора 47. Первый 8.1, второй 8.2, третий 8.3, четвертый 8.4 и пятый 8.5 выходы генератора 47 образуют соответствующие выходы второго блока 8 синхронизации. Выход генератора 47 соединен с первым входом элемента И 49, второй вход которого соединен с первым управляющим входом 33.2 блока 8. Второй управляющий вход второго блока В синхронизации соединен с единичным входом триггера 48.

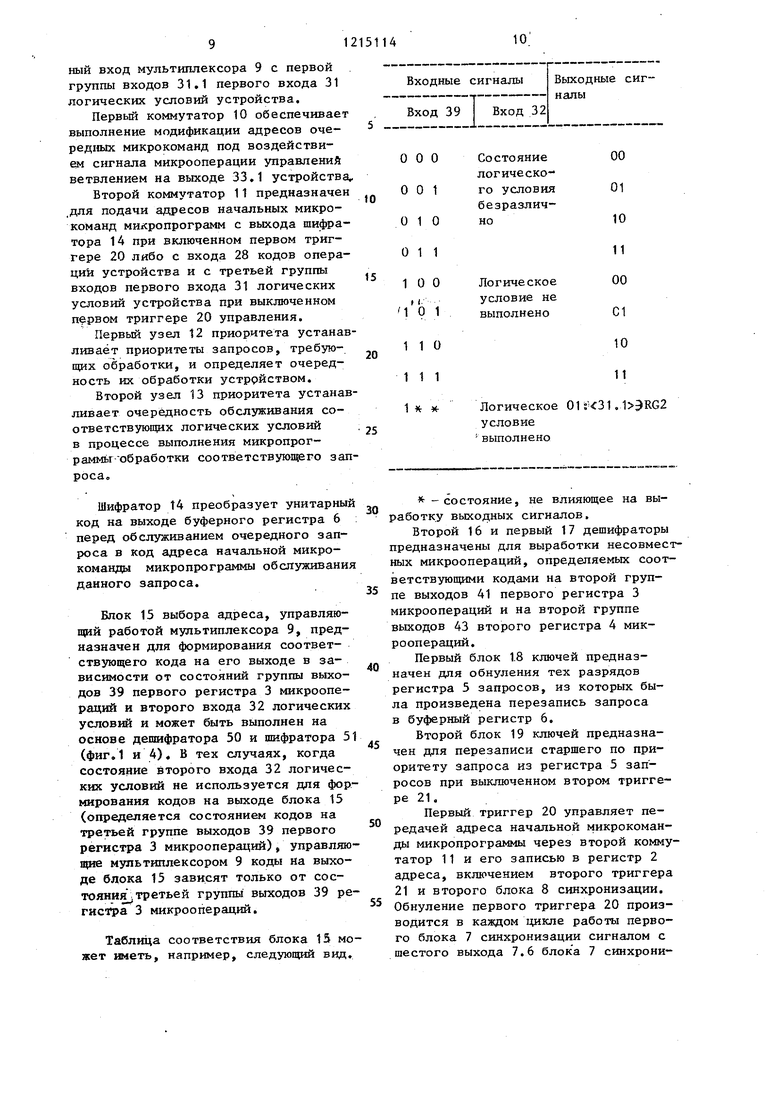

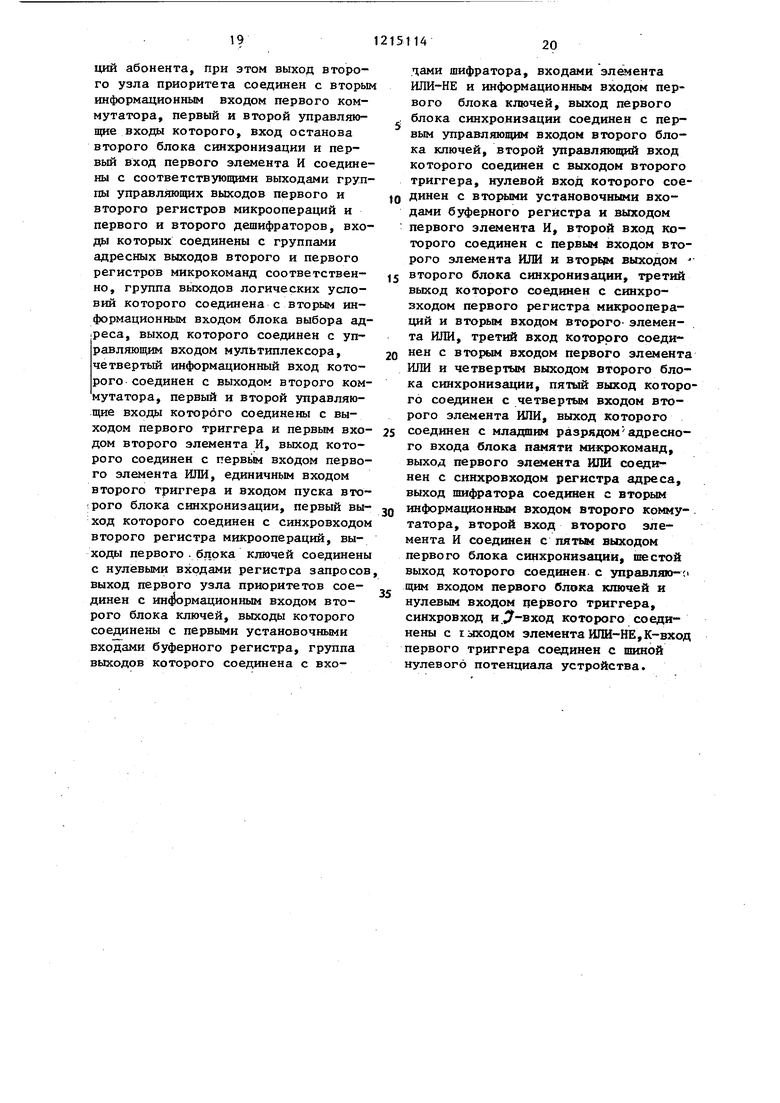

Блок 15 выбора адреса (фиг.4) содержит дешифратор 50 и шифратор 51, выход которого образует выход блока 15. Вторые входы 39 блока 15 соединены с первыми входами дешифратора 50, выходца которого являются входами шифратора 51. Первые входы 32 комбинационного блока соединены с вторыми входами дешифратора 50.

Блок 1 памяти микрокоманд предназначен для запоминания адресов очередных микрокоманд, микроопераций и констант, используемых при выполнении соответствующих микрокоманд. Каждой микрокоманде в блоке 1 памяти микрокоманд соответствует пара смежных ячеек (адресов). В ячейке с четным адресом располагаются только микрооперации операционной части микрокоманды, запоминаемые во втором регистре 4 микроопераций. В ячейке с нечетным адресом располагаются микрооперации операционной части микрокоманды, запоминаеьсые в первом регистре 3 микроопераций, четные адреса очередных микрокоманд и соответствующие микрокомандам константы. При этом константы одинарной разрядности располасаю.тся в зоне блока 1 памяти микрокоманд, соответствующей выходу 35 устройства, а константы удвоенной разрядности располагаются в зонах 1 памяти микрокоманд, соответствующих выходам . 35 и 36 устройства. В микрокомандах, не использующих поля констант блока 1 памяти или использующих константы одинарной разрядности, адрес очередной микрокоманды записывается в зоне блока 1 памяти, соответствующей вы

ходу 36 устройства (третьему информационному входу мультиплексора 9 и первому информационному входу первого коммутатора 10). В микрокомандах, содержащих константы удвоенной раз- рядности, одна из частей константы является адресом очередной микрокоманды, поступающим на второй либо третий информационный вход мультиплексора 9. Выбор соответствующей части константы в качестве адреса определяется при распределении массива памяти блока 1 между соответствующими микрокомандами и влияет на выбор соответствующего кода управления мультиплексором 9, соответствующего вьпсоду 39 первого регистра 3 -микроопераций. Нечетные адреса для каждой пары ячеек каждой микрокоманды формируются при выработке единичного сигнала на выходе второго элемента ИЛИ 25.

Регистр 2 адреса предназначен для хранения а;;реса микрокоманды в те- чение выборки старшей (четный адрес) и младшей (нечетный адрес) части микрокоманды. Так как регистр 2 адреса хранит только четные адреса блока 1 памяти микрокоманд, то в нем отсутству1ёт; самый младший разряд адреса. Запись адреса микрокоманды в регистр 2 адреса осзществляется по заднему фронту сигналов с выхода второго злемента И 23 (запись начального адреса микропрограммы) либо с четвертого выхода 8.4 второго блока 8 синхронизации (запись адреса очередной микрокоманды в процессе исполнения микропрограммы).

Регистры 3 и 4 микроопераций предназначены для хранения в течение цикла работы второго блока 8 синхронизации микроопераций соответствующих микрокоманд. Запись микроопераци очередных микрокоманд во второй регистр 4 микроопераций производится по заднему фронту сигнала с первого выхода 8.1, а в первый регистр 3 микроопераций - по заднему фронту сигнала с третьего выхода 8.3 второг блока 8 синхронизации.

Регистр 5 запросов предназначен для запоминания заявок, требующих обслуживания их устройством путем выполнения соответствующей последо- вательности микрокоманд (соответствующей микропрограммы). Установка в единичное состояние соответствую-

o

5

0

j

0

щих разрядов регистра 5 запросов осуществляется сигналами с входа 27 запросов устройства, вырабатываемыми в моменты времени, соответствующие наличию сигнала на выходе 7.2 первого блока 7 синхронизации (соответствующем синхровыходе 34 устройства) . Исключение запроса из регистра 5 запросов осуществляется сигналом с соответствующего выхода первого блока 18 ключей в начале выполнения микропрограммы обработки данного запроса в момент выработки синхросигнала на шестом выходе 7,6 первым блоком 7 синхронизации.

Буферный регистр 6 предназначен для запоминания самого старшего по приоритету из имеющихся запросов в регистре 5, Установка в единичное состояние соответствующего разряда буферного регистра 6 осуществляется до включения второго триггера 21 перед началом выполнения соответствующей ему микропрограммы сигна- i лом с одного из выходов второго блока 19 ключей в момент выработки сиг-, нала на четвертом выходе 7,4 первого блока 7 синхронизации. Обнуление буферного регистра 6 осуществляется в конце выполнения микропрограммы совместно с обнулением второго триггера 21 в момент выработки синхросигнала на четвертом выходе 8.4 второго блока 8 синхронизации. Обнуление буферного регистра 6 допускается сразу же после записи в регистр 2 адреса начального адреса микропрограммы. Однако обнуление одновременно всех разрядов буферного регистра 6 (обнуление установленного в единичное состояние разряда и подтверждение нулевого состояния всех остальных разрядов) в конце выполнения микропрограммы увеличивает помехозащищенность устройства, так как исключает влияние сбоев буферного регистра 6 в процессе выполнения очередной микропрограммы.

Первый блок 7 синхронизации предназначен для выработки серий синхросигналов (временная диаграмма на фиг.2) как в режиме ожидания работы устройства по обслуживанию соответствующих запросов, так и во время обработки устройством этих запросов. Запуск блока 7 синхронизации осуществляется по сигналу Пуск, поступающему на вход 29 устройства, а о : тан.ов

блока 7 синхронизации осуществляется после выработки сигнала на его последнем шестом выходе 7.6 при подаче сигнала на вход 30 устройства (фиг.1 и 2).

Второй блок 8 синхронизации предназначен для выработки серий синхросигналов (временная диаграмма на фиг.2) в режиме работы устройства по обслуживанию запросов (выполнения микропрограммы обслуживания соответствующего запроса). Запуск блока 8 синхронизации осуществляется по синхросигналу на пятом выходе 7.5 первого блока 7 синхронизации после включения первого триггера 20 управления воспринятым на обработку запросом в буферном регистре 6. Останов второго блока 8 синхронизации осуществляется после выработки сигнала на его последнем выходе (фиг.2) в момент выработки микрооперации Конец режима

в последней микрокоманде микропрограм-, устройства

мы на выходе 33.2 устройства.

Мультиплексор 9 осуществляет подачу на информационный вход регистра 2 адреса начального адреса микропрограммы или требуемого текущего адреса очередной микрокоманды с одного из. четырех информационных входов мультиплексора 9 в соответствии с кодом управления, поступающего на управляющий вход мультиплексора 9 с выхода блока 15 выбора адреса. Начальный адрес микропрограммы с выхода шифратора 14 через второй коммутатор 11 подается на четвертый информационный вход Мультиплексора 9. При

30

35

При этом возможно наличие или отсутствие модификации адреса очередной микрокоманды. При отсутствии модификации адреса очередной микрокоманды (микрооперация управления ветвлением на выходе 33.1 устройства отсутствует) младшая часть адреса на третий информационный вход мультиплексора 9 через первый коммутатор 10 поступает без изменения. При наличии модификации адреса (на выходе 33.1 устройства выработана микрооперация управления ветвлением) младшая часть адреса очередной микрокоманды поступает на соответобработке запросов заданной последова- ствующие разряды третьего информаци- тельностью микропрограмм (выполнение микропрограммы или программы) начальный адрес первой микропрограммы макропрограммы (программы) подается на четвертый информационный вход мульти- плексора через второй коммутатор 11 с выхода шифратора 14, а начальные адреса всех последующих микропрограмм макропрограммы (программы) поступают на четвертый информационный вход мультиплексора 9 через второй коммутатор 11 с входа 28 кода операции устройства и с третьей группы входов 31.3 первых входов 31 логи- .ческих условий устройства. При этом второй коммутатор 11 настроен на пропуск кода с выхода шифратора 14 толь- |ко в начале обслуживания запроса

50

55

онного входа мультиплексора 9 через первый коммутатор 10 с выхода второго узла 13 приоритета.. .

Адре са очередных микрокоманд микропрограммы поступают с выхода зоны блока 1 памяти микропрограммы, соответствующей выходу 35 устройства, на второй информационный вход мультиплексора, оль ко при выработке в микрокоманде констант удвоенной разрядности, когда код части константы на выходе 36 . устройства соответствует адресу бло-- ка 1 памяти, занятому дпя хранения какой-либо другой микрокоманды.

Если адрес очередно микрокоманды в процессе выполнения микропрограммы задается внешним устройством, TQ он подается на первый информапион

10

2151148

перед выполнением первой (или единственной) микропрограммы при единичном состоянии первого триггера 20.

Адреса очередных микрокоманд микропрограмм поступают с выхода зоны блока 1 памяти микрокоманд, соответствующей выходу 36 устройства, на третий информационный вход мультиплексора 9, в следующих случаях: в микрокоманде не используются поля констант и адрес очередной микрокоманды не задается на первой группе входов 31.1 первого входа 31 логи- . ческих условий устройства; в микрокоманде вырабатывается константа только одинарной разрядности (вьща- ется по выходу 35 устройства)j в микрокоманде вырабатывается константа удвоенной разрядности (вьщается одновременно по выходам 35 и 36 устройства), причем ад рес очередной микрокоманды совпадает с частью

J5

20

константы, выдаваемой на выход 36

устройства

При этом возможно наличие или отсутствие модификации адреса очередной микрокоманды. При отсутствии модификации адреса очередной микрокоманды (микрооперация управления ветвлением на выходе 33.1 устройства отсутствует) младшая часть адреса на третий информационный вход мультиплексора 9 через первый коммутатор 10 поступает без изменения. При наличии модификации адреса (на выходе 33.1 устройства выработана микрооперация управления ветвлением) младшая часть адреса очередной микрокоманды поступает на соответ ствующие разряды третьего информаци-

0

5

онного входа мультиплексора 9 через первый коммутатор 10 с выхода второго узла 13 приоритета.. .

Адре са очередных микрокоманд микропрограммы поступают с выхода зоны блока 1 памяти микропрограммы, соответствующей выходу 35 устройства, на второй информационный вход мультиплексора, оль-: ко при выработке в микрокоманде констант удвоенной разрядности, когда код части константы на выходе 36 . устройства соответствует адресу бло-- ка 1 памяти, занятому дпя хранения какой-либо другой микрокоманды.

Если адрес очередно микрокоманды в процессе выполнения микропрограммы задается внешним устройством, TQ он подается на первый информапионный вход мультиплексора 9 с первой группы входов 31.1 первого входа 31 логических условий устройства.

Первый коммутатор 10 обеспечивает выполнение модификации адресов очередных микрокоманд под воздействием сигнала микрооперации управлений ветвлением на выходе 33.1 устройства

Второй коммутатор 11 предназначен .для подачи адресов начальных микрокоманд микропрограмм с выхода шифратора 14 при включенном первом триггере 20 либо с входа 28 кодов операции устройства и с третьей группы входов первого входа 31 логических условий устройства при выключенном первом триггере 20 управления.

Первый узел 12 приоритета устанавливает приоритеты запросов, требующих обработки, и определяет очередность их обработки устройством.

Второй узел 13 приоритета устанавливает очерёдность обслуживания соответствующих логических условий в процессе выполнения микропрог- раммьг Обработки соответствующего запроса.

Шифратор 14 преобразует унитарный код на выходе буферного регистра 6 перед обслуживанием очередного запроса в код адреса начальной микрокомандою микропрограммы обслуживания данного запроса.

Блок 15 выбора адреса, управляющий работой мультиплексора 9, предназначен для формирования соответствующего кода на его выходе в зависимости от состояний группы выходов 39 первого регистра 3 микроопераций и второго входа 32 логических условий и может быть выполнен на основе депшфратора 50 и шифратора 51 (фиг,1 и 4), В тех случаях, когда состояние второго входа 32 логических условий не используется для формирования кодов на выходе блока 15 (определяется состоянием кодов на третьей группе выходов 39 первого регистра 3 микроопераций), управляющие мультиплексором 9 коды на выходе блока 13 зависят только от сос- TOHHHHjтретьеи группы выходов 39 ре- гис-гра 3 микроопераций.

Таблица соответствия блока 15 может иметь, например, следующий вид.

000

о о 1 о 1 о о 1 1

Состояние логического условия безразлично

1 1 1

1 Ч

00 01 10

11

00 С1 10

11

Логическое 01 . условие выполнено

-состояние, не влияющее на выработку выходных сигналов.

Второй 16 и первый 17 дешифраторы предназначены для выработки несовместных микроопераций, определяемых соответствующими кодами на второй группе выходов 41 первого регистра 3 микроопераций и на второй группе выходов 43 второго регистра 4 микроопераций.

Первый блок 1.8 ключей предназначен для обнуления тех разрядов регистра 5 запросов, из которых была произведена перезапись запроса в буферный регистр 6.

Второй блок 19 ключей предназначен для перезаписи старшего по приоритету запроса из регистра 5 запросов при выключенном втором триггере 21.

Первый триггер 20 управляет передачей адреса начальной микрокоманды микропрограммы через второй коммутатор 11 и его записью в регистр 2 адреса, включением второго триггера 21 и второго блока 8 синхронизации. Обнуление первого триггера 20 производится в каждом цикле работы первого блока 7 синхронизации сигналом с шестого выхода 7.6 блок а 7 синхрони

зации. Установка в единичное состояние первого триггера 20 производится перепадом Сигнала с высокого на низкий уровень на выходе элемента ИЛИ-НЕ 26 в момент записи любого запроса в буфер- ный регистр 6,

Второй триггер 21 предназначен для блокировки записи запросов более старших приоритетов, поступивших в регистр 5 запросов после записи соответствукяцего запроса в буферный регистр 6 и начала его обработки. Установка второго триггера 21 в единичное состояние происходит сигналом с пятого выхода 7.5 первого блока 7 синхронизации при включенном первом триггере 20. Обнуление второго триггера 21 происходит в конце микропрограммы обработки соответствующего запроса сигналом с четвертого выхода 8,4 второго блока 8 синхронизации по микрооперации, подаваемой с выхода 33.3 устройства на первый вход первого элемента И 22

Первый элемент И 22 предназначен для выработки сигнала обнуления буферного регистра 6 и второго триггера 21 в конце микропрограммы обработки соответствующего запроса.

Второй элемент И 23 предназначен для выработки сигнала включения второго блока 8 синхронизации и второго триггера 21, а также для записи адреса начальной микрокоманды микропрограммы в регистр 2 адреса.

Первый элемент ИЛИ 24 объединяет сигналы записи адресов микрокоманд в регистр 2 адреса.

Второй элемент ИЛИ 25 предназначен для формирования сигнала младше- го разряда адреса блока 1 памяти микрокоманд (нечетный адрес при вырботке сигнала на выходе второго элемента ИЛИ 25) из выходных сигналов второго блока 8 синхронизации.

Элемент ИЛИ-НЕ 26 предназначен для формирования низкого уровня сигнала при наличии сигнала на любом выходе буферного регистра 6.

Запросы на обслуживание соответ- абонентов поступают на входы регистра 5 запросов по входу 27 запросов устройства.

При обслуживании групп абонентов, требующих выполнения макропрограмм (последовательностей микропрограмм, определяемых особенностями соответствующих абонентов) адреса началь0

5

5

5

ных микрокоманд второй и последующих микропрограмм последовательности поступают в устройство по входу 28 кода операции, при этом номер соответствующего абонента группы задается кодом на третьей группе входов 31.3 первого входа 31 логических условий устройства, на вторую группу входов 31.2 которого подаются логические условия, вырабатываемые соответствующими абонентами и требующие обслуживания в соответствии с установленными приоритетами при выполнении микропрограмм обслуживания соответствующих запросов. Данные логические условия, модифицируя адрес очередной микрокоманды, определяют выбор одной из альтернативных последовательностей микрокоманд ветвящихся микропрограмм обслуживания соответствующих запросов. Для абонентов, последовательность выполнения микрокоманд которых определяется в зависимости от вырабатываемых в- них логических условий как адресами микрокоманд, хранимых в блоке 1 памяти микрокоманд, так и адресами, формируемыми самими абонентами, сигналы их логических условий подаются на второй вход блока 15 по второму входу 32 логических условий устройства, а адреса микрокоманд, формируемые абонентами, подаются на первую группу входов 31,1 первого входа 31 логических условий устройства.

Микрооперации, вырабатываемые устройством для обслуживания и управления работой внешних абонентов и для управления работой самого устройства, подаются на выход 33 устройства с выходов дешифраторов 16 и 17 и с соответствующих выходов регистров 3 и 4 микроопераций.

Дпя синхронизации взаимной работы устройства и внешних абонентов синхросигналы, вырабатываемые на выходах 7.1 - 7.3 первого блока 7 синхронизации, подаются на синхровыхо- ды 34 устройства.

Константы, вырабатываемые в соответствующих микрокомандах дпя вьэда- чи на абоненты при обработке их запросов на обслуживание, подаются на входы абонентов через выход 35 констант устройства и 36 рас- . ширения констант устройства.

Работу устройства рассмотрим в четырех режимах обслуживания эапросов абонентов, которые определяют классы обслуживаемых абонентов.

1, Обслуживание одиночных абонентов, требующих выполнения линейной последовательности микрокоманд.

В исходном состоянии регистры 3 - 6 и триггеры 20 и 21 обнулены и на выход 33 устройства не вьщают- ся сигналы микроопераций, триггер .48 второго блока 8 синхронизации выключен и на выходах генератора 47 и соответственно выходах блока 8 синхронизации синхросигналы не вы- рабатьшаются. При нулевом состоянии буферного регистра 6 на выходе элемента ИПИ-НЕ 26 установлен высокий уровень сигнала.

Первый блок 7 синхронизации, запущенный триггером 46, включенным по сигналу пуска устройства по входу 29, вьщает на выходы 7.1 - 7.6 серии синхросигналов, первые три из которых выдаются на синхровыход 34 устройства, а последний подтверждае исходное состояние первого триггера 20 управления. Сигналы на синхровы- ходе 34 устройства необходимы для согласования работы устройства с работой абонентов по выдаче запросов на обслуживание, поэтому выдача данных запросов совпадает с моментами времени выработки синхросигнала на выходе 7.2 блока 7 синхронизации.

При поступлений запросов в регистр 5 по входу 27 запросов устройства они запоминаются и первый узел 12 приоритетов выбирает старший из них по приоритету. Так как второй триггер 21 сброшен, указанный запрос с выхода узла 12 приоритета через второй блок 19 ключей в момент выработки сигнала на выход 7.4 первого блока 7 синхронизации записывается в буферный регистр 6. В момент перезаписи запроса в буферный регистр 6 (передний фронт сигнала на выходе 7.4 блока 7 синхронизации) на выходе элемента ИЖ-НЕ 26 появляется перепад сигнала из высокого уровня в низкий и первый триггер 20 устанавливается в единичное состояние, настраивая второй коммутатор 11 на пропуск кода адреса первой микрокоманды с выхода шифратора 14 (на выходе шифратора 14 выработан код, идентифицирующий соответствующий запрос, находящийся в буферном регистре 6) на чет0

5

0

вертый информационный вход мультиплексора 9, который в исходном состоянии всегда настроен кодом с выхода преобразователя 15 на пропуск информации с выхода второго коммутатора 11 на информационный вход регистра 2 адреса. Далее по сигналу на выходе 7,6 блока 7 синхронизации производится исключение из регистра

5запроса, попавшего в буферный регистр 6 для обслуживания.

При единичном состоянии первого триггера 20 синхросигнал с выхода 7.5 первого блока 7 синхронизации обеспечивает выработку сигнала на выходе второго элемента И 23, некоторому прозводится запись адреса начальной микрокоманды микропрограммы обслуживания запроса абонента в регистр 2 адреса, включение второго триггера 21 и запуск второго блока 8 синхронизации, которьш начинает выдавать серии синхросигналов на своих выходах (фиг.З). При включенном состоянии второго триггера 21 блокируется запись в буферный регистр

6запросов более старших- по приоритету, если они поступают в регистр

5 запросов.

В течение первой фазы работы блока 8 синхронизации сигнал на выходе второго элемента ИЛИ 25 отсутствует и операционная часть микрокоманды,

5 выбранная из блока 1 памяти по адресу, установленному в регистре 2 адреса, запишется во второй регистр 4 микроопераций сигналом на выходе 8,1 блока 8 синхронизации. Во второй фазе работы блока 8 синхронизации (выработка сигналов на выходах 8.2- 8.5 блока 8) на адресном входе блока 1 памяти установлен нечетный адрес ячейки блока 1 памяти, информация с которой поступает на информационный вход 37 первого регистра 3 микроопераций (операционная .часть микрокоманды, записьюаемая в регистр 3 сигналом с выхода 8,3 второго блока 8

синхронизации), на выходы 35 и 36 (при необходимости вьщачи констант абонентам) и на второй и третий информационные входы мультиплексора 9. Причем, так как для данного класса абонентов не производится ветвление микропрограмм, младшая часть адреса очередной микрокоманды на третий информационный вход мультиплексора 9 поступает через первый коммутатор 10 без изменения.

Несовместимые микрооперации с выходов дешифраторов 16 и 17 и совместимые микрооперации с выходов 40 и регистров 3 и 4 микроопераций первой микрокоманды, считанной из блока 1 памяти, выдаются на выход 33 устройства для управления работой обслуживаемого абонента. Для абонентов рассматриваемого класса код управления мультиплексором 9 на выходе блока 15 зависит только от состояния выходов 39 регистра 3, поэтому адрес очередной микрокоманды задан на третьем (втором) информационном входе, мультиплексора 9 (особенности формирования адреса очередной микрокоманды на втором входе мультиплексора 9 описаны выше) . Работа устройства по выдаче синалов на его выход 33 в дальнейшем аналогична описанному первому циклу работы блока 8 синхронизации с той лишь разницей; что адреса очередных микрокоманд поступают на третий (второй) информационный вход мультиплексора, а запись этого адреса в регистр 2 адреса осуществляется по сигналам с выхода 8.4 второго блока 8 синхронизации. В конце выполнения данного режима в последней микрокоманде вырабатъшаются. сигналы микроопераций на выходах 33.2 и 33.3 устройства, по которым произ- .водится останов второго блока 8 синхронизации и установка в исходное состояние буферного регистра 6 и второго триггера 21.

2. Обслуживсшие одиночных абонентов, требующих в ходе выполнения микропрограммы обслуживания изменения последовательности микрокоманд в зависимости от логических условий выработанных абонентами и выданных в устройство по второму входу 32 логических условий, причем адреса очередных микрокоманд в точках изменения последовательности микрокоманд микропрограммы задаются абонентами и поступают в устройство по первой группе входов 31.1 первого входа 31 логш/еских условий устройства.

Отличие работы устройства в данном режиме от ранее описанного заключается в том, что в микрокомандах последовательности на выходе 39

регистра 3 микроопераций вырабатывается код проверки логических условий, поступающих в устройство по входу 32. Таким образом, в зависимости от значений упомянутых логических условий на выходе блока 15 вырабатывается код, обеспечивающий передачу через мультиплексор 9 адреса очередной микрокоманды на информационный вход регистра 2 адреса либо с выхода блока 1 памяти микрокоманд, либо с первой группы входов 31.1 первого входа 31 логических условий при изменении последовательности выполнения микрокоманд микро- программы.

3.Обслуживание абонентов, объединенных в группу, вырабатыванщую единый запрос дпя обслуживания всех абонентов группы, либо обслуживание одного абонента, вырабатывающего группу логических условий, каждое из которых должно быть обслужено

в соответствии со своим приоритетом. Отличие работы устройства в данном режиме от режима, описанного первым, состоит в том, что в микрокомандах опроса логических условий, которые подаются на вход второго узла 13 приоритета через вторую группу входов 31.2 первого входа 31 логических условий устройства, адрес очередной микрокоманды подается на третий информационный вход мультиплексора 9. Устройство вырабатывает микрооперацию управления ветвлением на своем вь-ходе 33.1, по которой младшая часть адреса на третий информационный вход мультиплексора 9 подается через первый коммутатор 10 с выхода второго узла 13 приоритета. После обслуживания последнего логического условия (абонента) групгш на вькоде узла 13 приоритета выраба- тьшается нулевой код, а микрокоманда с нулевыми младшими разрядами адреса на выходе коммутатора 10 свидетельствует об окончаний обслуживания опрашиваеьилх логических условий (исключение абонентами соответствующих логических условий в процессе их обслуживания производится по микрооперациям на выходе 33 устройства) .

4.Обслуживание групп абонентов, требующих выполнения не одной микропрограммы, а последовательности микропрограмм (программы или макропрограммы), очередность выполнения которых задает каждый абонент группы. Номер абонента группы поступает в устройство по третьей группе входов 31.3 первого входа 31 логических условий устройства и в течение выполнения последовательности всех микропрограмм остается неизменным, а коды для идентификации начальных адресов .микропрограмм поступают в устройство по входу 28 кодов операций.

Выполнение каждой микропрограммы последовательности в устройстве осуществляется аналогично выполнению любого из трех ранее описанных режимов, при этом отличие заключается в том, что начальные адреса микропро рамм со второй по последнюю поступа- koT на выход второго коммутатора 11 ле с выхода шифратора 14, а с третье грзшпы входов 31.3 первого входа 31 логических услов1й устройства и с входа 28 кодов операций устройства; в последних микрокомандах всех микропрограмм с первой по предпоследнюю микрооперации на выходах 33.2 и 33.3 устройства не вырабатъшаются, поэтому работа второго блока 8 синхронизации в конце этих микропрограмм не прекращается, а буферный регистр 6 и второй триггер 21 в исходное состояние не устанавливаются. Выработка микроопераций на выходах 33,2 и 33,3 устройства, выключающих работу блока 8 синхронизации и сбра- сьшаюпрсс буферный регистр 6 и второй триггер 21 осуществляется только в конце выполнения последней микропрограммы последовательности.

Для полной остановки работы устройства, при которой выключается первый блок 7 синхронизации, необходимо на вход 30 останова устройства подать сигнал, по которому блок 7 синхронизахщи прекратит работу после выдачи последнего сигнала серии с выхода 7,6 генератора 44 (фиг,2).

Фор мула изобретения

Устройство для сопряжения ЭВМ с абонентами, содержащее блок памяти микрокоманд, регистр адреса, два регистра микроопераций, регистр запросов, буферный регистр, первый узел приоритета, мультиплексор, первый коммутатор, первый блок синхро- низации, 1фичем первый информацион

to

15

20

25

30

35

40

45

50

55

ный вход мультиплексора подключен к первому выходу логических условий абонента, первый и второй выходы блока памяти микрокоманд подключены к первому и второму информационным входам абонентов, группы управляющих выходов первого и второго регистров микроопераций подключены к группе входов микроопераций абонента, единичные входы регистра запросов подключены к выходу запросов абонента, входы пуска и останова первого блока синхронизации являются входами пуска и останова устройства соответственно, группа выходов первого блока синхронизации подключена к группе входов синхронизации абонента, третий - седьмой выходы блока памяти микрокоманд соединены с вторым и третьим информационными входами мультиплексора, первым информационным входом первого коммутатора, информационньми входами первого и второго регистров микроопераций, выход первого коммутатора соединен с третьим информационным входом мультиплексора, выход которого соединен с информационным входом регистра адреса, выход которого соединен со старшими разрядами адресного входа блока памяти микрокоманд, выход регистра запросов соединен с входом первого узла приоритетов, отличающееся тем, что, с целью повышения быстродействия и расширения области применения за счет обеспечения реализации одиночных, групповых и смешанных дисциплин обслуживания запросов, в него введены второй узел приоритета, второй коммутатор, второй блок синхронизации, шифратор, два дешифратора, блок выбора адреса, два блока ключей, два триггера, два элемента И, два элемента ШШ, элемент ИПИ-НЕ, причем вход второго узла приоритета и первая группа разрядов первого информационного входа второго коммутатора подключены к первому выходу логических условий абонента, вторая группа разрядов первого информационного входа второго коммутатора подключе- ;На к выходу кодов операций абонента, первый информационный вход блока выбора адреса подключен к второму выходу логических условий абонента, выходы первого и второго дешифраторов подключены к входу микроопераций абонента, при этом выход второго узла приоритета соединен с вторым информационным входом первого коммутатора, первый и второй управляю- щие входы которого, вход останова второго блока синхронизации и первый вход первого элемента И соединены с соответствующими выходами группы управляюпщх выходов первого и второго регистров микроопераций и первого и второго дешифраторов, вхо- ды которых соединены с группами адресных выходов второго и первого регистров микрокоманд соответствен- но, группа выходов логических условий которого соединена с вторым информационным входом блока выбора адреса, выход которого соединен с управляющим входом мультиплексора, четвертый информационный вход которого соединен с выходом второго коммутатора, первый и второй управляющие входы которого соединены с выходом первого триггера и первым вхо- дом второго элемента И, выход которого соединен с первьм входом первого элемента ИЛИ, единичньм входом второго триггера и входом пуска второго блока синхронизации, первый вы- ход которого соединен с синхровходом второго регистра микроопераций, выходы первого . блрка ключей соединены с нулевыми входами регистра запросов выход первого узла приоритетов соединен с ин(рмационным входом второго блока ключей, выходы которого соединены с первыми установочными входами буферного регистра, группа выходов которого соединена с вхо

, Q j 20 25 Q

5

дами шифратора, входами элемента ИЛИ-НЕ и информационным входом первого блока ключей, выход первого блока синхронизации соединен с первым управляющим входом второго блока ключей, второй управляющий вход которого соединен с выходом второго триггера, нулевой вход которого соединен с ВТО1Н11МИ установочными входами буферного регистра и выходом первого элемента И, второй вход которого соединен с первым входом второго элемента ИЛИ и вторьгм выходом второго блока синхронизации, третий выход которого соединен с синхро- зходом первого регистра микроопераций и вторым входом второго- элемента ИЛИ, третий вход которого соединен с вторым входом первого элемента ИЛИ и четвертым выходом второго блока синхронизации, пятый выход которого соединен с четвертым входом второго элемента ИЛИ, выход которого соединен с млада1им разрядом адресного входа блока памяти микрокоманд, выход первого элемента ИЛИ соединен с синхровходом регистра адреса, выход шифратора соединен с вторым информационным входом второго комму- , татора, второй вход второго элемента И соединен с пятьм выходом первого блока синхронизации, шестой выход которого соединен, с управляю-с 1 щим входом первого блока ключей и нулевым входом первого триггера, синхровход иv -вход которого соединены с 1ЫХОДОМ элемента ИПИ-НЕ,К-вход первого триггера соединен с шиной нулевого потенциала устройства.

J/

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах управления и код1троля распределенных цифровых систем и ЭВМ. Целью изобретения является повьппение быс- тродействия и расщирение области применения путем обеспечения реализации одиночных, групповых и смешанных дисциплин обслуживания запросов от абонентов. Устройство содержит блок памяти, микрокоманд, регистр адреса, два регистр микроопераций, регистр запросов, буферный регистр, два блока синхронизации, мультиплексор, два коммутатора, два узла приоритетов, шифратор, блок выбора адреса, два дешифратора, два блока клточей; два триггера, два элемента И, два элемента ИЖ, элемент ИЛИ-НЕ. 4 ил.

| Устройство для диагностики и испытаний электронной вычислительной машины | 1979 |

|

SU883909A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мик Дж., Врик Дж | |||

| Проектирование микропроцессорных устройств с раз- рядно-модульной организацией | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Мир, 1984, с.43-44, рис.2.6. | |||

Авторы

Даты

1986-02-28—Публикация

1984-08-02—Подача