Изобретение относится к электронной измерительной технике, в частности к электрон ным аналоговым интеграторам длительных процессов, и может быть использовано, например, в кулонометрии с контролируемым потен циалом.

Известны электронные аналоговые интеграторы, работа которых основана на использовании решающих усилителей с емкостной обратной связью. В этих усилителях сначала интегрируют измеряемый (входной) сигнал, а затем компеисационный сигнал или сумму входного и компенсационного сигналов 1.

Недостатками этих интеграторов являются перерывы в интегрироваиии входного сигнала и недостаточно высокая точность.

Наиболее близким к предлагаемому является аналоговый интегратор, содержащий интегрирующий рещающий усилитель, источник компенсирующего (эталонного) напряжения, гистерезисное переключающее устройство и суммирующий хронометр 2.

Недостатком известного интегратора является возрастание погрещности интегрирования при уменьшении величины входного напряжения. Это особенно существенно при использовании интегратора в кулонометрии с контролируемым потенциалом, в котором подлежащий интегрированию сигнал экспоненциально уменьщается во времени. Недостаток обусловлен тем, что уровни проинтегржрованного сигнала (напряжение на выходе усилителя), соответствующие моментам включения и выключения источника компенсирующе10го напряжения, постоянны я определяются только величиной гистерезиса переключающего устршства (его уровнями срабатывания и опускания). Поэтому длительность каждого о1дельного цикла интегрирования, состоящего из

IS интегрирования входного напряжения и последующего интегрирования суммы входного и компенсирующего напряжений, зависит от величины входного напряжения, увеличиваясь при уменьщешш последнего. Увеличение же

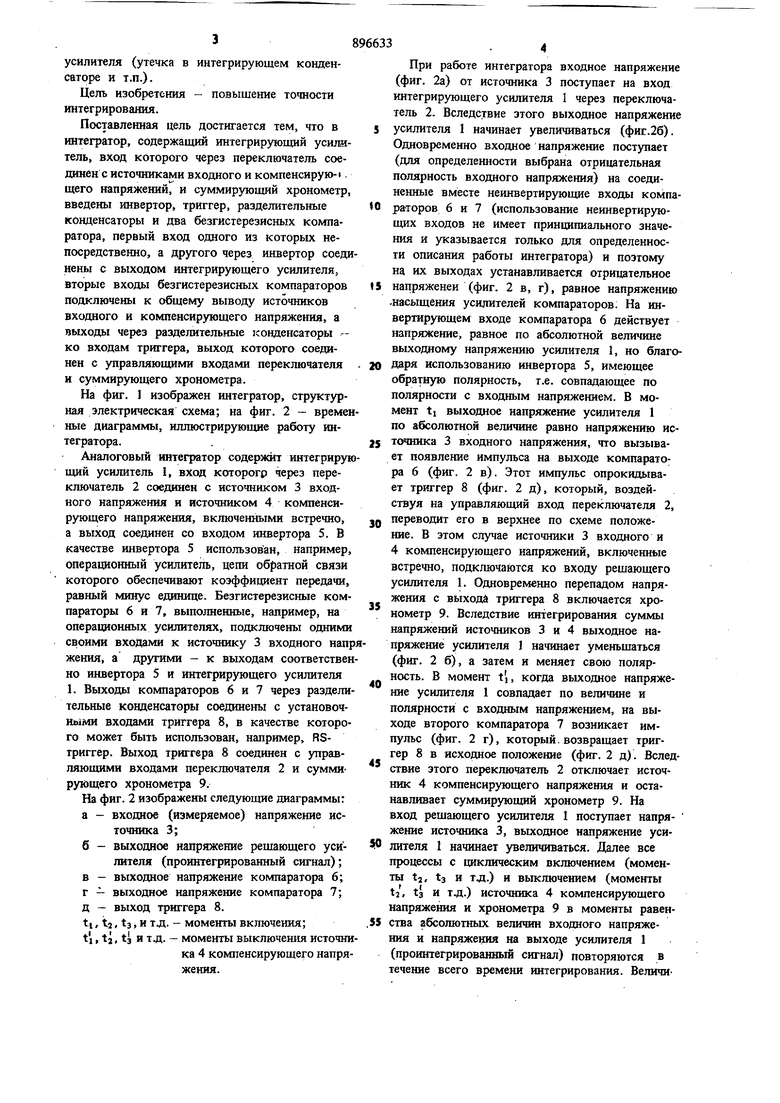

30 длительности отдельного цикла интегрирования приводит к соответствующему увеличению погрешности вследствие конечного значения эквивалентной постоянной времени решающего усилителя (утечка в интегрирующем конденсаторе и т.п.)Цель изобретения - повышение точности интегрировашм. Поставленная цель достигается тем, что в интегратор, содержащий интегрирующий усилитель, вход которого через переключатель соединен с источниками входного и компенсирую-i щего напряжений, и суммирующий хронометр, введены инвертор, триггер, разделительные конденсаторы и два безгистерезисных компаратора, первый вход одного из которых непосредственно, а другого через инвертор соеди нены с выходом интегрирующего усилителя, вторые входы безгистерезисных компараторов подключены к общему выводу источников входного и компенсирующего напряжения, а выходы через разделительные конденсаторы -ко входам триггера, выход которого соединен с управляющими входами переключателя и суммирзоощего хронометра. На фиг. изображен интегратор, структурная электрическая схема; на фиг. 2 - времен ные диаграммы, иллюстрирующие работу интегратора. Аналоговый интегратор содержит интегрирую щий усилитель i, вход которогр через переключатель 2 соединен с источником 3 входного напряжения и источником 4 компенсирующего напряжения, включенными встречно, а выход соединен со входом инвертора 5. В качестве инвертора 5 использован, например, операционный усилитель, цепи обратной связи которого обеспечивают коэффициент передачи, равный минус единице. Безгистерезисные компараторы 6 и 7, выполненные, например, на операционных усилителях, подключены одними своими входами к источнику 3 входного напр жения, а другими - к выходам соответствен но инвертора 5 и интегрирующего усилителя 1. Выходы компараторов 6 и 7 через раздели тельные конденсаторы соединены с установочными входами триггера 8, в качестве которого может быть использован, например, RSтриггер. Выход триггера 8 соединен с управляющими входами переключателя 2 и суммирующего хронометра 9. На фиг. 2 изображены следующие диаграммы: а - входное (измеряемое) напряжение источника 3; б - выходное напряжение решающего усилителя (проинтегрированный сигнал); в - выходное напряжение компаратора 6; г - выходное напряжение компаратора 7; д - выход триггера 8. , t3, и т д. - моменты включения; tl. tj. ts и т.д. - моменты выключения источни ка 4 компенсирующего напря жения. При работе интегратора входное напряжение (фиг. 2а) от источника 3 поступает на вход интегрирующего усилителя 1 через переключатель 2. Вследствие зтого выходное напряжение усилителя 1 начинает увеличиваться (фиг.2б). Одновременно входное напряжение поступает (для определенности выбрана отрицательная полярность входного напряжения) на соединенные вместе неинвертирующие входы компараторов 6 и 7 (использование неинвертируюпщх входов не имеет принципиального значения и указывается только для определенности описания работы интегратора) и позтому на их выходах устанавливается отрицательное нацряженеи (фиг. 2 в, г), равное напряжению насыщения усилителей компараторов; На инвертирующем входе компаратора 6 действует напряжение, равное по абсолютной величине выходному напряжению усилителя 1, но благодаря использованию инвертора 5, имеющее обратную полярность, т.е. совпадающее по полярности с входным напряжением. В момент ti выходное напряжение усилителя 1 по абсолютной величине равно напряжению источника 3 входного напряжения, что вызывает появление импульса на выходе компаратора 6 (фиг. 2 в). Этот импульс опрокидывает триггер 8 (фиг. 2 д), который, воздействуя на управляющий вход переключателя 2, переводит его в верхнее по схеме положевме. В этом случае источники 3 входного и 4 компенсирующего напряжений, включенные встречно, подключаются ко входу решающего усилителя 1. Одновременно перепадом напряжения с выхода триггера 8 включается хронометр 9. Вследствие интегрирования суммы напряжений источников 3 и 4 выходное напряжение усилшеля начинает уменьпгаться (фиг. 2 б), а затем и меняет свою полярность. В момент ti, когда выходное напряжение усилителя 1 совпадает по величине и полярности с входным напряжением, на выходе второго компаратора 7 возникает импульс (фиг. 2 г), который. возвращает триггер 8 в исходное положение (фиг. 2 д). Вследствие зтого переключатель 2 отключает источник 4 компенсирующего напряжения и останавливает суммирующий хронометр 9. На вход решающего усилителя 1 поступает напряжение источника 3, выходное напряжение усилителя 1 начинает увеличиваться. Далее все процессы с циклическим включением (моменты tj. ta и т.д.) и выключением (моменты tj, ta и т.д.) источника 4 компенсирующего напряжения и хронометра 9 в моменты равенства абсолютных величин входного напряжения и напряжения на выходе усилителя 1 (проинтегрированный сигнал) повторяются в течение всего времени интегрирования. ВеличН

на интеграла оценивается по суммарной продолжительности включения источника 4 компенсирующего напряжения, измеряемой суммирующим хронометром 9.

Преимуществом предлагаемого аналогового интегратора является сзшхественно меньшая погрещность при интегрировании входных напряжений, изменяющихся в щироком диапазоне величин. Это основано на том, что уровни проинтегрированного сигнала равны (по абсолютной величине) входному напряжению. Вследствие этого длительность отдельного иикла интегрирования не увеличивается пря . уменьшении величины входного напряжения и поэтому погрещность ннтегрирования, определяемая конечной величиной эквивалентной постоянной времени решающего усилителя, в частности утечкой в интегрирующем конденсаторе, остается практически неизменной при уменьшении входного напряжения.

Формула изобретения

Аналоговый интегратор, содержащий интегрирующий усилитель, вход которого через

переключатель соединен с источниками входного и компенсирующего напряжений, и суммирующий хронометр, отлнчаюшяйс я тем, что, с целью повышенмя точноста интегрирования, в него введены инвертор, триггер, разделительные конденсаторы и ли безгистерезисных ксммпаратора, первый хоа одного из которых непосредственно, щ угого через инвертор соединен с выходом интегрирующего усилителя, вторые входы .безгистерезисных компараторов подключим к общему вьтояу источников входного к компенсирующего напряжений, а выходы через разделительные конденсаторы - ко входам триггера, выход которого соединен с управляющими входами переключателя и суммирующего хронометра.

Источники информации, принятые во внимание при экспертизе

1.Махнанов В. Д. Мнлохин М. Т. Устройства частотного и время-импульсного иреобразования. М., Энергия, 1970, с. 107-112, 115119.

2.Авторское свидетельство СССР N 374618, кл. СгОб Or7/186, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый интегратор | 1980 |

|

SU896634A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2014 |

|

RU2571618C1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР НАПРЯЖЕНИЯ | 2014 |

|

RU2571614C1 |

| Компенсационный интегратор | 1978 |

|

SU798886A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Интегратор | 1978 |

|

SU744628A2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ СОВОКУПНОСТИ ВХОДНЫХ СИГНАЛОВ | 1994 |

|

RU2134929C1 |

%

Vi

1

.

t

XOffff.

dbfwd mpyfieflo

Авторы

Даты

1982-01-07—Публикация

1980-04-23—Подача