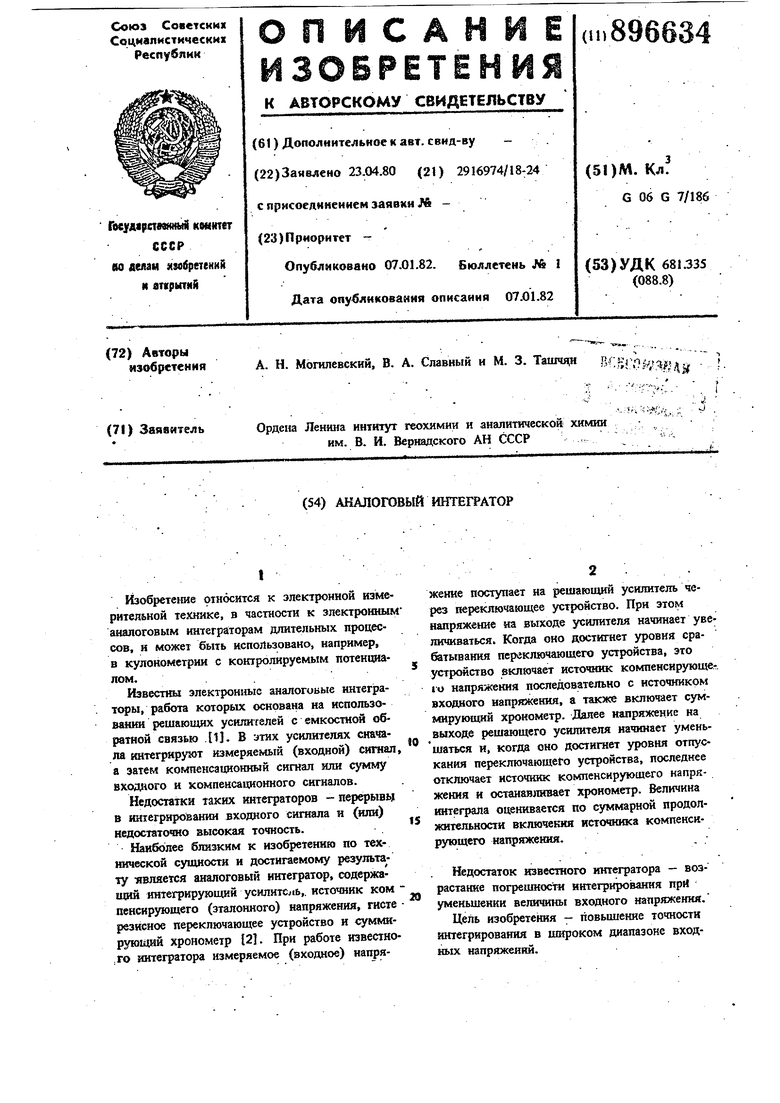

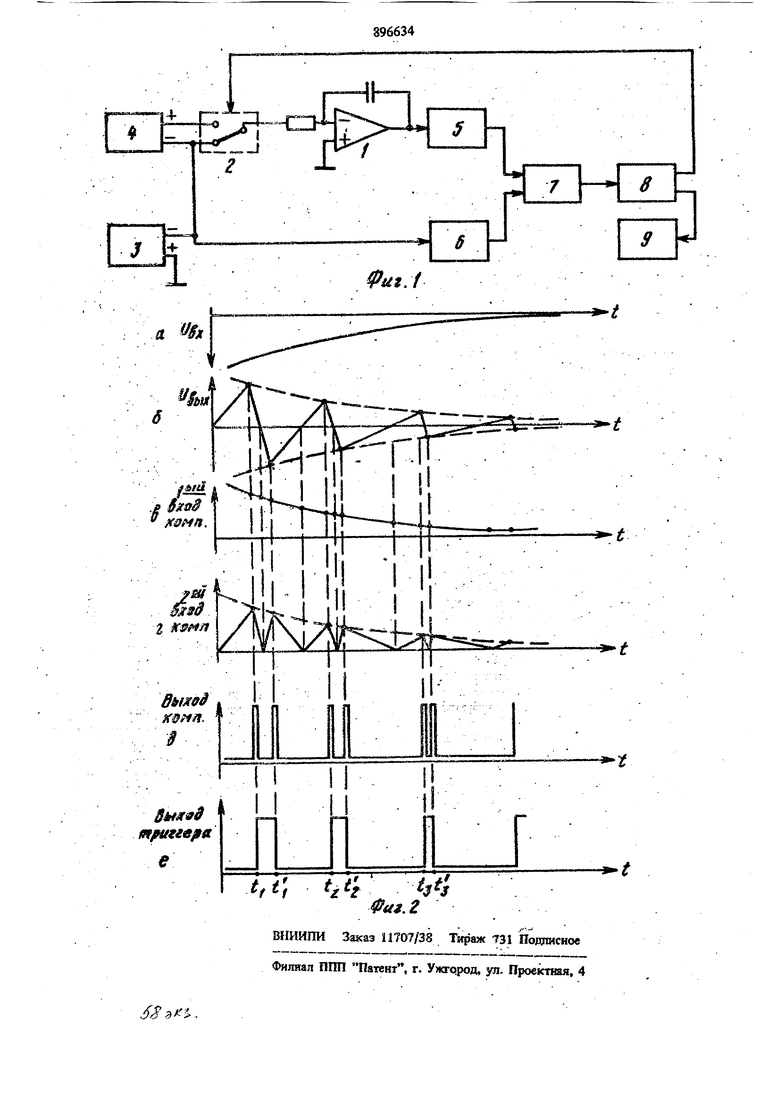

- - . Изобретение относится к электронной измерительной технике, в частности к электронным аналоговым интеграторам длительных процессов, и может быть использовано, например, в кулонометрии с контролируемым потенциалом. Известны электрош1ыс аналогивые интеграторы, работа которых основана на нспользовашш решающих усилителей с емкостной обратной связью .1. В этих усилителях сначала интегрируют измеряемый (входной) сигнал а затем компенсационный сигнал или сумму BKooiioro и компенсационного сигналов. Недостатки таких интеграторов - перерывад в интегрировании входного сигнала и (юга) недостаточно высокая точность. Наиболее близким к изобретению по технической сущиости и достигаемому результату -явп&епя аналоговый интегратор, содержащий интегрирующий усилитель,, источник ком пенсирующего (эталонного) напряжения, гнете резисное переключающее устройство и суммирующий хронометр 12. При работе известно .го интегратора измеряемое (входное) напряжение поступает на решающий усилитель через переключающее устройство. При зтом напряжение на выходе усилителя начзшает увеличиваться. Когда оно достигнет уровня срабатывания переключающего устройства, это устройство включает источник компенснрующе-. 10 напряжения последовательно с нсточником входного напряжения, а также включает суммирующий хронометр. Далее напряжение на выходе рещающего усилителя начинает уменьшаться и, когда оно достигнет уровня отпускания переключающего устройства, последнее отключает нсточкик компенсирующего напряжения и останавливает хронометр. Величина интеграла оценивается по суммарной продолжительности включения источника компенсирующего напряжения. Недостаток известного интегратора - возрастание погрешности интегрирования при умекьщенки величины входного напряжения. Цель изобретения - повьщ1ение точности интегрирования в ип роком диапазоне входных напряжений. 3 Поставленная цель достигается тем, что в известный аналоговый интегратор, содЬржаиИЙ интегрирующий усилитель, вход которого соединен с подвижным контактом переключателя непод&нжкые контакты которого подключены соответственно к одному выводу источника компенсирующего напряжения и общему выаоду источников, входного икомпенсирующег напряжений, друго вывод источника входного напряжения соединен с шиной нулевого потенциала, и суммирующий хронометр, введены два блока формирования модуля знакопеременного напряжения,, безгистерезисный компаратор .и-триггер, выход которого подклю.чен к. управляющим входам переключателя и суммирующего хронометра, входы блоков формирования модуля знакопеременного напряжения подключены соответственно к выходу иитегриругощего усилителя и общему выводу источников входного и компенсирующего напряжений, а выходы соединены со BXOflDi -oj безгистерезисиого KOMnapaTbpia, вы-. ход которого подключен ко входу триггера. На фиг. I приведена структурная электрическая схема аналогового шггегратора; на фиг. 2 - временные диаграмглы, иллюстрирующие работу интегратора. Аналоговый интегратор содержит интегрирующий усилитель 1, вход которого через переключатель 2 соед1Я1ен с нсточ1шком 3 входного и источником 4 компенсирующего напряжений. Источники 3 и 4 вктаочены встречно. С выходом усЕ-шителя -1 соединен вход блока 5 фop отpoвamш модуля зиакопереме шого напряжения. Вход второго блока б формирования модуля соединен с источником 3 входного С5«-нала. Выходы блоков 5 и 6 соединены соответственно с входами без гистерезискогр компаратора 7. Выход компаратора 7 через счетный триггер 8 соединен с управляющими входами переключателя и сум лиpyющero хронометра 9, На фиг. 2 изобра5кекы сле)аующив диаграм мы: а - входное (измеряемое) напряжение источника 3; б - выходное напряжение реша ющего усялзггеля 1 (проинтегрированный сигнал); в - модуль входного напряжения; г модуль выходного напряжения усилителя; д выходное напряжение компаратора 7; е - вы .ход триггера 8. Кроме того, обозначены моменты включения ti, tj, ts и тд., а также моменты вьпслючсния источника компенсирую щего напряжений ti, t, t| и т.д. При практическом осуществлении интегратора переключатель 2 может бьпь выполнен. например, в виде электромагнитного реле/об мотка включена на выход триггера 8. Блоки 5 и б формирования модуля знакопеременно го напряжения могут быть выполнены, напри ер, по схеме выпрямителей среднего значеия на основе операционных усилителей. В ачестве безгистерезисного компаратора 7 можо использовать любой дифференциальный силитель, например операционный усилитель. Устройство работает следующим образом. Входное напряжение (фиг. 2, а) от источника 3 поступает на вход интегрирующего . усилителя 1 через переключатель 2. Вследствне этого выходное напряжение (фиг. 2, б) усилителя 1 начинает увеличиваться. Это напряжение поступает на вход блока 5 формирования модуля знакопеременного сигнала, напряжение на выходе котсГрого (фиг. 2, г) по абсолютной величине равно напряжению на выходе усилителя 1, но всегда положительно. Напряжение источника 3 поступает также на вход блока 6, который работает аналогично блоку 5. Напряжение на выходе блока 6 (фиг. 2, в) по абсолютной величине равно напряжению источника 3 входного напряжения, но всегда положительно, напряжение с выходов блока 5 и 6 (фиг. 2, в и фиг. 2, г) сравнивается компаратором 7. В момент ti равенства указанных напряжений компаратор 7 вырабатывает импульс (фиг. 2, д), который поступает на счетный вход триггера 8, опрокидывая последний (фиг. .2, с).-Триггер 8, воздействуя на управляющий вход перекяадчателя 2, переводит его в верхнее положение. В этом случае источники 3 и 4 входного .и компенсирующего напряжений, включенные з тречно, подсоединяются ко входу кнтег5Н1рующего усилителя 1. Одновременно перепадом напряжения с выхода триггера 8 включается суммнр)пющий хронометр 9. Вследствие интегрирования суммы напряжений источников 3 и 4 выходное напряжение усилителя 1 начинает уменьщаться ,Сфиг- 2, б), а затем и меняет свою полярность. Б момент tij Соответствующий следующему после мо-менгы tj равенству модулей напряжения источника 3 входного сигнала и выходного напряжения усилителя 1, т.е.- равенству напряжений на выходах блоков 5 и 6 (фиг. 2, е), компаратор.7 вырабатывает импульс, который возвращает триггер 8 в исходное положение. Вследствие этого переключатель 2 отключает источник 4 компенсирующего напряжения и останавливает суммирующий хронометр 9. На вход интегрирующего. усилителя 1 поступает напряжение источника 3, выходное напряжение усилителя 1 начинает увеличиваться. Далее все процессы с циклическим включением (момипы t2,-t3 И Т Л.) И выключением (моменты ti, tsH т.д.) источника 4 компенсирующего напряжения и хронометра 9 в моменты равенства модулей напряжения источника 3 входного напряжения и напряжения на вьпсо5де усилителя 1 (проинтегрированный сигнал) повторяются в течение всего времени интегрирования. Величина интеграла оценивается по суммарной продолхсительности включения источника компенсирующего напряжения, измеряемой суммирующим хронометром. Преимуществом предлагаемого аналогового интегратора является существенно меньшая погрешность при интегрировании входных напряжений, изменяющихся в широком диапазоне величин. Это преимущество основано на том, что в отличие от известного интегритора, в котором уровни проинтегрированного сигнала, соответствующие моментам включения и выключения источника компенсирующего напряжения, постоя1щы и не зависят от величины входного напряжения. В предлагаемом интеграторе эти уровни равны (по абсолютной величине) входному напряжению. 1Вследствие зтого длителикость отдельного щисла интегрирования не увеличивается при уменьшении величины входного напряжения и поэтому погрешность интегрирования, определяемая конечной величиной экв«1валентной постоянной времени решающего усилителя, в частности утечкой в интегрийтощем конденсаторе, остается практически неизменной при уменьшении входного напряжения. Следует также отметить, что в предлагаемом интеграторе имеет место дополнительное снижение, погрешности интегрирования. Это обусловлено тем, что проинтегрированный сиг нал изменяется приблизительно симметрично относительно нулевого уровня. Поэтому среднее значение проинтегрированного сигнала (вь ходаого напряжения решающего усилителя), о которого наряду с утечкой в конденсаторе зависит погрешность интегрирования, мало, чт и ведет к дополнительному снижению погрешности. Формула изобретения .. . .. Аналоговый интегратор, содержащий ннтегрнруюиуй усилитель, вход которого соелишен с подвижным контактом переключателя , неподвижные контакты которого подключены соответствекно к одному выводу источника кЪмпенсирующего напряжения н общему выводу источников компенсирующего и входного напряжений, другой вывод источника входного напряжения соединен с шиной нулевого потенциала, н суммируюшкй хронометр, отличающийся тем, что, с целью кжышения точности интегрирования в широком диапазоне входных напряжений, в него введены два блока формирования модуля знакоперемеииого напряжения, безгистерсзискый компаратор н триггер, выход которого подключен к управлявшим входам переключателя и суммирующего хронометра, входы блока формирования модуля знакомеременного напряжения подключены соответственно к выходу интегрирующего усилителя и общему выводу источников входного и компенсирующего напряжений, а выходы соединены со входами безгистерезисного компаратора, выход которого подключен ко входу триггера. Источники информации, . принятые во внимание при экспертизе 1.Махнанов В. Д. н Мклохин М. Т. Устройство частотного и время-импульсного пре.образования. М., Энергия, 1970, с. , 115-119. 2.Авторское свидетельство СССР К 374618, кл. G 08 G 7/18, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый интегратор | 1980 |

|

SU896633A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2014 |

|

RU2571618C1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР НАПРЯЖЕНИЯ | 2014 |

|

RU2571614C1 |

| Компенсационный интегратор | 1978 |

|

SU798886A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ СОВОКУПНОСТИ ВХОДНЫХ СИГНАЛОВ | 1994 |

|

RU2134929C1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Интегрирующее устройство | 1980 |

|

SU924721A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-23—Подача