(54) УСТРОЙСТВО ОЦЕНКИ СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Устройство оценки сигнала | 1974 |

|

SU482903A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840115A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С УСТРОЙСТВОМ БЫСТРОГО ПОИСКА НАВИГАЦИОННЫХ СИГНАЛОВ В УСЛОВИЯХ ВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2006 |

|

RU2341898C2 |

| СПОСОБ ПРИЕМА МНОГОЛУЧЕВОГО СИГНАЛА, СПОСОБ ПОИСКА И СПОСОБ ФОРМИРОВАНИЯ МЯГКИХ РЕШЕНИЙ ПРИ ПРИЕМЕ МНОГОЛУЧЕВОГО СИГНАЛА И УСТРОЙСТВА, ИХ РЕАЛИЗУЮЩИЕ | 2003 |

|

RU2251802C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1980 |

|

SU1840563A1 |

| ИЗМЕРИТЕЛЬ ОТНОШЕНИЯ СИГНАЛ-ШУМ | 1992 |

|

RU2117954C1 |

I

Изобретение огнсжится к технике оси работки сигналов, может использоваться в сясгемая передачи информации, в раш онавигЕоцш, в рашолоквдии.

По основному авт. св. N 482903 известно устройство шенки. сигнала, состоящее из генератора опорных сигналов, решающего устройства, N корреляторов, кажоый из которых состоит из перемножакяцего устройства и интегратора и N пороговых устройств, дополнительно ввеценного переключающего блока, ооин вход которого пооключен к вькопу генератора счетной частоты, второй вход подключен к выходу генератора опорных сигналов, а выход - к входам интеграторов каждого коррелятора fl 1

Однако известное устройство не об/шцает достаточно высокой помехоустойчивостью.

Целью изобретения является повышение помехоустойчивости путем анализа верности оценки сигнала.

Для этого в известное устройство Оценки сигнала введены последовательно соединенные счетчик, вычитающий блок, первый пороговый блок, и элемент И и последовательно соединенные регистр памяти и втсрой пороговый бл(ж, выход которого подключен к другому входу элемента И, выход которого подключен к дополнительному входу решающего блока, дополнительный выход которого подклю10чен к управляющему входу регистра памяти, сигнальный вход которого соединен с выходом счетчика, вход которого соединен с выходом переключающего блока, причем выход регистра памяти подключен

IS к щэугому входу вычитающего блока.

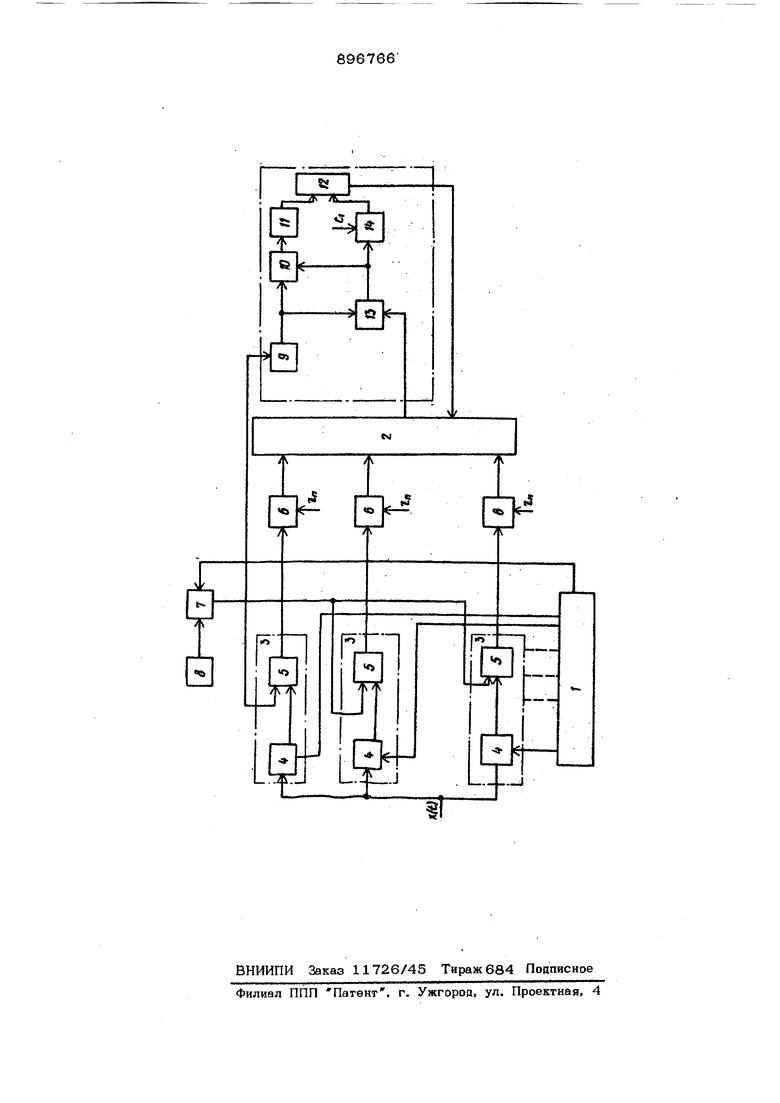

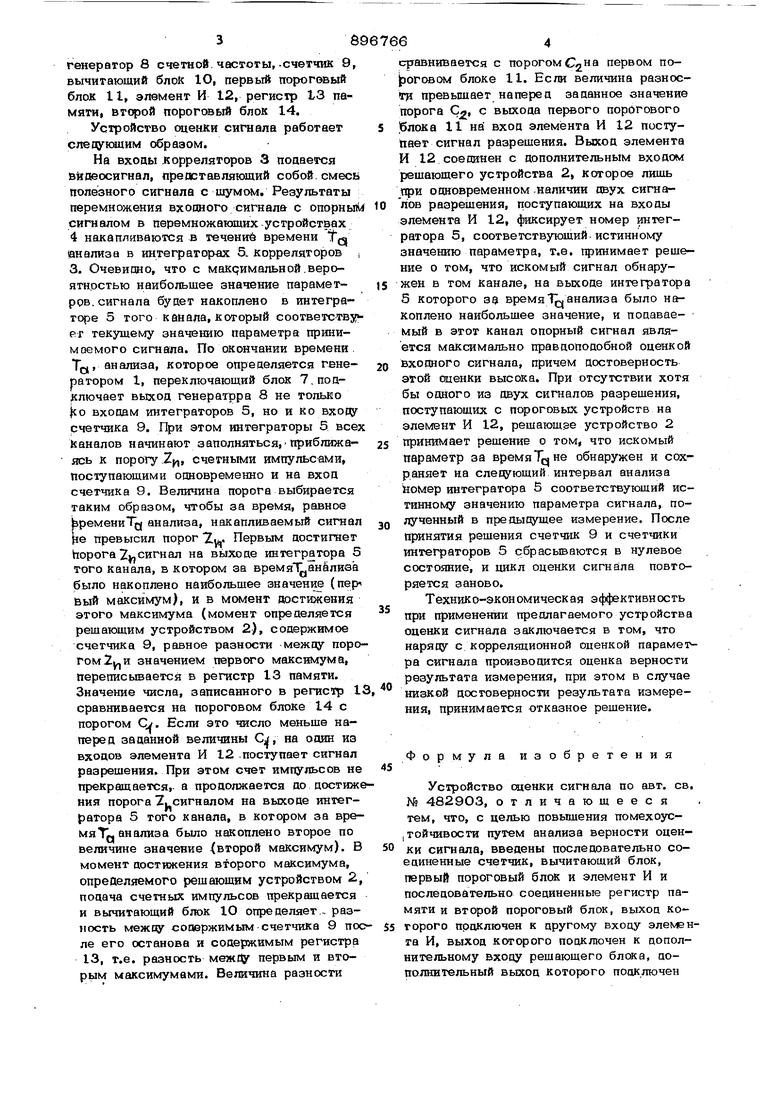

На чертеже изображена структурная электрическая схема предлагаемого-уст ройства.

Устройство оценки сигнала содержит

20 генератор 1 опорных сигналов,, решающее устройство 2, коррелятор 3, перемножающее устройство 4, интегратор 5, пороговые устройства 6, переключакмций блок 7, генератор 8 счетной, чозгогы,-счетчик 9, вычитающий блок 1О, первый пороговый блок 11, элемент И 12, регистр 13 памяти, второй пороговый блок 14. Устройство сщенки сигнала работает слец)гкяцим образом. На вхоцы 15орреляторов 3 подается Видеосигнал, представляющий собой, смесь полезного сигнала с шумом. Результаты перемножения входного сигнала с опорны)и сигналом в перемножающих устройствах 4 накапливаются в течение времени Г (анализа в интеграторах 5. корреляторов , 3. Очевидно, что с макс имальной.вероятностью наибольшее значение параметров, сигнала будет накоплено в интеграторе 5 того канала, который соответствую рг текущему значению параметра принимаемого сигнала. По окончании времени. TQ, анализа, которое определяется генератором I, переключающий блок 7, под,ключает выход генератрра 8 не только ito входам интеграторов 5, но и ко вхосу счетчика 9. При этом интеграторы 5 всех Каналов начинают заполняться, приближаясь к порогу 2y, счетными импульсами, Пос1упающими одновременно и на вход счетчика 9. Величина порога выбирается таким образом, чтобы за время, равное ЬремениТц анализа, накапливаемый сигнал ре превысил порог Zu. Первым достигнет hopora 2 сигнал на выходе интегратора 5 того канала, в котором за времяТ анйлиаа было накоплено наибольшее значение (пер Ьый максимум), и в момент достижения этого максимума (момент определяется решающим устройством 2), содержимое счетчика 9, равное разности между порогом 2 и значением первого максимума, переписывается в регистр 13 памяти. Значение числа, записанного в регистр 13 сравнивается на пороговом блоке 14 с порогом С. Если это число меньше наперед заданной величины С;, на один из входов элемента И 12 .поступает сигнал разрешения. При этом счет импульсов не прекращается, а продолжается до достиже ния порога X сигналом на выходе интегратора 5 того канала, в котором за время TQ анализа было накоплено второе по величине значение второй максимум). В момент достижения второго максимума, определяемого решающим устройством 2, подача счетных импульсов прекращается и вычитающий блок 10 определяет - разлость между содержимым счетчика 9 пос-ss ле его останова и содержимым регистра 13, т.е. разность первым и вторым максимумами. Величина разности сравнивается с порогомСоНа первом пооговом блоке 11. Если величина разности превышает наперед заданное значение порога Ccg, с выхода первого порогового блока 11 на вход элемента И 12 посчуйает сигнал разрешения. Выход элемента И 12 соединен с дополнительным входом решающего устройства 2, которое лишь при одновременном .наличии двух сигна ов разрешения, поступающих на входы элемента И 12, фиксирует номер интегратора 5, соответствующий истинному значению параметра, т.е. принимает решение о том, что искомый сигнал обнаружен в том канале, на выходе интегратора 5 которого 39 время Т анализ а было накоплено наибольшее значение, и подаваемый в этот канал опорный сигнал является максимально правдоподобной оценкой входного сигнала, причем достоверность этой оценки высока. При отсутствии хотя бы одного из двух сигналов разрешения, поступающих с пороговых устройств на элемент И 12, решающее устройство 2 принимает решение о том, что искомый параметр за время Tq не обнаружен и сохраняет на следующий интервал анализа йоМер интегратора 5 соответствующий истинному значению параметра сигнала, по ученный в предыдущее измерение. После принятия решения счетчик 9 и счетчики интеграторов 5 сбрасьгоаются в нулевое состояние, и цикл оценки сигнала повторяется заново. Технико-экономическая эффективность при применении предлагаемого устройства оценки сигнала заключается в том, что наряду с корреляционной оценкой параметра сигнала производится оценка верности результата измерения, при этом в случае низкой достоверности результата измерения, принимается отказное ращение. Формула изобретения Устройство оценки сигнала по авт. св. 482903, отличающееся тем, что, с целью повышения помехojrc|Тойчивости путем анализа верности оценки сигнала, введены последовательно соединенные счетчик, вычитающий блок, первый пороговый блок и элемент И и последовательно соадиненнью регистр памяти и второй пороговый блок, выход которого прдключен к другому входу элемента И, выход которого подключен к дополнительному входу решающего блсжа, дополнительный выход которого подключен

5 896766«

к управляющему вхоцу. регистр а памяти,HcroHHHkH ввформацин,

сигнальный вхоа которого соеаинен с выпринятые во вниманве при акспе|рг ходом счетчика, вход которого соеаинен

с выходом переключающего блсяса, причем1Г Авторское сввовтельство СССР

выход регистра памяти подключен к дру-Mi 4829ОЗ, кя, Н О4 В 1/10, .1974

гому входу вычитающего блока,(прототип).

а

Фп1

I LIFT Up-j

Р

I

Tt::

Щ

Авторы

Даты

1982-01-07—Публикация

1980-01-24—Подача