1

Изобретение относится к запоминающим устройствам и может быть использовано в ЦВМ для хранения информации, в частности в микропрограммных устройствах управления.

Известно запоминающее устройство, содержащее формирователь адреса, накопитель с зонами контроля и информационных сигналов, коммутаторы, включенные на выходе накопителя, дешифратор переключения коммутаторов, суммирующее устройство и блок сравнения 1.

Недостатком этого устройства является отсутствие в нем контроля работоспособности формирователя адреса и контроля работоспособности накопителя по отдельным словам, выбираемым из накопителя.

Наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее формирователь адреса, накопитель с зонами контроля и информационных сигналов, регистр числа, два блока контроля 2.

В этом устройстве не проверяется работа дещифра ора адреса, осуществляется недостаточная проверка работоспособности накопителя и используются сложные, многоступенчатые

свертки в блоках контроля, что снижает надежность запоминающего устройства. - Цель изобретения - повыщение надежности запоминающего устройства.

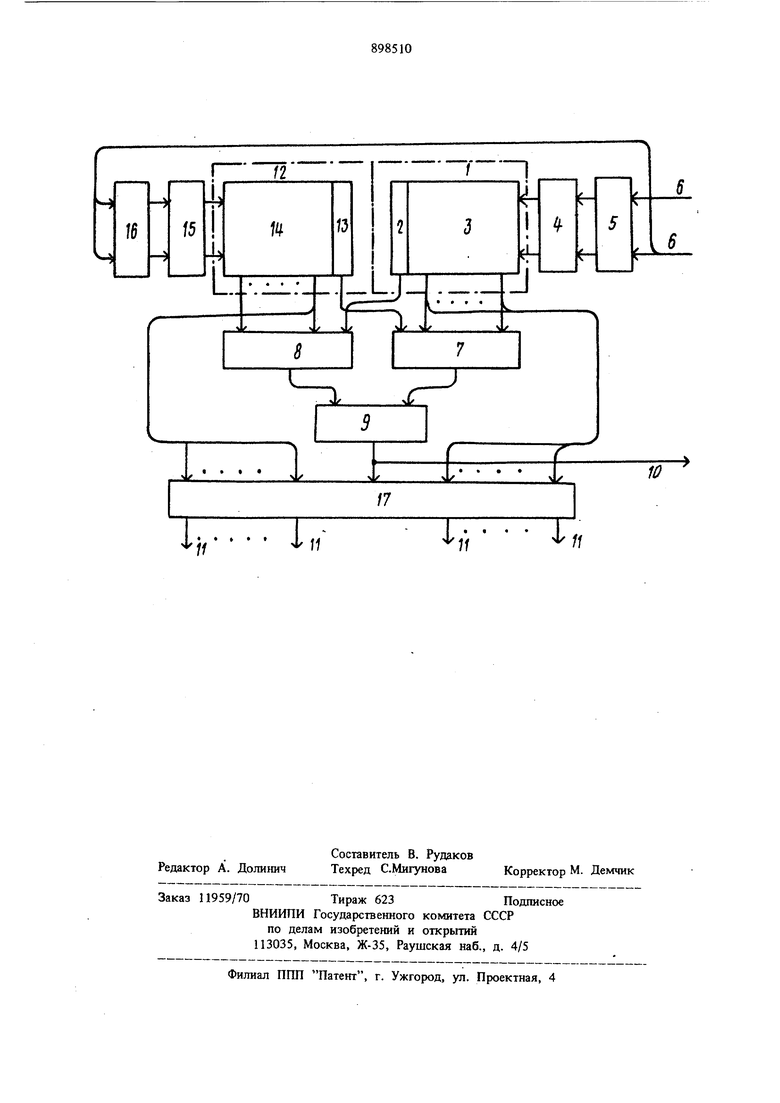

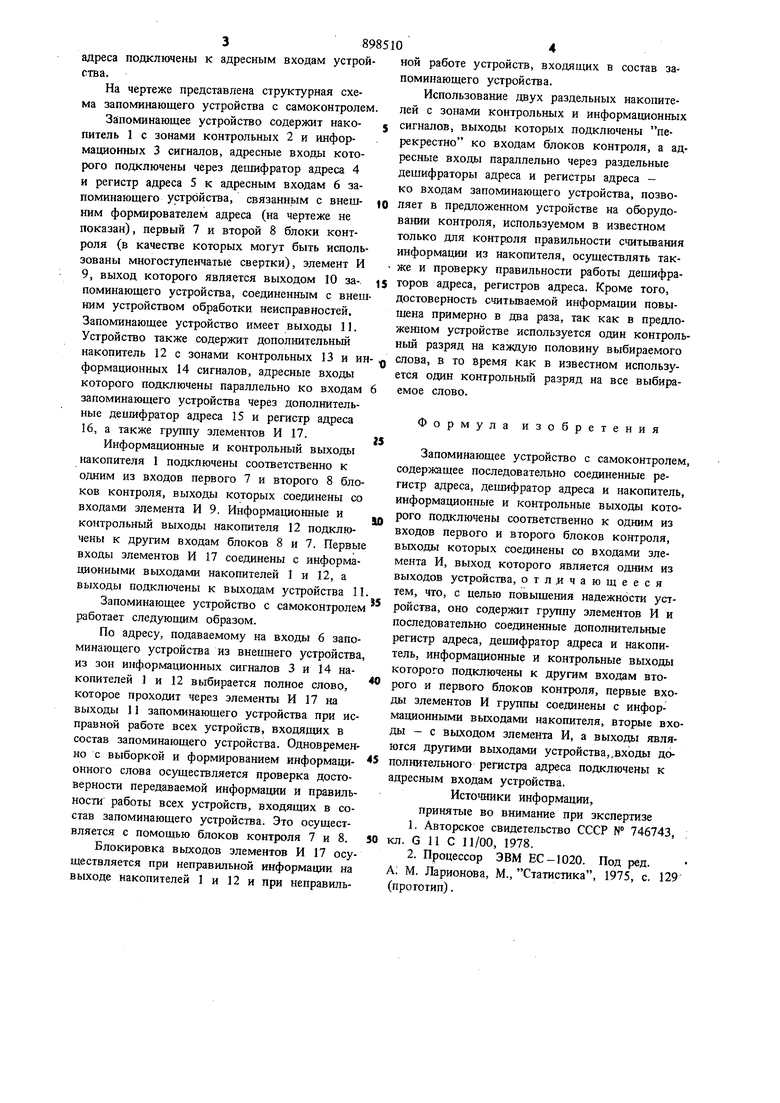

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее последовательно соединенные регистр адреса, дещифратор адреса и накопитель, информационные и контрольные выходы которого подключены соответственно к одним из входов первого и второго блоков контроля, выходы которых соединены со входами элемента И, выход которого является одним из выходов устройства, введена группа элементов И и последовательно соединенные дополнительные регистр адреса, дещифратор адреса и накопитель, информационные и контрольные выходы которого подключены к другим входам второго и первого блоков контроля, первые входы элементов И группы соединены с информационными выходами накопителя, вторые входы - с выходом элемента И, а выходы являются другими выходами устройства, входы дополнительного регистра адреса подключены к адресным входам устройства. На чертеже представлена структурная схема запоминающего устройства с самоконтролем Запоминающее устройство содержит накопитель 1 с зонами контрольных 2 и информационных 3 сигналов, адресные входы которого подключены через дешифратор адреса 4 и регистр адреса 5 к адресным входам 6 запоминающего устройства, связанным с внешним формирователем адреса (на чертеже не показан), первый 7 и второй 8 блоки контроля (в качестве которых могут быть использованы многоступенчатые свертки), элемент И 9, выход которого является выходом 10 за-. поминающего устройства, соединенным с внеш ним устройством обработки неисправностей. Запоминающее устройство имеет выходы 11. Устройство также содержит дополнительный накопитель 12 с зонами контрольных 13 и ин формационных 14 сигналов, адресные входы которого подключены параллельно ко входам запоминающего устройства через дополнительные деншфратор адреса 15 и регистр адреса 16, а также группу элементов И 17. Информационные и контрольный выходы накопителя 1 подключены соответственно к одним из входов первого 7 и второго 8 блоков контроля, выходы которых соединены со входами элемента И 9. Информаш1онные и контрольный выходы накопителя 12 подключены к другим входам блоков 8 и 7. Первые входы элементов И 17 соединены с информационными выходами накопителей 1 и 12, а выходы подключены к выходам устройства П Запоминающее устройство с самоконтролем работает следующим образом. По адресу, подаваемому на входы 6 запоминающего устройства из внешнего устройства из зон информационных сигналов 3 и 14 накопителей 1 и 12 выбирается полное слово, которое проходит через элементы И 17 на выходы 11 запоминающего устройства при исправной работе всех устройств, входящих в состав запоминающего устройства. Одновремен но с выборкой и формированием информационного слова осуществляется проверка достоверности передаваемой информации и правильности работы всех устройств, входящих в состав запоминающего устройства. Это осуществляется с помощью блоков контроля 7 и 8. Блокировка выходов элементов И 17 осу ществляется при неправильной информации на выходе накопителей 1 и 12 и при неправильОЙ работе устройств, входящих в состав заоминающего устройства. Использование двух раздельных накопитеей с зонами контрольных и информационных игналов, выходы которых подключены пеекрестно ко входам блоков контроля, а адесные входы параллельно через раздельные ешифраторы адреса и регистры адреса - о входам запоминающего устройства, позвояет в предложенном устройстве на оборудоании контроля, используемом в известном только для контроля правильности считьшания нформации из накопителя, осуществлять также и проверку правильности работы дешифраторов адреса, регистров адреса. Кроме того, достоверность считьтаемой информации повышена примерно в два раза, так как в предложенном устройстве используется один контрольный разряд на каждую половину выбираемого слова, в то время как в известном используется один контрольный разряд на все выбираемое слово. Формула изобретения Запоминающее устройство с самоконтролем, содержащее последовательно соединенные регистр адреса, дешифратор адреса и накопитель, информационные и контрольные выходы которого подключены соответственно к одним из входов первого и второго блоков контроля, выходы которых соединены со входами элемента И, выход которого является одним из выходов устройства, отлячающееся тем, что, с целью повыщения надежности устройства, оно содержит группу элементов И и последовательно соединенные дополнительные регистр адреса, дешифратор адреса и накопитель, информационные и контрольные выходы которого подключены к другим входам второго и первого блоков контроля, первые входы элементов И группы соединены с информационными выходами накопителя, вторые входы - с выходом элемента И, а выходы являются другими выходами устройства,,входы дополнительного регистра адреса подключены к адресным входам устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 746743, кл. G И С 11/00, 1978. 2.Процессор ЭВМ ЕС-1020. Под ред. А; М. Ларионова, М., Статистика, 1975, с. 129 (прототип).

-LX;

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU957277A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1056274A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с самоконтро-лЕМ | 1979 |

|

SU842980A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1156145A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU928423A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1264243A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

X

I I «4

4j/ 17

I

w

e.AL,

i

11

Авторы

Даты

1982-01-15—Публикация

1980-05-27—Подача