Изобретение относится к цифровой вычислительной технике и предназначено для использования в устройстве повышенной надежности, в частности в специализированных вычислительных машинах.

Известно запоминающее устройство с коррекцией ошибок методом избыточного кодирования, содержащее основной и дополнительный накопители, предназначенные для хранения информационных и контрольных разрядов соответственно. Входы и выходы основного накопителя соединены с выходами входного и выходного регистров числа и с входами первого и второго шифраторов соответственно, которые предназначены для выработки контрольных разрядов по определенному алгоритму (например, по коду Хэмминга). Выходы второго шифратора соединены с входами дополнительного накопителя, выходы которого совместно с выходами первого шифратора соединены с соответствующими входами блока сравнения, который предназначен для выработки синдрома ошибки. Выходы блока сравнения через дешифратор соединены с вторыми входами выходного регистра. Это устройство позволяет исправлять ошибки, возникающие в накопителе, и обладает повышенной надежностью в сравнении с ЗУ, в котором не используются корректирующие коды 1.

Недостаток устройства заключается в том, что кратность исправляемой ошибки низка и определяется корректирующей способностью применяемого кода.

Наиболее близким к изобретению по технической сущности и достигаемому результату является запоминающее устройство с самоконтролем, содержащее регистр адреса, вход которого является адресным входом устройства, а выход соединен с входами первого и второго накопителей. Выход первого накопителя, который наряду с информационными разрядами хранит и контрольные, через регистр данных соединен с информационным выходом устройства и входом блока декодирования, который предназначен для выработки сигнала ошибки и корректирующих разрядов. Первый выход блока коррекции соединен с вторыми входами второго накопителя и блока управления, первый вход которого соединен с выходом второго накопителя, предназначенного для хранения факта ошибки по определенному адресу. Выходы блока управления соединены с соответствующими входами второго и третьего накопителей и первым входом счетчика, второй вход которого соединен с выходом третьего накопителя, а выход - с третьим входом третьего накопителя и первыми входами дополнительного регистра и блока сравнения, выход которого соединен с вторым входом дополнительного регистра, первый вход которого соединен с вторым входом блока сравнения и является выходом, информирующим о числе отказов в блоке памяти, а на втором выходе дополнительного регистра формируется адрес этого блока. Третий вход дополнительного регистра соединен с третьим входом третьего накопителя и вторым входом блока декодирования 2. Недостатком известного устройства является невысокая надежность ЗУ при работе в составе автономных ЦВМ, в которых невозможно произвести профилактическую замену наиболее ненадежного блока в процессе эксплуатации. Число исправляемых ощибок невелико и также при этом определено корректирующей способностью кода. Ошибки большей кратности не исправляются.

i

Цель изобретения - повышение надежности устройства путем исправления ошибок, число которых превышает корректирующие способности применяемого кода.

Указанная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее регистр адреса, накопитель, счетчик, блок декодирования, причем вход регистра адреса является адресным входом устройства, выход регистра адреса соединен с одним входом накопителя, введены сумматор по модулю два, дещифратор, генератор импульсов, элемент И, один вход которого соединен с выходом генератора импульсов, а другой вход подключен к выходу блока декодирования и является одним выходом устройства, вход блока декодирования соединен с выходом сумматора по модулю два и является другим выходом устройства, выход накопителя подключен к одному входу сумматора по модулю два, другой вход которого соединен с выходом элемента И и одним входом счетчика, другой вход которого подключен к адресному входу устройства, выход счетчика подключен к входу дешифратора, выходы которого подключены к другим входам накопителя.

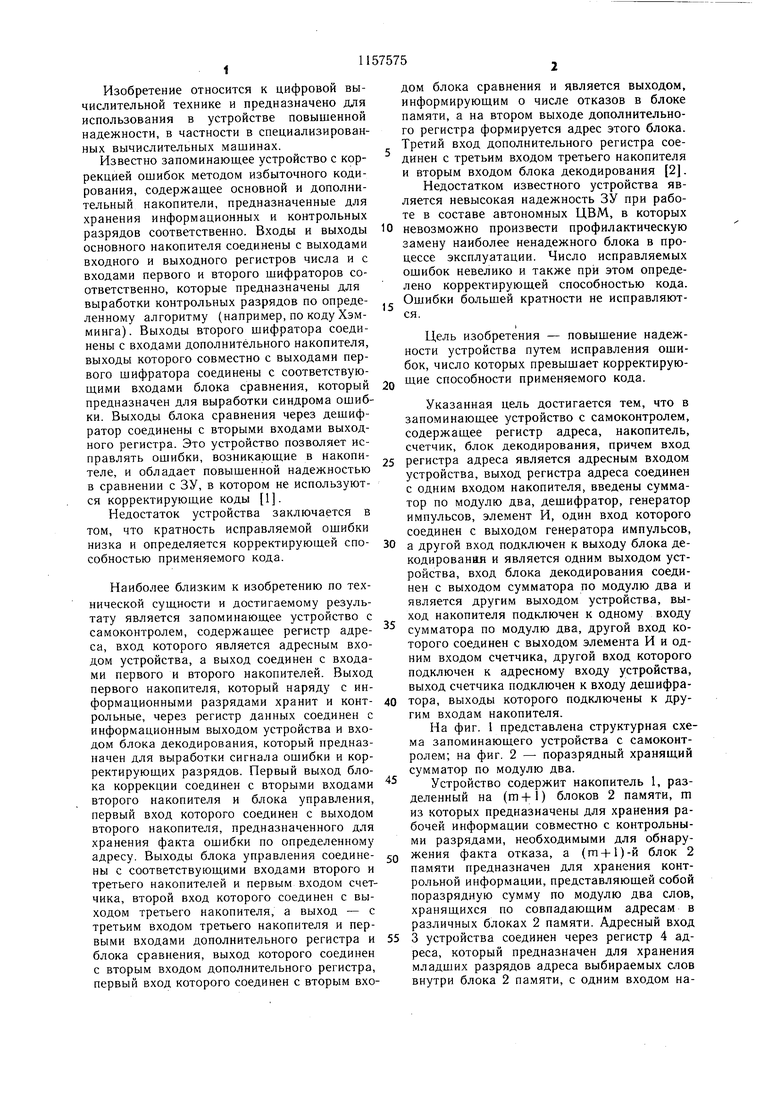

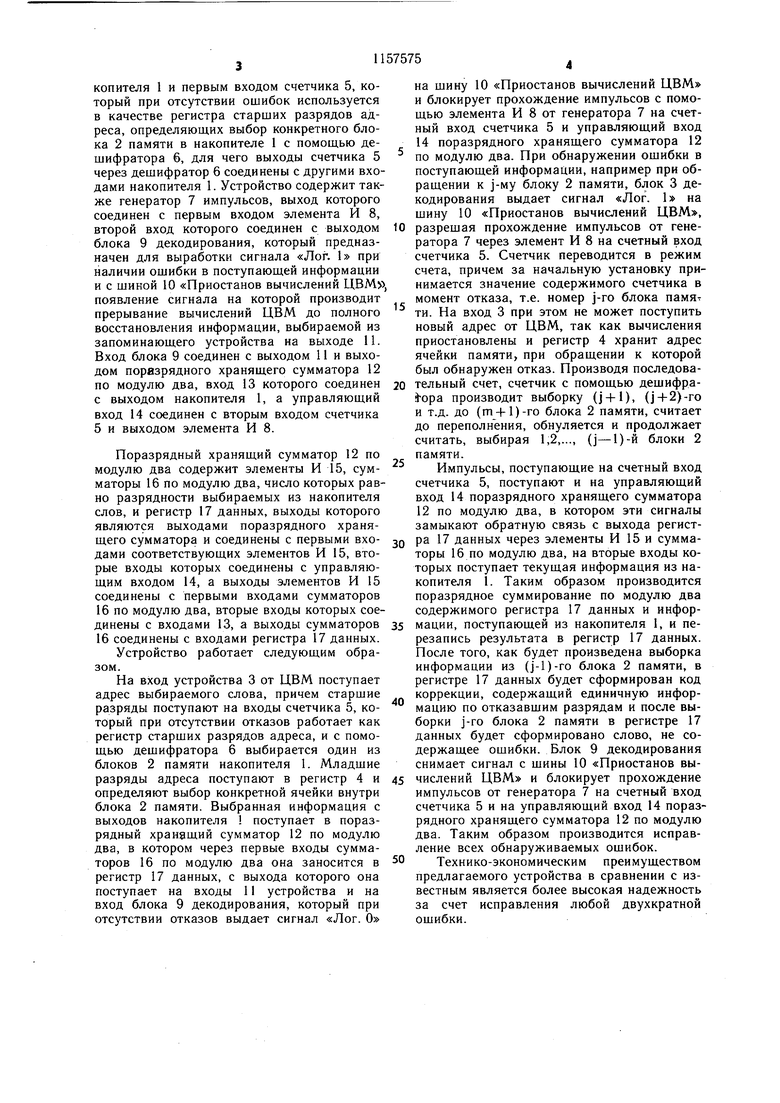

На фиг. 1 представлена структурная схема запоминающего устройства с самоконтролем; на фиг. 2 - поразрядный хранящий сумматор по модулю два.

Устройство содержит накопитель 1, разделенный на (гп -Ь1) блоков 2 памяти, m из которых предназначены для хранения рабочей информации совместно с контрольными разрядами, необходимыми для обнаружения факта отказа, а (т + 1)-й блок 2 памяти предназначен для хранения контрольной информации, представляющей собой поразрядную сумму по модулю два слов, хранящихся по совпадающим адресам в различных блоках 2 памяти. Адресный вход 3 устройства соединен через регистр 4 адреса, который предназначен для хранения младших разрядов адреса выбираемых слов внутри блока 2 памяти, с одним входом накопителя 1 и первым входом счетчика 5, который при отсутствии ошибок используется в качестве регистра старших разрядов адреса, определяющих выбор конкретного блока 2 памяти в накопителе 1 с помощью дешифратора 6, для чего выходы счетчика 5 через дещифратор 6 соединены с другими входами накопителя 1. Устройство содержит также генератор 7 импульсов, выход которого соединен с первым входом элемента И 8, второй вход которого соединен с выходом блока 9 декодирования, который предназначен для выработки сигнала «Лог. 1 при наличии ошибки в поступающей информации и с шиной 10 «Приостанов вычислений ЦВМ появление сигнала на которой производит прерывание вычислений ЦВМ до полного восстановления информации, выбираемой из запоминающего устройства на выходе 11. Вход блока 9 соединен с выходом 11 и выходом поразрядного хранящего сумматора 12 по модулю два, вход 13 которого соединен с выходом накопителя 1, а управляющий вход 14 соединен с вторым входом счетчика 5 и выходом элемента И 8.

Поразрядный хранящий сумматор 12 по модулю два содержит элементы И 15, сумматоры 16 по модулю два, число которых равно разрядности выбираемых из накопителя слов, и регистр 17 данных, выходы которого являются выходами поразрядного хранящего сумматора и соединены с первыми входами соответствующих элементов И 15, вторые входы которых соединены с управляющим входом 14, а выходы элементов И 15 соединены с первыми входами сумматоров 16 по модулю два, вторые входы которых соединены с входами 13, а выходы сумматоров 16 соединены с входами регистра 17 данных.

Устройство работает следующим образом.

На вход устройства 3 от ЦВМ поступает адрес выбираемого слова, причем старшие разряды поступают на входы счетчика 5, который при отсутствии отказов работает как регистр старщих разрядов адреса, и с помощью дещифратора б выбирается один из блоков 2 памяти накопителя 1. Младшие разряды адреса поступают в регистр 4 и определяют выбор конкретной ячейки внутри блока 2 памяти. Выбранная информация с выходов накопителя 1 поступает в поразрядный храндщий сумматор 12 по модулю два, в котором через первые входы сумматоров 16 по модулю два она заносится в регистр 17 данных, с выхода которого она поступает на входы 11 устройства и на вход блока 9 декодирования, который при отсутствии отказов выдает сигнал «Лог. О

на шину 10 «Приостанов вычислений ЦВМ и блокирует прохождение импульсов с помощью элемента И 8 от генератора 7 на счетный вход счетчика 5 и управляющий вход 14 поразрядного хранящего сумматора 12 по модулю два. При обнаружении ощибки в поступающей информации, например при обращении к j-му блоку 2 памяти, блок 3 декодирования выдает сигнал «Лог. 1 на шину 10 «Приостанов вычислений ЦВМ,

0 разрешая прохождение импульсов от генератора 7 через элемент И 8 на счетный вход счетчика 5. Счетчик переводится в режим счета, причем за начальную установку принимается значение содержимого счетчика в момент отказа, т.е. номер j-ro блока памят ти. На вход 3 при этом не может поступить новый адрес от ЦВМ, так как вычисления приостановлены и регистр 4 хранит адрес ячейки памяти, при обращении к которой был обнаружен отказ. Производя последовательный счет, счетчик с помощью дешифраJ-opa производит выборку (j-bl), (j+2)-ro и т.д. до (m-f 1)-го блока 2 памяти, считает до переполнения, обнуляется и продолжает считать, выбирая 1,2,..., (j-1)-й блоки 2 памяти.

Импульсы, поступающие на счетный вход счетчика 5, поступают и на управляющий вход 14 поразрядного хранящего сумматора 12 по модулю два, в котором эти сигналы замыкают обратную связь с выхода регистра 17 данных через элементы И 15 и сумматоры 16 по модулю два, на вторые входы которых поступает текущая информация из накопителя 1. Таким образом производится поразрядное суммирование по модулю два содержимого регистра 17 данных и информации, поступающей из накопителя 1, и перезапись результата в регистр 17 данных. После того, как будет произведена выборка информации из (j-l)-ro блока 2 памяти, в регистре 17 данных будет сформирован код коррекции, содержащий единичную информацию по отказавщим разрядам и после выборки j-ro блока 2 памяти в регистре 17 данных будет сформировано слово, не содержащее ошибки. Блок 9 декодирования снимает сигнал с шины 10 «Приостанов вычислений ЦВМ и блокирует прохождение импульсов от генератора 7 на счетный вход счетчика 5 и на управляющий вход 14 поразрядного хранящего сумматора 12 по модулю два. Таким образом производится исправление всех обнаруживаемых ощибок.

0 Технико-экономическим преимуществом предлагаемого устройства в сравнении с известным является более высокая надежность за счет исправления любой двухкратной ошибки.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1095240A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1089627A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1264243A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1105944A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее регистр адреса, накопитель, счетчик, блок декодирования, причем вход регистра адреса является адресным входом устройства, выход регистра адреса соединен с одним входом накопителя, отличающееся тем, что, с целью повышения надежности устройства, в него введены сумматор по модулю два, дешифратор, генератор импульсов, элемент И, один вход которого соединен с выходом генератора импульсов, а другой вход подключен к выходу блока декодирования .и является одним выходом устройства, вход блока декодирования соединен с выходом сумматора по модулю два и является другим выходом устройства, выход накопителя подключен к одному входу сумматора по модулю два, другой вход которого соединен с выходом элемента И и одним входом счетчика, другой вход которого подключен к адресному входу устройства, выход счетчика подключен к входу дешифратора, выходы которого подключены к другим входам накопителя. flpuocmijna 4/vuC(«UU i/d/V

| I | |||

| Самофалов К | |||

| Г., Корнейчук В | |||

| И., Городний А | |||

| В | |||

| Структурно-логические методы повышения надежности запоминающих устройств | |||

| М., «Машиностроение, 1976, с | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU746744A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-05-23—Публикация

1984-01-04—Подача