(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТГОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1264243A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU898511A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU898510A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU957277A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1056274A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

1

Изобретение относится к запоминающим устройствам и предназначено для использования в устройствах для обработки информации.

Известно запоминающее устройство с самоконтролем, содержащее накопитель с контрольными полями, входной и выходной регистры, схемы выявления неисправностей 1.

Однако это устройство имеет низкую до- . стоверность передаваемой информащ1и из-за отсутствия возможности контроля по всем единицам каждого слова, выбираемого из накопителя.

.

Наиболее близким техническим рещением к данному изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, формирователь адреса, депшфратор коммутации, коммутаторы, счетчик и блок сравнения 2.

Однако это устройство имеет невысокую надежность из-за отсутсвия контроля работоспособности формирователя адреса и из-за отс5тствия возможности контроля по всем

единицам каждого слова, выбираемого из накопителя.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, .что в запоминающее устройство с самоконтролем, содержащее накопитель, один из адресных входов которого подключен к выходам формирователя адресных сигналов, а информационные выходы - к одним из входов эле10ментов И, счетчик, выходы которого соединены с одними из входов схемы сравнения, введены блок поразрядного опроса и дополнительный формирователь адресных сигналов, входы которого являются адресными входа15ми устройства, а выходы подключены к другим адресным входам накопителя, другие входы схемы сравнения соединены соответственно с контрольными выходами накопителя и первым выходом блока поразрядного

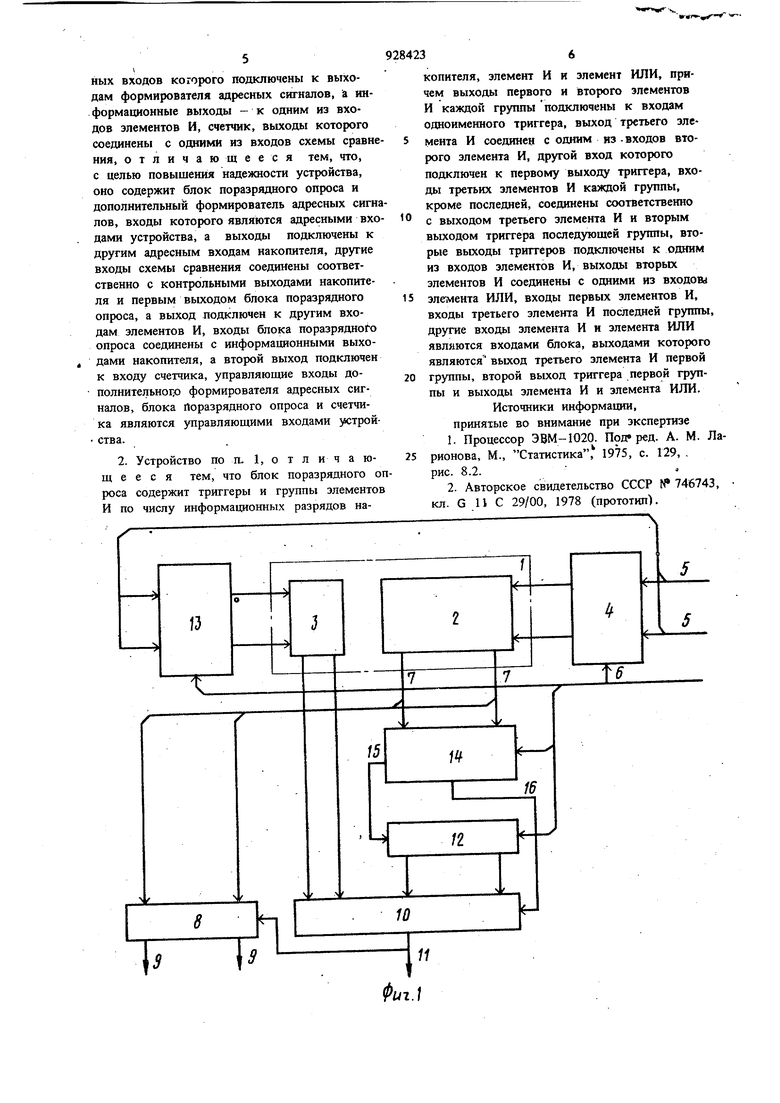

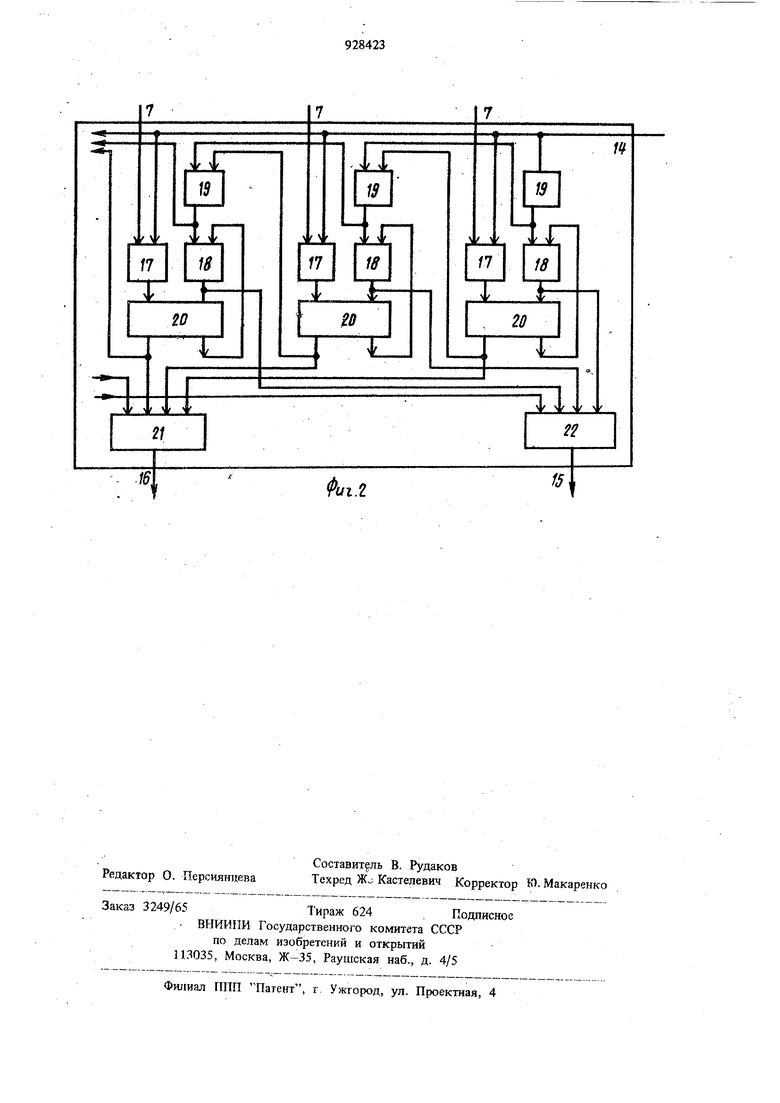

20 опроса, а выход подключен к другим входам элементов И, входы блока поразрядного опроса соединены с информационными выходами накопителя, а второй выход подключен к входу счетчика, упраляющие входы дополнительного формирователя адресных сигналов, блока поразрядного опроса и счетчика являются управляющими входами устройства. При этом целесообразно блок поразрядно , го опроса выполнить в виде блока, содержаj щего триггеры и группы элементов И по чи лу информационных разрядов накопителя, элемент И и элемент ИЛИ, причем выходы первого и второго элементов И каждой грзш пы подключены к входам одноименного три гера, выход третьего элемента И соедииен с одним из входов второго элемента И, друго вход которого подключен к первому выходу триггера, входы третьих элементов И каждои группы, кроме последней, соединены соответственно с выходом третьего элймеита И и вторым выходом триггера последующей группы, вторые выходы триггеров подключены к одним из входов элементов И, выходы вторых элементов И соединены с одними из входов .элемента ИЛИ, входы первых элементов И, входы третьего элемента И последней группы, другие входы лемента И и элемента ИЛИ являются входами блока, выходами которого являются выход третьего элемента И первой группы, второй выход триггера первой группы и вы ходы элемента И и элемента ИЛИНа фиг. 1 представлена структурная схема предложенного запоминающего устройства с самоконтролем; на фиг. 2 - принципиаль- ная схема блока поразрядного опроса (для трех разрядов). Запоминающее устройство с самоконтролем (см. фиг. 1) .содержит накопитель 1 с зонами информащш 2 и контроля 3, формирователь 4 адресных сигналов, имеющий вхо ды 5 и 6. Накопитель 1 имеет информационные выходы 7. Устройство также содержит элементы И 8, имеющие выходы 9, схему 10 сравнения с выходами И, счетчика 12, дополнительный формирователь 13 адресных сигналов и блок 14 поразрядного опроса с выходом 15 и выходом 16. Блок 14 (см. фиг. 2) содержит группы элементов И 1719, триггеры 20, элемент И 21 и элемент ИЛИ 22. Запоминающее устройство с самоконтролем работает следующим образом. По адресу и управляющим сигналам, пода ваемым соответственно на входы устройства из внешней ЦВМ, формирователь 4 осуществляет выборку соответствующего информационного слова из зоны информации 2 накопителя 1, а дополнительный формирователь 33 осуществляет выборку кода числа единиц (содержащихся в выбираемом слоiBC из зоны информадаи 2) из зоны контроЛЯ 3 накопителя 1, который подается на первые входы схемы сравнения 10. При этом информационное слово с выходов 7 зоны информации 2 подается на входы элементов И 8 и переписывается через элементы И 17 в триггеры 20 блока поразрядного опроса 14, и одновременно осуществляется установка счетчика 12 в исходное - нулевое состояние. Затем в блоке 14 осуществляется поочередное гащение единиц, записанных в триггеры 20, начиная с младщего разряда. При каждом гашении единицы на выходе 15 элемента ИЛИ 22 формируется импульс, который запоминается в счетчике 12, т.е. счетчик 12 подсчитывает количество единиц, Содержащихся в выбираемом слове, из зоны информации 2. После установки всех нулей в триггерах 20 блока 14 на выходе 16 элемента И 21 формируется импульс, обеспечивающий под слючение выходов 11 схемы 10 сравнения. При равенстве кодов на входах схемы 10 сравнения на ее выходе 11 формируется сигнал Ошибки нет, который разрешает передачу информации через элементь И. 8 на выходы 9 и разрешает формирование следующего адреса в формирователях 4 и 13, после чего цикл работы повторяется. При каждом неравенстве кодов на входах схемы 10 сравнения на ее выходе 11 вырабатывается сигнал ошибки, который запрещает выдачу информации на выходе 9 и запрещает формирование следующего адреса в формирователях 4 и 13. Технико-экономическое преимущество предложенного устройства в сравнении с известным заключается в повышенной надежности за счет обеспечения возможности контроля каждого слова (а не группы слов, как в известном устройстве), выбираемого из накопителя, не по четности (как в известном устройстве), а по сумме единиц, записанных в каждое из выбираемых слов, что практически исключает возможность передачи неверной информации на выход запоминающего устройства; а также обеспечения возможности контроля правильности работы формирователей адресного сигнала, так как управление выборкой слов из зон контроля и информации осуществляется через раздельные формирователи, в то время как в известном устройстве выборка слов из обеих зон накопителя осуществляется от общего (одного) формирователя. Формула изобретения 1. Запоминающее устройство с самоконтролем, содержащее накопитель, .один из адресных входов которого подключены к выходам формирователя адресных сигналов, а информационные выходы - к одним из входов элементов И, счетчик, выходы которого соединены с одними из входов схемы сравн ния, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок поразрядного опроса и дополнительный формирователь адресных сигн лов, входы которого являются адресными вхо дами устройства, а выходы подключены к другим адресным входам накопителя, другие входы схемы сравнения соединены соответственно с контрольными выходами накопителя и первым выходом блока поразрядного опроса, а выход подключен к другим входам элементов И, входы блока поразрядного опроса соединены с информационными выходами накопителя, а второй выход подключен к входу счетчика, управляющие входы дополнительно1;О формирователя адресных сигналов, блока Поразрядного опроса и счетчика являются управляющими входами устройства. 2. Устройство по п. 1, о т л и ч а ющ е е с я тем, что блок поразрядного оп роса содержит триггеры и группы элементов И по числу информационных разрядов на R

36 копнтеля, элемент И и элемент ИЛИ, причем выходы первого и второго элементов И каждой группы подключены к входам одноименного триггера, выход третьего элемента И соединен с одним из . входов второго элемента И, другой вход которого подключен к первому выходу триггера, входы третьих элементов И каждой группы, кроме последней, соединены соответственно с выходом третьего элемента И и вторым выходом триггера последующей группы, вторые выходы триггеров подключены к одним из входов элементов И, выходы вторых элементов И соединены с одними из входов 1 элемента ИЛИ, входы первых элементов И, входы третьего элемента И последней группы, другие входы элемента И и элемента ИЛИ являются входами блока, выходами которого являются выход третьего элемента И первой группы, второй выход триггера первой группы и выходы элемента И и элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Процессор ЭВМ-1020. Под ред. А. М. Ларионова, М., Статистика 1975, с. 129, . рис. 8.2. 2.Авторское свидетельство СССР 1 746743, кл. СП С 29/00, 1978 (прототип).

Авторы

Даты

1982-05-15—Публикация

1980-06-10—Подача