(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФЛУКТУА11ИОННЫХ ХАРАКТЕРИСТИК УЗКОПОПОСНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2001 |

|

RU2206901C1 |

| ИЗМЕРИТЕЛЬ ДЕВИАЦИИ ЧАСТОТЫ СИГНАЛОВ С ГАРМОНИЧЕСКОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2054680C1 |

| ПРОТИВОУГОННОЕ УСТРОЙСТВО ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1992 |

|

RU2033353C1 |

| Формирователь однополосного сигнала | 1985 |

|

SU1356183A1 |

| Устройство для измерения флуктуационных характеристик частоты радиосигналов | 1980 |

|

SU920558A1 |

| Устройство для приема фазоманипулированных сигналов | 1988 |

|

SU1598202A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2541147C1 |

| ФАЗОВЫЙ СПОСОБ ПЕЛЕНГАЦИИ И ФАЗОВЫЙ ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2426143C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАССТОЯНИЯ МЕЖДУ ВОЗДУШНЫМИ СУДАМИ | 2009 |

|

RU2411532C1 |

1

Изобретение относится к радиоизмерениям.

Известнй устройство для измерения флуктуационных характеристик сигналов, содержащее смеситель, на один вход которого подан сигнал непосредственно, а на второй вход через перестраиваемую линию задержки, и амплитудный детектору вход которого соединен с выходом смесителя СП .

Недостатками данного устройства яв- пиеяся малое быстродействие и необходимость в дополнительных вычислительных операциях.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство, содержашее первый перемножителъ, на входы которого поступает исследуемый сигнал и опорный сигнал, второй и .третий перемножители, первые входы которых подключены к выходу первого перемножител выходы которых через фильтры соединены с входами блоков вычисления производных, выходы и входы которых соединены с входами блока вычисления частоты, выход которого подключен к инпикаторуС2/.

Однако устройство не обеспечивает ilocTaточной точности.

Цель изобретения - повышение точности.

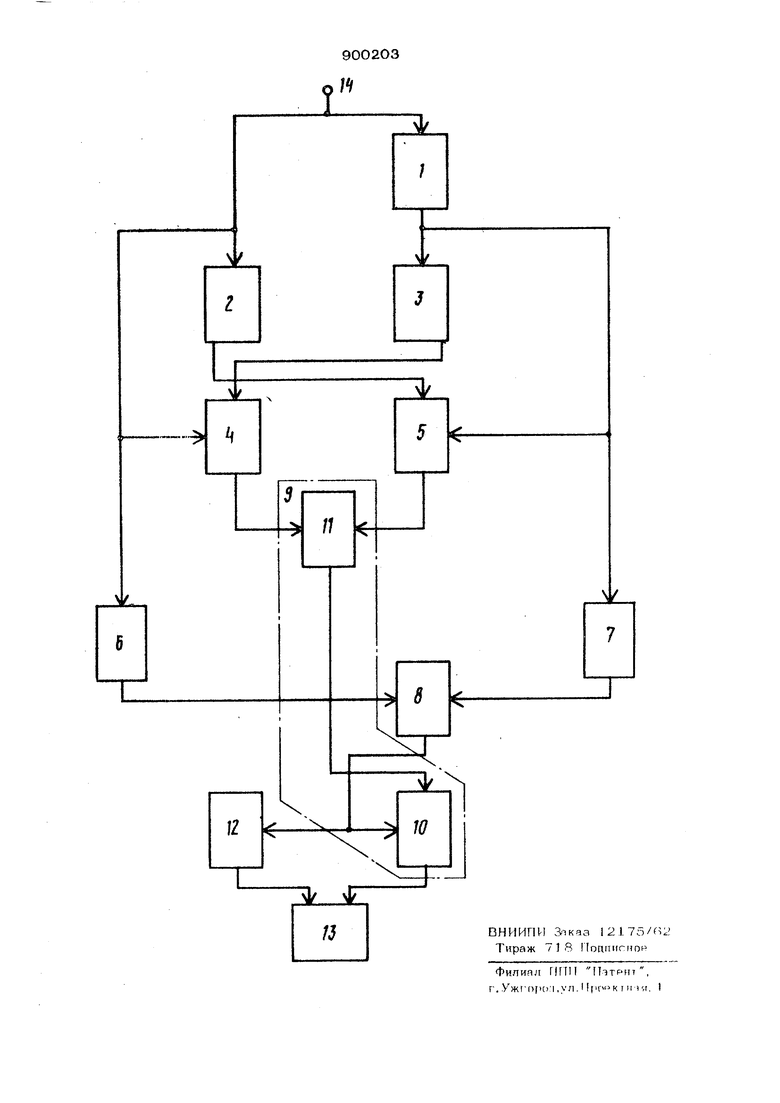

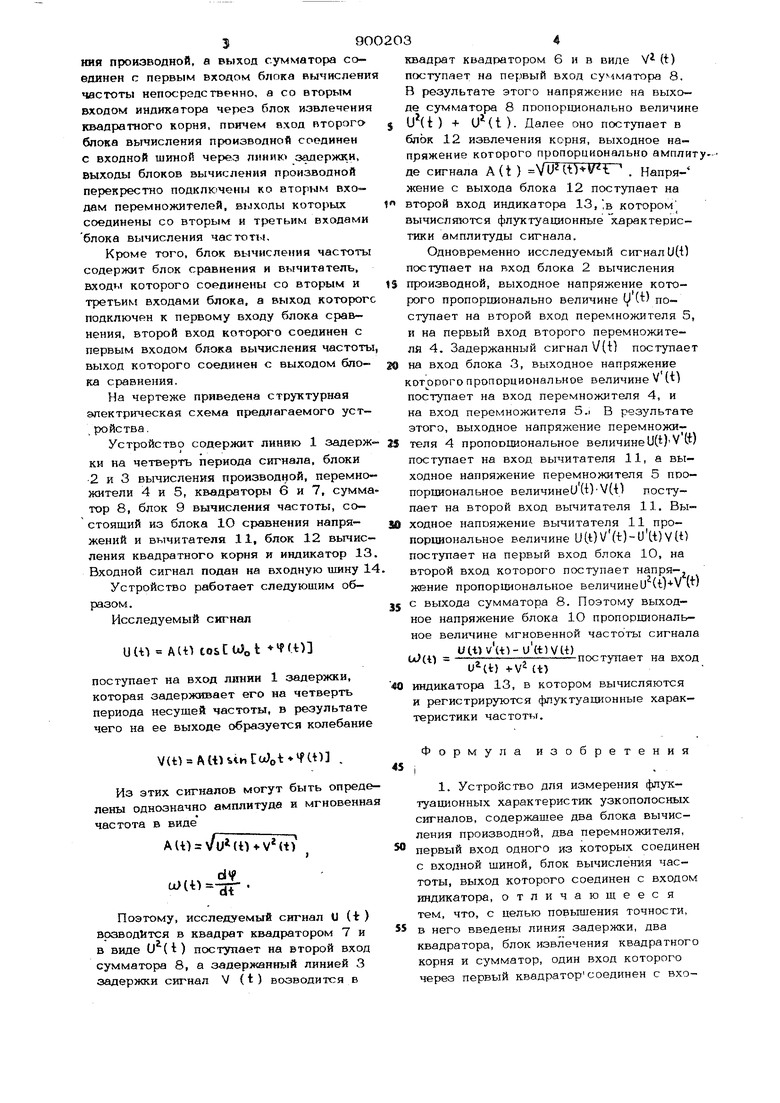

Поставленная цель достигается тем, что в устройство для измерения флуктуационных характеристик узкополосных сигналов, содержащее два блока вычисления производной, два перемножителя, пе{)ЫЙ вход одного из которых соединен с входной шиной, блок вычисления частоты, выход которого соединен с входом индикатора, введены линия задержки, два квадратора, блок извлечения квадратного корня и сумматор, один вход которого череЬ первый квадратор соединен с входом первого блока вычисления производной и с входной шиной, а второй вход сумматора через второй квадратор соединен с первым входом второго перемножителя и входом второго блока вычисле39НИИ производной, а выход сумматора соединен с первым входом блока вычислени частоты непосредственно, а со вторым входом индикатора через блок извлечени квадрютного корня, поячем вход второго блока вычисления производноЯ соединен с входной шиной через линию задержки, выходы блоков вычисления производной перекрестно подключены ко вторым входам перемножителей, выходы которых соединены со вторым и третьим входами блока вычисления частоты. Кроме того, блок вычисления частоты содержит блок ср авнения и вычитатель, входы которого соединены со вторым и третьим входами блока, а выход которог подключен к первому входу блока сравнения, второй вход которого соединен с первым входом блока вычисления частоты выход которого соединен с выходом блока срэавнения. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство содерлдат линию 1 задерж ки на четверть периода сигнала, блоки 2 и 3 вычисления производной, перемно жители 4 и 5, квадраторы б и 7, сумма тор 8, блок 9 вычисления частоты, состоящий из блока Ю сравнения напряжений и вычитателя 11, блок 12 вычисления квадратного корня и индикатор 13 Входной сигнал подан на входную шину 1 Устройство работает следующим образом. Исследуемый сигнал иШ A(t) cosCUot f(t) поступает на вход линии 1 задержки, которая задерживает его на четверть периода несущей частоты, в результате чего на ее выходе образуется колебание V(в A(i)s иCoJo ft 3 . Из этих сигналов могут быть опреде лены однозначно амплитуда и мгновенна частота в виде AU) /U(t)V(t) ,,ч « u(t)-jp. Поэтому, исследуемый сигнал U (t ) возводится в квадрат квадратором 7 и в виде и (t) поступает на второй вход сумматора 8, а задержанный линией 3 задержки сигнал V (t) возводится в 3 квадрат квадратором бив виде V (t) поступает на первый вход су -1матора 8, В результате этого напряжение на выходе сумматора 8 поопорилонально величине и (t ) + и (t ). Далее оно поступает в блок 12 извлечения корня, выходное напряжение которого пропорционально амплитуде сигнала A(t ) VlFIt)VH . Напря- жение с выхода блока 12 поступает на второй вход индикатора 13,IB котором вычисляются флуктуационные характеристики амплитуды сигнала. Одновременно исследуемый сигналив) поступает на вход блока 2 вычисления производной, выходное напряжение которого пропорционально величине (W поступает на второй вход перемножителя 5, и на первый вход второго перемножителя 4. Задержанный сигнал /(t} поступает на вход блока 3, выходное напряжение оторого пропорциональное величине V (t) поступает на вход перемножителя 4, и на вход перемножителя 5.i В результате этого, выходное напряжение перемножителя 4 пропооциональное величинеU(t)V (ч поступает на вход вычитателя 11, а выходное напряжение перемножителя 5 поопорциональное величинеи(1)У({) поступает на второй вход вычитателя 11. Выходное напряжение вычитателя 11 пропорциональное величине UCt)V (t)-U UjVlO поступает на первый вход блока 1О, на второй вход которого поступает напря-. жение пропорциональное величинеи (t)V (ч с выхода сумматора 8. Поэтому выходное напряжение блока Ю пропорциональное величине мгновенной частоты сигнала utt)vu)-uttWlt) -поступает на вход U(t) J Ct) индикатора 13, в котором вычисляются и регистрируются флуктуационные характеристики частоты. Формула изобретения 1. Устройство для измерения флуктуашюнных характеристик узкополосных сигналов, содержащее два блока вычисления производной, два перемножителя, первый вход одного из которых соединен с входной шиной, блок вычисления частоты, выход которого соединен с входом индикатора, отличающееся тем, что, с целью повышения точности, в него введены линия задержки, два квадратора, блок извлечения квадратного корня и сумматор, один вход которого через первый квадраторсоединен с входом первого блока вычисления производной и с входной шиной, а второй вход сумматора через втооой квадратор со единен с первым входом второго пере- множителя и входом второго блока вычисления производной, а выход сумматорй соединен с первым входом блока вычисления частоты непосредственно, а со вторым входом индикатора через блок извлечения квадратного корня, причем вход второго блока вычисления производной соединен с входной шиной через линию задержки выходы блоков вычисления производной перекрестно подключены ко вторым входам перемножитепей, выходы которых соединены со вторым и третьим входами блока вычисления ., частоты.

Источники информации, принятые во внимание при экспертизе

Г

Авторы

Даты

1982-01-23—Публикация

1980-05-27—Подача