(54) ЦИФРОВАЯ ИНТЕГРИРУЮЩАЯ СТРУКТУРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления цифровой интегрирующей структуры | 1978 |

|

SU789993A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Устройство управления цифровойиНТЕгРиРующЕй СТРуКТуРы | 1979 |

|

SU813429A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство для измерения параметров динамического процесса и управления с самоконтролем | 1986 |

|

SU1495751A1 |

| Система для контроля и управления | 1984 |

|

SU1247842A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

Изобретение относится к вычислительной технике и предназначено для решения широкого класса задач, описываемых системами дефференциальных и алгебраических уравнений и уравнениями, сводящимися к дифференциальным, а также для моделирования сложных процессов и объектов.

Известны цифровые интегрирующие структуры, содержащие решающие блоки, блоки коммутаций, блоки ввода и вывода и блоки управления, предназначенные для решения широкого класса задач, описьшаемых системами дифференциальных и алгебраических уравнений и уравнениями, сводящимися к дифференциальным 1 и 2.

Основным недостатком известных структур является большой расход оборудования для их построения вследствие больших затрат на коммутацию решающих блоков, не позволяющий практически создавать цифровые интегрирующие структуры (ЦИС) большой мощности, а также малогабаритные бортовые ЦИС.

Наиболее близкой по технической сущности к предлагаемой является ЦИС с одноразрядными приращениями, содержащая решающие блоки, блок вводи.

олок вывода,Олок управления,блок набора, блок коммутаций из коммутирующих эле ментов,причем выход блока набора схзединен с группой входов каждого решающего блока, а вход блока набор соединен с первым выходом каждого решающего блока, первый выход блока ввода соединен с первым входом каждого решающего блока, первый выход

10 блока управления соединен со входом блока ввода и вторым входом каждого решающего блока, а вход блока управления, соединен со вторым выходом каждого решающего блока и с первым входом бло

15 ка вывода, второй вход которого соединен со вторым выходом блока управления, второй выход блока ввода соединен с первым входом каждого коммутирующего элемента блока коммута20ции, первый выход каждого решгиошего блока соединен также со вторьми входами соответствующей группы коммутирующих элементов блока коммутации, а первая группа входов каждого решающего блока соединена также с выходами соответствующих групп коммутирующих элементов блока коммутации 3 .

Основным недостатком известной

30 ЦИС с одноразрядными приращениями

является большой расход оборудования , необходимый для ее построения вследствие больших затрат на коммутацию решающих блоков. При разработке ЦИС большой мощности эти затраты оказьаваются настолько велики, что реализация подобных ЦИС оказывается практически невозможной.

Цель изобретения - уменьшение затрат оборудования ЦИС с одноразрядными приращениями.

Поставленная цель достигается .тем, что в цифровую интегрирующую структуру/содержащую блок ввода, ре шающие блоки, блок управления, блок вывода и блок коммутации, причем первый выход блока ввода соединен с первым входом каждого решающего блока, выход блока управления соединен со входом блока ввода .и со вторым входом каждого решающего блока, а выход каждого решающего блока соединен со входом блока управления и с первым входом блока вывода, второй вход которого соединен со вторым выходом блока управления, дополнительно введены сдвигающие регистры . положительных приращений, сдвигающие регистры отрицательных приращений, программные регистры сдвига и дешифраторы, блок коммутации, состоящий из элементов И положительных и отрицательных приращений, причем третий выход блока управления соединен с первыми входами сдвигающих регистров положительных и отрицательных приращений и с управляющими входами программных регистров сдвига, первая группа информационных входов которых соединена с выходами выдачи программ коммутации блока ввода, выходы программных регистров сдвига соединены со второй группой информационных входов этого регистра и со входами соответствующего дешифратора, выходы каждого из которых соединены с первыми входами соответствующих элементов И положительных и отрицательных приращений блока коммутации, второй выход каждого решающего блока соединен со вторыми входами соответствующих элементов И положительных приращений блока коммутации, а третий выход.каждого решающего блока со вторыми входами соответствующих элементов И отрицательных приращений блока коммутации, -второй вход каждого сдвигающего регистра положительных -приращений соединен с выходом соответствующих элементов И положительных приращений блока коммутации а второй вход каждого сдвигающего регистра отрицательных приращений соединен с выходом соответствую1цих элементов И отрицательных приращени с.пока коммутации, первая группа вхо;;ов каждого решающего блока соедииема с соответствующей группой выходов соответствующего сдвигающего регистра положительных приращений, а вторая группа входов каждого решающего блока соединена с соответствующей группой выходов соответствующего сдвигающего регистра отрицательных приращений.

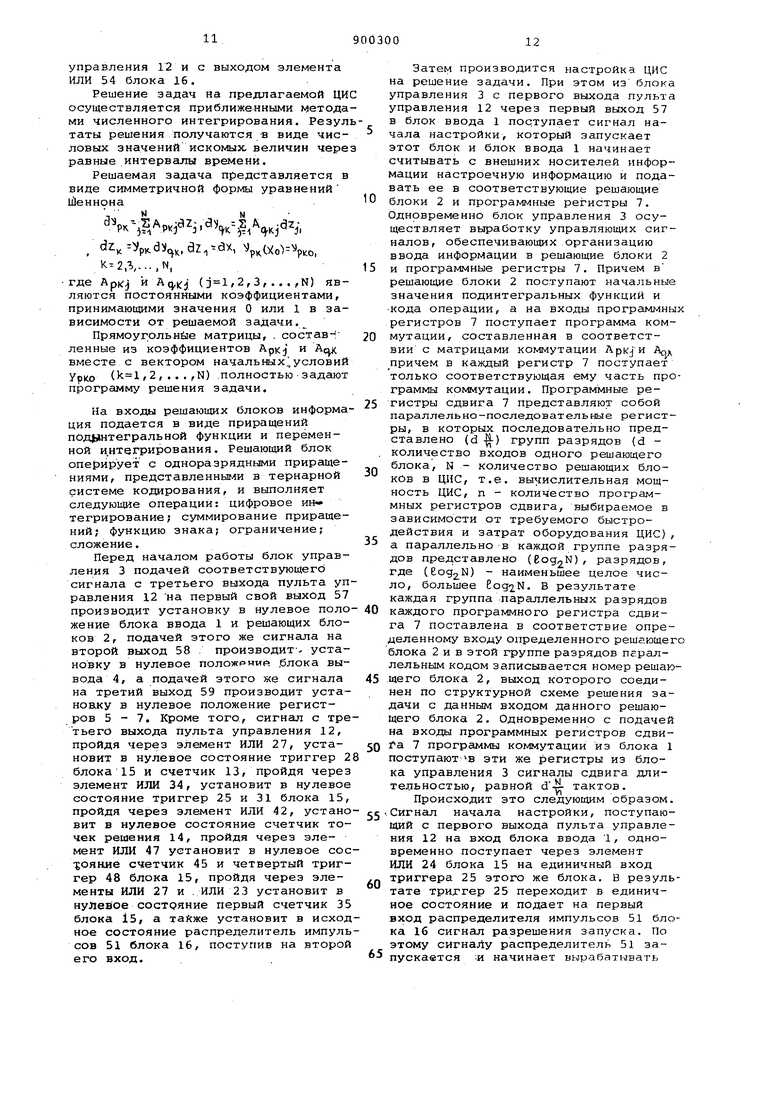

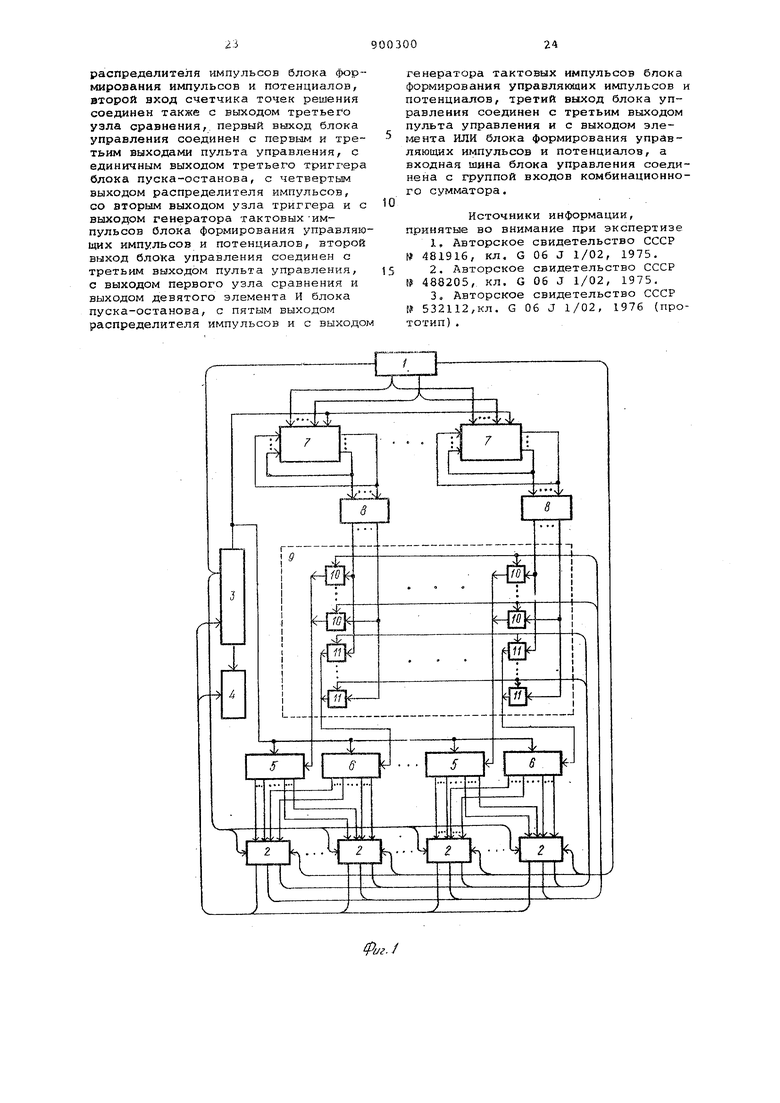

Кроме того, блок управления содержит пульт управления, счетчик итераций, счетчик точек решения, блок пуска-останова, включающий три узла сравнения, два счетчика, два элемента НЕ, четыре триггера, пять линий задержки, семь элементов ИЛИ, 5 девять элементов И, комбинационный сумматор и делитель частоты, блок .фсзрмирования управляющих импульсов и чютенциалов, включающий распределитель импульсов, узел триггеров, элемент И, элемент ИЛИ и генератор тактовых импульсов, причем первая группа выходов пульта управления и группа выходов счетчика итераций соединены соответственно с первой и второй группой входов первого узла сравнения блока пуска-останова, вторая группа выходов пульта управления и группа выходов, счетчика точек решения соединены соответственно с первой и второй группами входов второго узла сравнения -блока пуска-останова, выход первого узла сравнения блока пуска-останова соединен со входом первого элемента И этого же блока и через первый элемент НЕ - со входом второго элемента Иэтого же блока, выход которого через первую линию задержки соединен со входом первого элемента ИЛИ и со входом Q второго элемента ИЛИ этого же блока, выход которого соединен с единичным входом первого триггера этого же блока, выход первого элемента И блока пуска-останова соединен через вторую . линию задержки со входом третьего элемента ИЛИ этого же блока, выход которого соединен со вторым входом первого элемента ИЛИ и с нулевым входом второго триггера этого же блока, единичныйвыход которого соединен со входом третьего элемента И и со входом четвертого элемента И этого же блока, второй вход которого соединен с нулевым выходом первого триггера этого же блока, выход третьего элемента И блока пуска-останова соединен с единичным входом третьего триггера этого же блока, единичный выход которого соединен со входом пятого элемента И этого же 0 блока, выход которого через третью линию задержки соединен со входом четвертого элемента ИЛИ этого же Злока, выход которого соединен с нуле-вым входом первого триггера н с левым входом третьего триггера отi o же блока, выход четвертого элеме та И блока пуска-останова соединен со входом первого счетчика этого же блока, второй вход которого соедине с выходом первого элемента ИЛИ, а группа выходов - с группой входов шестого элемента И этого же блока, выход которого соединен со вторыми входами первого и второго элементов И этого же блока, -выход второго узла сравнения блока пуска-останова соединен со входом седьмого элемента и и через второй элемент ПЕ - со входом восьмого элемента И этого же блока, выход которого соединен со входом пятого элемента ИЛИ этого же блока, выход которого соединен со вторым входом второго элемента ИЛИ и с единичным входом второго тригге ра этого же блока, выход седьмого элемента И блока пуска-останова сое динен через четвертую линию задер жки со входом шестого элемента ИЛИ этого же блока, выход которого соединен с первым входом счетчика точек решения, группа выходов комбина ционного сумматора блока пуска-останова соединена с первой группой входов третьего узла сравнения этого же блока, вторая группа входов которого соединена с группой выходов второго счетчика этого же блока, а выход через пятую линию задержки соединен со вторыми входами седьмого и восьмого элементов И этого же блока и со входом седьмого элемента ИЛИ этого же блока, выход которого соединен с первым входом второго счетчика и с нулевым входом четвертого триггера этого же блока, единичный вход которого соединен также с выходом второй линии задержки этого же блока, а единичный выход - со входом девятого элемента И этого же блока, второй вход которого соединен с выходом де лителя частоты этого же блока, а выход - со вторым входом второго счет чика этого же блока,первый вход счет чика итераций соединен с выходом третьего элемента ИЛИ блока пускаостанова, второй вход - с единичным выходом третьего триггера блока . пуска-останова, а третий вход - с первым выходом распределителя импульсов блока формирования управляю щих импульсов и потенциалов, первый вход которого соединен с единичным выходом первого триггера блока пуска-останова, второй выход распредели теля импульсов блока формирования управляющих импульсов и потенциалов соединен со вторьв входом третьего элемента И блока пуска-останова, третий выход - со вторым входом пятого элемента И блокапуска-останова, а группа выходов - с группой входов узла триггеров блока формирования управляющих импульсов и потенциалов, первый выход которого соединен со входом элемента И блока формирования управляющих импульсов и потенциалов, второй вход которого соединен с нулевым выходом второго триггера блока пуска-останова, а выход - со входом элемента ИЛИ, второй вход которого соединен также с выходом чет зертого элемента И блока пуска-останова, выход генератора тактовых импульсов блока формирования управляющих импульсов и потенциалов соединен со вторым входом распределителя импульсов и третьим входом элемента И этого же блока, с третьим входом четвертого элемента И и входом делителя частоты блока пуска-останова, первый выход пульта .управления соединен с третьим входом второго элемента ИЛИ блока пуска-останова, второйвыход - со вторым входом пятого элемента ИЛИ блока пускаостанова, а третий выход - со входа-ми третьего, четвертого, шестого и седьмого элементов ИЛИ блока пускаостанова и третьим входом распределителя импульсов блока формирования управляющих импульсов и потенциалов, второй вход счетчика точек решения соединен также с выходом третьего узла сравнения, первый выход блока управления соединен с первым и третьим выходами пульта управления, с единичным выходом третьего триггера блока пуска-останова, с четвертым выходом распределителя импульсов, со вторым выходом узла триггеров и с выходом генератора тактовых импульсов блока формирования управляющих импульсов и потенциалов, второй выход блока управления соедийен с третьим выходом пульта управ- . ления, с выходом первого узла сравнения и с выходом девятого элемента И блока пуска-останова, с пятым выходом распределителя импульсов и с выходом генератора тактовых импульсов блока формирования управляющих импульсов и потенциалов, третий выход блока управления соединен с третьим выходом пульта управления и с выходом элемента -:ИЛИ блока формирования управляющих импульсов и потенциалов, а входная шина блока управления соединена с группой входов комбинационного сумматора. На фиг.1 представлена функциональная схема предлагаемой цифровой интегрирующей системы; на фиг.2 - схема реализации блока управления ЦИС. В состав ЦИС (фйг.1) входят блок ввода 1, решающие блоки 2, блок управления 3, блок вывода 4, сдвигающие регистры положительных приращений 5, сдвигающие регистры отрицательных приращений б, пpoгpa мныe регистры сдвига -7, дешифраторы 8, блок коммутации 9, содержащий элементы И положительного канала приращенцй 10 и элементы И отрицательного канала приращений 11..

Выход блока ввода 1 соединен с первым входом каждого решающего блока 2, второй вход каждого из которых соединен с первым выходом блока управления 3.

Первый выход каждого решающего блока 2 соединен со входом блока управления 3 и с первым входом блока вывода 4, второй вход которого соединен со вторым выходом блока управления 3, третий выход которого соединен с первым входом каждого сдвигающего регистра положительных приращений 5, с первым входом каждого сдвигающего регистра отрицательных приращений 6 и со входом каждого программного регистра сдвига 7,

Вход блока ввода 1 соединён также с первым выходом блока управления 3, а группа выходов блока ввода 1 соединена с первой группой входов каждого программного регистра сдвига 7.

Группа выходов каждого программного регистра сдвига 7 соединена со второй группой входов этого же -регистра 7 и с группой входов соответствующего дешифратора 8, выходы каждого из которых соединены с первыми входами соответствующих элементов И положительного канала приращений 10 блока коммутации 9 и с первыми входами соответствующих элементов И отрицательного канала приращений 11 блока коммутации 9.

Второй вход каждого сдвигающего регистра положительных приращений 5 соединен с выходом соответствующей группы элементов И положительного канала приращений 10 блока 9, а второй вход каждого сдвигающего регистра отрицательных приращений 6 сое.динен с выходом соответствующей группы элементов И отрицательного канала приращений.11 блока 9.

Первая группа входов каждого решающего блока 2 соединена с соответствующей группой выходов соответствующего сдвигающего регистра положительных приращений 5,а-..вторая группа входов - с соответствующей группой выходов соответствующего сдвигающего регистра отрицательных приращений 6.

Второй выход каждого решающего блока 2 соединен со вторыми входами соответствующих групп элементов И положительного канала приращений 10 блока коммутаций 9, а третий выход каждого решающего блока 2 соединен со вторыми входс1ми соответствующих групп элементов И отрицательного канала приращений 11 блока коммутации 9.

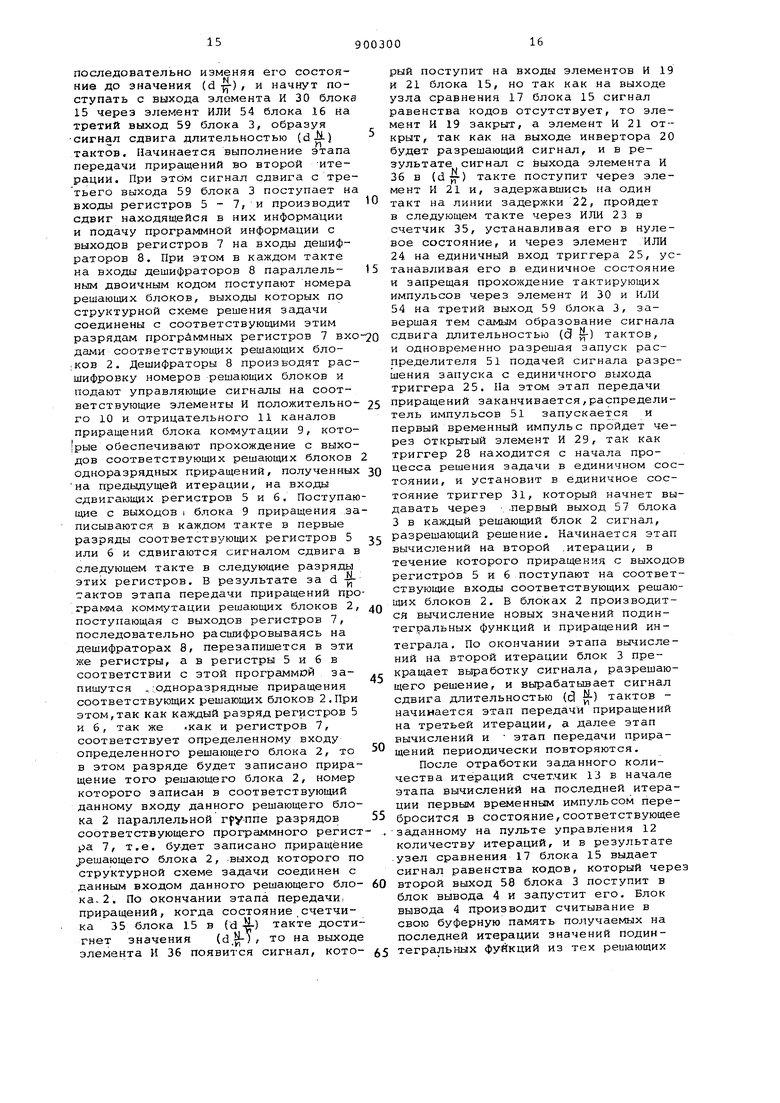

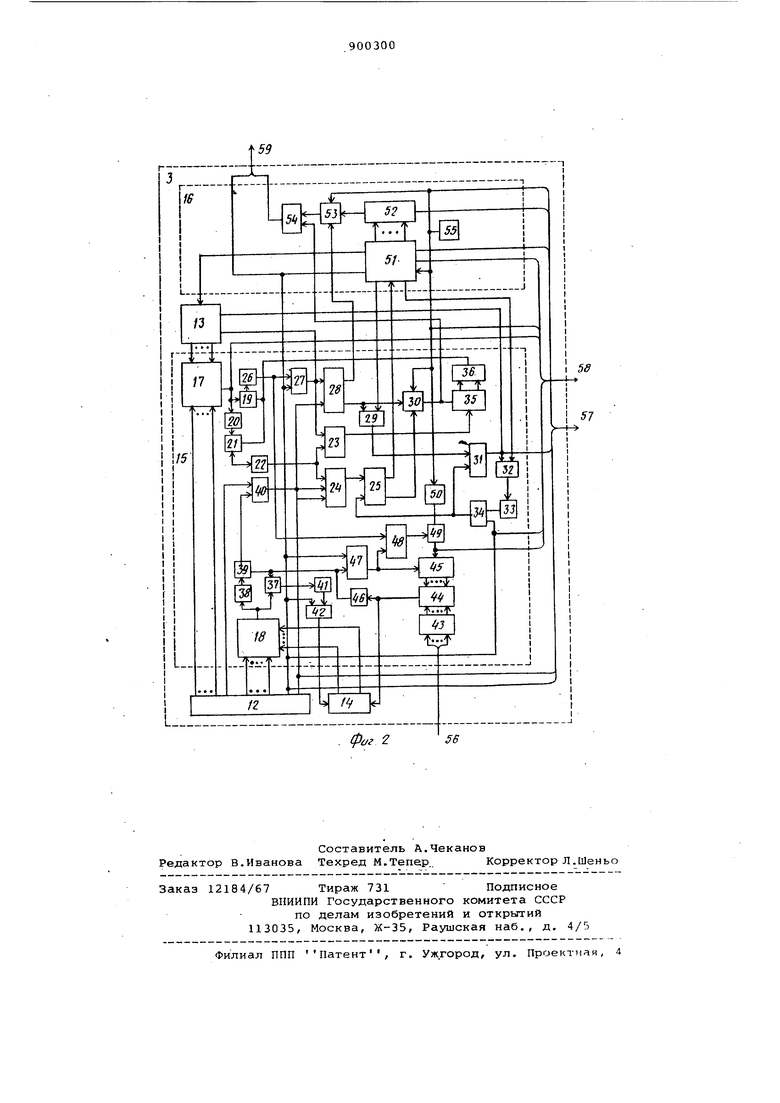

В состав блока управления 3 предложенной ЦИС (фиг.2) входят пульт управления 12, счетчик итераций 13, счетчик точек решения 14, блок пуска-останова 15, содержащий первый узел сравнения 17, второй узел сравнения 18, первый элемент И 19, первый элемент НЕ 20, второй элемент И 21, первую линию задержки 22, первый элемент ИЛИ 23, второй элемент ИЛИ 24, первый триггер 25, вторую линию задержки 26, третий элемент ИЛИ 27, второй триггер 2а, третий элемент И 29, четвертый элемент И 30 третий .триггер 31, пятый элемент И 32, третью линию задержки 33, четвертый элемент ИЛИ 34, первый счетчик 35, шестой элемент И 36,.- седьмой элемент И 37, второй элемент НЕ 38, восьмой элемент И 39, пятый элемент ИЛИ 40, четвертую линию задержки 41, шестой элемент ИЛИ 42, комбинационный сумматор 43, третий узел сравнения 44, второй счетчик 45, пятую линию задержки 46, седьмой элемент ИЛИ 47, четвертый триггер 48, . девятый элемент И 49, делитель частоты 50, блок формирования управляющих импульсов и потенциалов 16, содержащий распределитель импульсов 51, узел 52 триггеров, элемент И 5.3, элемент .ИЛИ 54, генератор тактовых импульсов 55, входную шину 56 блока управления, первый выход 57 блока управления, второй выход 58 блока управления, третий выход 59 блока управления.

Первая группа вькодов пульта управления 12 и группа выходов счетчика итераций 13 соединены соответственно с первой и второй группой входов первого узла сравнения 17 блока пуска-останова 15.

Вторая группа выходов пульта управления 12 и группа выходов счетчика точек решения 14 соединены соответственно с первой и второй группой входов второго узла сравнения 18 блока 15,

Выход первого узла сравнения 17 блока 15 соединен со входом первого элемента И 19 этого же блока и через первый элемент НЕ 20 - со входом второго элемента И 21 этого же блока, выход которого через первую линию задержки 22 соединен со входом первого элемента ИЛИ 23 этого же блока и со входом второго элемента ИЛИ 24 этого же блока, выход которого соединен с единичным входом первого триггера 25 этого же блока.

Выход первого элемента И 19 блока 15 соединен через вторую линик зга держки 26 со входом треп..м-о -Ш.ч-юнта ИЛИ 27 этого же б.пока, Hf.iXui К-торого соединен со вторым входом пер вого элемента ИЛИ 23 и с нулевым входом второго триггера 28 этого жеблока, единичный выход которого соединен со входом третьего элемента И 29и со входом четвертого элемента И 30этого же блока, второй вход которого со,единен с нулевым выходом первого триггера 25 этого же блока. Выход третьего элемента И 29 блока 15 соединен с единичным входом третьего триггера 31 этого же блока единичный выход которого соединен со входом пятого элемента И 32 этого же блока, выход которого через третью линию задержки 33 соединен со входом четвертого элемента ИЛИ 34, выход которого соединен с нулевым входом первого триггера 25 и с нулевым входом Т:ретьего триггера 31 бло ка 15. Выход четвертого элемента И 30 блока 15 соединен со входом первого счетчика 35 этого же блока, второй вход которого соединен с выходом первого элемента ИЛИ 23, а группа выходов - с группой входов шестого элемента И 36 этого же блока, выход которого соединен со вторыми входами первого 19 и второго 21 элементов И этого же блока. Выход второго уэла сравнения 18 блока 15 соединен со входом седьмого элемента -И 37 и через второй элемен НЕ 38 - со входом восьмого элемента И 39 этого же блока, выход котор го соединен со входом пятого длемен та .ИЛИ 40, выход которого-соединен со вторым второго элемента ИЛИ 24 и с единичны - входом второго триггера 28 блока 15. Выход седьмого элемента И 37 бло ка 15 соединен через четвертую лини1О задержки 41 со входом шестого элемен та ИЛИ 42 этого же блока, выход кото рого соединен с первым входом счетчи ка точек решения 14. Входная шина 56 блока управления соединена с группой входов комбинационного сумматора 43 блока 15, груп па выходов которого соединена с пер вой группой входов третьего узла сравнения 44, вторая группа входов которого соединена с группой выходо второго счетчика 45 этого же блока, а выход через пятую линию, задержки .46 соединен со вторыми входами седь мого 37 и восьмого 39 элементов И этого же блока и . входом седьмого элемента ИЛИ 47 этого же блока, выход которого, соединен с первым входом второго счетчика 45 и с нулевым вхо дом четвертого триггера 48 этого же блока, единичный вход которого соединен также с выходом второй линий задержки 26 этого же блока, а едини ный выход - со входом девятого элемента И 49, второй вход которого соединен с выходом делителя частоты 50, а выход - со вторым входом второго счетчика 45. Первый вход счетчика итераций 13 соединен с выходом третьего элемента ИЛИ 27 блока 15, второй вход - с единичным выходом третьего триггера 31 блока 15, а третий вход - с первым выходом распределителя импульсов 51 блока 16, первый вход которого соединен с единичным выходом первого триггера 25 блока 15. Второй выход распределителя импульсов 51 соединен со вторым входом третьего элемента И 29 блока 15,. третий выход - со вторым входом пя.того элемента И 32 блока 15, а группа выходов - с группой входов узла триггеров 52 блока 16, первый выход которого, соединен со входом элемента И 53 блока 16, второй вход которого соединен с нулевым выходом второго триггера 28 блока 15, а выход со входом элемента ИЛИ 54, второй вход которого соединен также с выходом четвертого элемента и 30 блока 15. Выход генератора тактовых импульсов 55 блока 16 соединен со вторь входом распределителя импульсов 51 и третьим входом элемента И 53 блока 16, с третьим входом четвертого элемента И 30 и входом делителя частоты 50 блока 15. Первый выход пульта управления 12 соединен с третьим входом элемента ИЛИ 24 блока 15, второй выход - со вторым входом пятого элемента ИЛИ 40 блока 15, а третий выход - со .входом третьего элемента ИЛИ 27, четвертого элемента ИЛИ 34, шестого элемента ИЛИ 42 и седьмого элемента ИЛИ 47 блока 15- и с третьим входом распределителя импульсов 51 блока 16. Второй вход счетчика точек решения 14 соединен также с выходом третьего узла сравнения 44 блока 15. Первый выход 57 блока управления соединен с первым и третьим выходами пульта управления 12, с единичным выходом третьего триггера 31 блока 15, с четвертый выходом распределителя импульсов 51, со вторым выходом узла триггеров 52 и с выходом генератора тактовых импульсов 55 блока 16. Второй выход 58 блока управления соединен с третьим выходом пульта управления 12, с выходом первого уэла сравнения 17 и Выходом девятого элемента И 49 блока 15, с пятым выходом распределителя импульсов 51 и с выходом генератора тактовых импульсов 55 блока 16. Третий выход 59 блока управления соединен с третьим выходом пульта управления 12 и с выходом элемента ИЛИ 54 блока 16. Решение задач на предлагаемой ЦИ осуществляется приближенными метода ми численного интегрирования. Резул таты решения получаются -в виде числовых значений искомых, величин чере равные интервсшы времени. Решаемая задача представляется в виде симметричной формы уравнений UieHHOHa .., , dr Z.-dX, )Vo, К-2Л---, где ApKj и Aej,; (j l,2,3, .. . ,N) являются постоянными коэффициентами, принимающими значения О или 1 в зависимости от решаемой задачи. Прямоуг;ольнй1е матрицы, . составленные из коэффициентов Арк-) и вместе с вектором начальных. условий Урко (,2,...,N) .полностью задают программу решения задачи. На входы решающих блоков информа ция подается в виде приращений подынтегральной функции и переменной интегрирования. Решающий блок опе зирует с одноразрядными приращениями, представленными в тернарной системе кодирования, и выполняет следующие операции: цифровое ин тегрирование; суммирование приращений; функцию знака; ограничение; сложение. Перед началом работы блок управления 3 подачей соответствующего сигнала с третьего выхода пульта уп равления 12 на первый свой выход 57 производит установку в нулевое поло жение блока ввода 1 и решающих блоков 2, подачей этого же сигнала на второй выход 58 . производит- установку в нулевое ПОЛОЖРНИР блока вывода 4, а подачей этого же сигнала на третий выход 59 производит устаHOBjty в нулевое положение регистров 5-7. Кроме того, сигнал с тре тьего выхода пульта управления 12, пройдя через элемент ИЛИ 27, установит в нулевое состояние триггер 2 блока 15 и счетчик 13, пройдя через элемент ИЛИ 34, установит в нулевое состояние триггер 25 и 31 блока 15 пройдя через элемент ИЛИ 42, устано вит в нулевое состояние счетчик точек решения 14, пройдя через элемент ИЛИ 47 установит в нулевое сос ояние счетчик 45 и четвертый триггер 48 блока 15, пройдя через элементы ИЛИ 27 и .ИЛИ 23 установит в нулевое состряние первый счетчик 3 блока 15, а тайже установит в исход ное состояние распределитель импул сов 51 блока 16, поступив на второй его вход. Затем производится настройка ЦИС на решение задачи. При этом из блока управления 3 с первого выхода пульта управления 12 через первый вьисод 57 в блок ввода 1 поступает сигнал начала настройки, который запускает этот блок и блок ввода 1 начинает считывать с внешних носителей информации настроечную информацию и подавать ее в соответствующие решающие блоки 2 и программные регистры 7. Одновременно блок управления 3 осуществляет выработку управляющих сигналов, обеспечивающих организацию ввода информации в решающие блоки 2 и программные регистры 7. Причем в решающие блоки 2 поступают начальные значения подинтегральных функций и кода операции, а на входы программных регистров 7 поступает программа коммутации, составленная в соответствии с матрицами коммутации Арк,)и АО причем в каждый регистр 7 поступает только соответствующая ему часть программы коммутации. Программные регистры сдвига 7 представляют собой параллельно-последовательные регистры, в которых последовательно представлено (d -) групп разрядов (d количество входов одного решающего блока, N - количество решающих блокОв в ЦИС, т.е. вычислительная мощность ЦИС, п - колич:ество программных регистров сдвига, выбираемое в зависимости от требуемого быстродействия и затрат оборудования ЦИС), а параллельно в каждой группе разрядов представлено (), разрядов, где (eog2N) - наименьшее целое число, большее . В результате каждая группа параллельных разрядов каждого программного регистра сдвига 7 поставлена в соответствие определенному входу определенного решающего блока 2 и в этой группе разрядов параллельным кодом записывается номер решающего блока 2, выход которого соединен по структурной схеме решения задачи с данным входом данного решающего блока 2. Одновременно с подачей на входы программных регистров сдвиз а 7 программы коммутации из блока 1 поступают-B эти же регистры из блока управления 3 сигналы сдвига длительностью, равной d- тактов. Происходит это следующим образом. Сигнал начала настройки, поступающий с первого выхода пульта управления 12 на вход блока ввода 1, одновременно поступает через элемент ИЛИ 24 блока 15 на единичный вход триггера 25 этого же блока, в результате триггер 25 переходит в единичное состояние и подает на первый вход распределителя импульсов 51 блока 16 сигнаш разрешения запуска. По этому сигналу распределитель 51 запускается -и начинает вырабатывать

распределение временных импульсов, которые с выходов распределителя 51 поступят на единичные и нулевые входы триггеров узла 52 блока 16 л произведут выработку управляющих сигналов соответствующей длительности (эта длительность зависит от количества разрядов и регистре иодинтегральной функции, в регистре кода операций и т.п.), которые со второго выхода узла 52, также как и распределенные временные импульсы с четвертого выхода распределителя 51, будут поступать через первый выход 57 блока управления 3 в блок ввода 1 и решающие блоки 2 для обеспечения организации ввода настроенной информации Кроме того, управляющий потенциал длительностью (d ) тактов с первого выхода узла 52 поступает на вход элемента И 53 блока 16 и, так как триггер.28 блока 15 после установки в исходное состояние выдает с нулевого выхода разрешающий сигнал на другой вход элемента И 53 блока 16, то в течение (d ) тактов в каждом цикле работы распределителя 51 через открытый элемент И 53 будут проходить тактирующие импульсы с выхода генератора 55 и получающиеся в результате в каждом цикле сигналы сдвига длительностью (d ) тактов с выхода элемента И 53 через элемент ИЛИ 54 и третий, выход 59 блока управления 3 будут поступать на входы регистров 7 обеспечивая запись считываемой блоком 1 с внешнего носителя информации программы коммутации в регистр 7, причем в каждый регистр 7 будет записываться программа коммутации лишь той группы решающих блоков 2, которая соответствует этому регистру (т.е. будет записываться вся соответ ствующая только этому регистру часть программы коммутации).

После ввода всей настроечной информации процесс настройки ЦИС заканчивается и начинается выполнение процесса решения задачи.Процесс решения задачи на каждой итерации разбивается на два этапа - этап вычислени и этап передачи приращений. Лиа1ь на первой итерации этап передачи приращений, вследствие их нулевого значени отсутствует.Перед началом решения в блоке управления 3 на пульте 12 задается необходимое количество итераций, в течение которого вычисляется точка решения и задается необходимое число точек решения. Затем на пульте управления 12 блока 3 вырабатывается команда Пуск и соответствующий сигнал со второго выхода пульта управления-12 поступает через элемент ИЛИ 40 блока 15 на единичный вход триггера 28 этого же блока, устанавливая его в единичное состояние, и с выхода элемента ИЛИ 40 через элемент ИЛИ 24 - на единичный вход триггера 25 блока 15, подтверждая его единичное состояние. В результате триггер 28 блока 15 закроет элемент И 53 блока 16, запретив тем самым выработку сигнешов сдвига, обеспечивающих ввод программы коммутации в, регистры 7.Одновременно сигнал с единичного выхода триггера 28 блока 15 откроет элемент И 29 этого же блока и первый временный импульс, соответствующий начашу итерации, со второго выхода распределителя 51 блока 16 пройдет через элемент И 29 и установит в единичное состояние триггер 31 блока 15, который начнет выдавать на первый выход 57 блока управления 3 сигнал, разрешающий решение. Этот сигнал с выхода блока 3 поступает в решающие блоки 2 и в них производится выполнение этапа вычислений первой итерации, при этом также в решающие блоки 2 из блока 3 с выходов распределителя 51 и узла 52 триггеров поступают временные импуль сы и управляющие потенциалы, обеспечивающие процесс вычислений. Одновременно сигнал с единичного выхода триггера 31 блока 15 поступает на управляющий вход счетчика 13, разрешая суммирование, и первый временный импульс, соответствующий итерации, поступит с выхода распределителя 51 блока 16 и перебросит счетчик 13 в состояние, равное единице. По окончании этапа вычислений на первой итерации последний временный импульс соответствующий концу итерации, пройдет с третьего выхода распределителя 51 блока 16 через открытый элемент И 32 блока 15 и, задержавшись на оди такт на линии задержки 33, поступит через элемент ИЛИ 34 на нулевые входы триггеров 25 и 31 блока 15 и установит их в нулевое состояние, В результате триггер 25 блока 15 прекоаТИТ выработку сигнала разрешения запуска в распределитель 51 блока 16 и распределитель 51 перестанет выдавать на выход 57 блока 3 распределенные временные импульсы, -а узел триггеров -52 блока 16 - управляющие потенциалы, необходимые для организации процесса вычислений в.решающих блоках 2, а триггер 31 блока 15 пре:.ратит выработку сигнала, разрешающего решение. На этом этап вычислений первой итерации заканчивается и начиная со следующего такта, тактирующие импульсы с выхода генератора 55 блока 16 через открытый элемент И 30 блока 15 (так как триггер 25 после окончания этапа вычислений первой итерации установился в нулевое состояние, а триггер 28 находится с начала процесса решения задачи в единичном состоянии) начнут поступать на суммирующий счетчика 35,

последовательно изменяя его состояние до значения (d ) , и начнут поступать с выхода элемента И 30 блока 15 через элемент ИЛИ 54 блока 16 на третий выход 59 блока 3, образуя

сигнал сдвига длительностью (d-bLj тактов. Начинается выполнение этапа передачи приращений во второй -итерации. При этом сигнал сдвига с третьего выхода 59 блока 3 поступает на входы регистров 5 - 7, и производит сдвиг находящейся в них информации и подачу программной информации с выходов регистров 7 на входы дешифраторов 8. При этом в каждом такте на входы дешифраторов 8 параллельным двоичным кодом поступают номера решающих блоков, выходы которых по структурной схеме решения задачи соединены с соответствуюощми этим разрядам программных регистров 7 вхо дами соответствующих решающих бло;Ков 2. Дешифраторы В производят расшифровку номеров решающих блоков и подают управляющие сигналы на соответствующие элементы И положительно го 10 и отрицательного 11 каналов приращений блока коммутации 9, кото|рые обеспечивают прохождение с выходов соответствующих решающих блоков одноразрядных приращений, полученных

на предыдущей итерации, на входы сдвигающих регистров 5 и 6. Поступающие с выходов 1 блока 9 приращения .записываются в каждом такте в первые разряды соответствующих регистров 5 или 6 и сдвигаются сигналом сдвига в следующем такте в следующие разряды этих регистров, В результате за d тактов этапа передачи приращений программа коммутации решающих блоков 2, поступающая с выходов регистров 7, последовательно расшифровываясь на дешифраторах 8, перезапишется в эти же регистры, а в регистры 5 и б в соответствии с этой программой запишутся , одноразрядные приращения соответствующих решающих блоков 2,При этом,так как каждый разряд регистров 5 и б, так же .как и регистров 7, соответствует определенному входу определенного решающего блока 2, то в этом разряде будет записано приращение того решающего блока 2, номер которого записан в соответствующий данному входу данного решающего блока 2 параллельной rfy-nne разрядов соответствующего программного регист ра 7, т.е. будет записано приращение

)ешающего блока 2, -выход которого по структурной схеме задачи соединен с данным входом данного решающего блока-2. По окончании этапа передачи, приращений, когда состояние счетчика 35 блока 15 в (d 4-) такте дости(cl.H-1

то на выходе

гнет значения

элемента И 36 появится сигнал, кото- 5

рый поступит на входы элементов И 19 и 21 блока 15, но так как на выходе узла сравнения 17 блока 15 сигнал равенства кодов отсутствует, то элемент И 19 закрыт, а элемент И 21 открыт, так как на выходе инвертора 20 будет разрешающий сигнаш, и в результате сигнал с выхода элемента И 36 в (d-) такте поступит через элемент И 21 и, задержавшись на один такт на линии задержки 22, пройдет в следующем такте через ИЛИ 23 в счетчик 35, устанавливая его в нулевое состояние, и через элемент ИЛИ 24 на единичный вход триггера 25, устанавливая его в единичное состояние и запрещая прохождение тактирующих импульсов через элемент И 30 и ИЛИ 54 на третий выход 59 блока 3, завершая тем самым образование сигнала сдвига длительностью (d ) тактов, и одновременно разрешая запуск распределителя 51 подачей сигнала разрешения запуска с единичного выхода триггера 25. Па этом этап передачи приращений заканчивается,распределитель импульсов 51 запускается и первый временный импульс пройдет через открытый элемент И 29, так как триггер 28 находится с начала процесса решения задачи в единичном состоянии, и установит в единичное состояние триггер 31, который начнет выдавать через . .первый выход 57 блока 3 в каждый решающий блок 2 сигнал, разрешающий решение. Начинается этап вычислений на второй .итерации, в течение которого приращения с выходо регистров 5 и б поступают на соответствующие входы соответствующих решающих блоков 2. В блоках 2 производится вычисление новых значений подинтегральных функций и приращений интеграла. По окончании этапа вычислений на второй итерации блок 3 прекращает выработку сигнала, разрешающего решение, и вырабатывает сигнал сдвига длительностью (d ) тактов начинается этап передачи приращений на третьей итерации, а далее этап вычислений и этап передачи приращений периодически повторяются.

После отработки заданного количества итераций счетчик 13 в нача.пе этапа вычислений на последней итерации первым временным импульсом перебросится в состояние,соответствующее заданному на пульте управления 12 количеству итера.ций, и в результате .узел сравнения 17 блока 15 выдает сигнал равенства кодов, который чере второй выход 58 блока 3 поступит в блок вывода 4 и запустит его. Блок вывода 4 производит считывание в свою буферную память получаемых на последней итерации значений подинтегральных фуЯкций из тех решающих блоков 2, в коде операций которых имеется признак печати. После- прове дения этапа вычислений на последней итерации выполнится этап передачи приращений, по окончанию которого на выходе элемента И 36 блока 15 появится сигнал и, так как на выходе узла 17 имеется сигнал равенства ко дов, то элемент И 21 будет закрыт и не пропустит сигнал на запуск распределителя 51, но в то же время элемент И 19 будет открыт и сигнал с выхода элемента И 36 пройдет через элемент И 19 и, задержавшись на один такт на линии задержки 26, пройдет через элемент ИЛИ 27 и установит в нулевое состояние триггер 28 блока 1Ь и счетчик 13, а пройдя еще через элемент ИЛИ 23, установит в нулевое состояние счетчик 35 блока 15. Па этом процесс вычисления первой точки решения заканчивается. В то же время сигнал с выхода линии задержки 26 поступит на единичный вход триггера 48 и перебросит его в единичное состояние. В результате триггер 48 откроет элемент И 49 и разрешит прохождение импульсов с вы хода делителя частоты 50, который понижает частоту следования тактирую щих импульсов до частоты работы печатающего устройства, на суммирующий вход счетчика 45 блока 15 и на второй выход 58 блока 3, как импульсов опроса, по которым блок 4 начинает вывод информации на печать. Одновременно счетчик 45 блока 15 про изводит подсчет импульсов , а узел 44 производит сравнение значения счетчи ка 45 со значением суммы на выходе сумматора 43, на входы которого поступают сигналы из тех решающих блоков 2,. в коде операций которых имеет ся признак печати, т.е. значение на выходе сумматора 43 блока 15 соответ ствует числу решающих блоков 2, из которых выводится информация. После окончания печати всей выводимой информации данной точки решения значение счетчика 45 блока 15 становится равны - значению суммы на выходе сумматора 43 и узел 44 блока 15 выдает сигнал равенства кодов, который пройдет на вход счетчика 14 точек ре шения и перебросит его в состояние, равное единице, кроме того, этот сиг нал пройдет через пятую линию задерж ки 46 и элемент ИЛИ 47 и установит в нулевое состояние счетчи-к 45 и триггер 48, запретив тем самым прохождение импульсов через элемент И 49. Па этом вывод информации на пе чать закончится, а сигнал равенства кодов с выхода узла 44 через линию задержки 46 поступит также на входы элементов и 37 и И 39, но так как на выходе узла сравнения 18 блока 15 сигнал равенства кодов еще отсутствует, то элемент И 37 закрыт, а элемент И 39.открыт, так как на выходе элемента ПЕ 38 будет разрешающий сигнал. В результате сигнал с выхода линии задержки 46 пройдет через открытый элемент И 39 и поступит через элемент ИЛИ 40 блока 15 на единичный вход триггера 28, устанавливая его в единичное состояние, и с выхода элемента ИЛИ 40 через элемент ИЛИ 24 - на единичный вход триггера 25, также устанавливая его в единичное состояние. Начнется этап вычислений на первой итерации следующей точки решения. После отработки необходимого количества точек решения счетчик 14 перебросится к состояние, соответствующее заданному на пульте управления 12 количеству точек решения, и. узел сравнения 18 блока 15 выдаст сигнал равенства кодов, который закроет элемент И 39, запретив тем са-мым прохождение сигнала с выхода узла 44, запускающего блок управления на вычисление следующей точки решения, и откроет элемент И 37. В результате сигнал с выхода узла 44 после печати информации последней точки решения пройдет, задержавшись на линии задержки 46, через элемент И 37 , линию задержки 41 и элемент ИЛИ 42 и установит счетчик 14 точек решения в нулевое состояние, а также установит в нулевое состояние триггер 48 и счетчик 45, пройдя элемент ИЛИ 47. На этом процесс решения задачи заканчивается. Таким образом, предлагаема ЦИС с одноразрядными приращениями, производя решение задачи, выполняет на каждой итерации этап вычислений и этап передачи прирашений последовательно во . времени, при этом предлагаемая ЦИС позволяет значительно сократить затраты оборудования. Если затраты оборудования на известную ЦИС с одновременными прираще ниями составляют . : иИс- РБ К9 АОП, где Q-g - затраты оборудования на один решающий блок; Q - затраты оборудования на один коммутирующий ЭлементQ - затраты оборудования на орАО ганизацию управления, ввода и вывода информации, составляющие обычно не более 10% от общих затрат, то затраты оборудования на предлагаемую ЦИС с одноразрядными приращениями составляют uc-- C p,-H(d ).2K,(d)Qp-V, . где Qt, - затраты оборудования на один разряд сдвигающего регистра Одщ - .затраты оборудования на один дешифратор; Q - затраты оборудования на один двухвходовой элемент И (на двухвходовой элемент И- И-НЕ с открытЕЛм коллектором или аналогичный ключ) В то же время при реализации ЦИС с одноразрядными приращениями на интегральных микросхемах серий К164 и К 502 эти затраты составляют: Qpg 3-5 корпусов микросхем; ,5 корпуса микросхемы; Qp корпуса микросхемы, корпусов микросхем; Qyi v корпуса микросхему/тогда Оцмс ,-f((,5 .vic t,-N -dNre;og;jNl - -2dN;jg-vn|N-v2viN ,SdN g4--1,5-dN (reog-.)-vf-yi Учитывая, что , N , n 5-50, получим 5-H,5(i47)(5O-f-fOOO) ,4 C)f;MC (.l-f7)(reog-,,(.60vtOOO)1+2y-|(450) Таким образом, предлагаемая ЦИС с одноразрядными приращениями в зависимости от требуемой вычислительной мощности структуры и быстродействия обеспечивает сокращение затра оборудования в 13-150 раз в сравнении с известной ЦИС с одноразрядными приращениями с учетом реализации их на интегральных микросхемах серий Мб 4 и К502 и тем самым позволит создавать малогабаритные настол ные ЦИС, бортовые ЦИС средней мощно ти, а также позволит практически со давать ЦИС большой мощности, Формула изобретения 1. Цифровая интегрирующая структ ра, содержащая блок ввода, решающие блоки, блок управления, блок вывода блок коммутации .причем первый выход блока ввода соединен с первыми входами решающих блоков, первый вых блока управления соединен со входом блока ввода и вторыми входами решаю щих блоков, а выходы решающих блоко соединены со входом блока управлени и с первым входом блока .вывода, вт рой вход которого соединен со вторы выходом блока управления, отличающаяся тем, что, с целью сокращения затрат оборудования, в нее введены сдвигающие регистры положительных приращений, сдвигающие регистры отрицательных приращений, программные регистры сдвига и дешифраторы, а блок ко(Ф1утации состоит из элементов И положительных и отрицательных приращений, причем третий выход блока.управления соединен с первыми входами сдвигающих регистров положительных и отрицательных приращений и с управляющими входами программных регистров сдвига, первая группа информационных входов которых соединена с выходами выдачи программ коммутации блока ввода, выходы программньах регистров сдвига соединены со второй группой информационных входов этого регистра и со входами соответствующего дешифратора, выходы, каждого из которых соединены с первыми входами соответствующих элементов И положительных приращений блока коммутации и с первыми входами соответствующих элементов .И отрицательных приращений блока коммутации, второй выход-каждого решающего блока соединен со вторыми входами соответствующих элементов И положительных приращений блока коммутации, а третий /.выход каждого решающего блока - со вторЕлми входами соответствующих элементов И отрицательных приращений блока коммутации, второй вход каждого сдвигающего регистра положительных приращений соединен с выходом соответствующих элементов И положительных приращений блока коммутации, а второй вход каждого сдвигающего регистра отрицательных приращений соединен с выходом соответствующих элементов И отрицательных приращений блока коммутации, первая группа входов каждого решающего блока соединена с соответствующей группой выходов соответствующего сдвигающего регистра положительных приращений, а вторая группа входов каждого решающего блока соединена с соответствующей группой выходов соответствующего регистра отрицательных приращений. 2. Цифровая интегрирующая структура по п. 1, отличающаяс я тем, что блок управления содержит пульт управления, счетчик итераций, счетчик точек решения, блок пуска-останова, включающий три узла сравнения, два счетчика, два элемен та НЕ, четыре триггера, пять линий задержки, семь элементов -ИЛИ, девять элементов И, комбинационный сумматор и делитель частоты, блок формирования управляющих импульсов и потенциалов, включающий распределитель импульсов, .узел триггеров, элемент И, элемент ИЛИ и генератор тактовых имnyj bcoB, причем первая группа выходов пульта управления и группа выходов счетчика итераций соединены соответственно с первой и второй группами входов первого узла сравнения блока пуска-останова, вторая группа выходов пульта управления и группа выходов счетчика точек решения соеди нены соответственно с первой и второй группами входов второго узла сравнения блока пуска-останова, выхо первого узла сравнения блока пускаостанова соединен со входом первого элемента И этого же блока и через первый элемент НЕ - со входом второго элемента И этого же блока, выход которого через первую линию задержки соединен со входом первого элемента ИЛИ и со входом второго эле мента ИЛИ этого же блока, выход которого соединен с единичным входом первого триггера этого же блока, выход первого элемента И блока пускаостанова соединен через вторую линию задержки со входом третьего элемента ИЛИ этого же блока, выход которого соединен со вторым входом пер вого элемента ИЛИ и с нулевым входом второго триггера этого же блока, единичный выход которого соединен со входом третьего элемента И и со входом четвертого элемента И этого же бл,ока, второй вход которого соединен с нулевым выходом перйого триг гера этого же блока, выход третьего элемента И блока пуска-останова соединен с единичным входом третьего триггера этого же блока, единичный выход которогс соединен со входом пятого элемента И этого же блока, выход которого через третью линию задержки соединен со входом -четвертого элемента ИЛИ этого же блока выход которого соединен с нулевым входом первого триггера и с нулевым входом третьего триггера этого же блока, выход четвертого элемента И блока пуска-останова соединен со входом, первого счетчика этого же бло ка, второй вход которого соединен с выходом первого элемента ИЛИ, а груп па выходов - с группой входов mecTQго элемента И этого же блока, выход которого соединен со вторыми входами первого и второго элементов И этого же блока, выход второго узла сравнения блока пуска-останова соеди нен со входом седьмого элемента И и через второй элемент НК - со входом восьмого элемента И этого же блока, выход которого соединен со вторым входом второго элемента ИЛИ и с еди ничным входом второго триггера этого же блока, выход седьмого элемента И блока пуска-останова соединен через четвертую линию задержки, со входом шестого элеме 1та ИЛИ этого же вихол которого сойдинси с псрвым входом счетчика точек решения,группа выходов комбинационного сумматора блока пуска-останова соединена с первой группой входов третьего узла сравнения этого же блока,вторая группа входов которого соединена с группой выходов второго счетчика этого же блока,а выход - через пятую линию задержки соединен со вторыми входами седьмого и восьмогб элементов И этого же блока и со входом седьмого элемента ИЛИ этого же блока, выход которого соединен с первым входом второго счетчика и с нулевым входом четвертого триггера этого же блока, единичный вход которого соединен с выходом второй линии задержки этого же блока, а единичный выход - со входом девятого элемента И этого же блока, второй вход которого соединен с выходом делителя частоты этого же блока, а выход - со вторьм входом второго счетчика этого же блока, первый вход счетчика итераций соединен с выходом третьего элемента ИЛИ блока пуска-останова, второй вход - с единичным выходом третьего триггера блока пуска-останова, а третий вход- с первым выходом распределителя импульсов блока формирования управляющих импульсов и потенциалов, первый вход которого соединен с единичным выходом первого триггера блока пус.ка-останова, второй выход распределителя импульсов блока формирования управляющих импульсов и потенциалов соединен со вторым входом третьего элемента И блока пуска-останова, третий выход - со вторым входом пятого элемента И блока пуска-останова, а группа выходов - с группой входов узла триггеров блока формирования управляющих импульсов и потенциалов, первый выход которого соединен со входом элемента И блока формирования управляющих импульсов и потенциалов, второй вход которого соединен с нулевым выходом второго триггера блока пуска-останова, а выход - со входом элемента ИЛИ, второй вход которого соединен также с выходом четвертого элемента И блока пуска-останова, выход генератора тактовых импульсов блока формирования управляющих импульсов и потенциалов соединен со вторым входом распределителя импульсов и третьим входом элемента И этого же блока, с третьим входом четвертого элемента И и входом делителя частоты блока пуска-останова,первый выход пульта управления соединен с третьим входом второго элемента ИЛИ блока пуска-останова, второй выход со вторым входом пятого элемента ИЛИ блока пуска-останова, а третий выход - со входами третьего, четвертого, шестого и седьмого элементов ИЛИ блока пуска-останова и третьим входом

распределителя импульсов блока формирования импульсов и потенциалов, второй вход счетчика точек решения соединен также с выходом третьего узла сравнения, первый выход блока управления соединен с первьи и третьим выходами пульта управления, с единичным выходом третьего триггера блока пуска-останова, с четвертым выходом распределителя импульсов, со вторым выходом узла триггера и с вьоходом генератора тактовых -импульсов блока формирования управляющих импульсов и потенциалов, второй выход блока управления соединен с третьим выходом пульта управления, с выходом первого узла сравнения и выходом девятого элемента И блока пуска-останова, с пятым выходом распределителя импульсов и с выходом

генератора тактовых импульсов блока формирования управляющих импульсов и потенциалов, третий выход блока управления соединен с третьим выходом пульта управления и с выходом элег ента ИЛИ блока формирования управляющих импульсов и потенциалов, а входная шина блока управления соединена с группой входов комбинационного сумматора.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР Н 481916, кл, G 06 J 1/02, 1975.

2,Авторское свидетельство СССР № 488205,. кл. G 06 J 1/02, 1975,

3,Авторское свидетельство СССР

532112,кл. G 06 J 1/02, 1976 (прототип) .

Авторы

Даты

1982-01-23—Публикация

1980-04-07—Подача