1

Изобретение относится к вычислительной технике и предназначено для решения широкого класса задач, описываемых системами дифференциальных и алгебраических уравнений и уравнениями, сводящимися к дифференциальным, а также для моделирования сложных процессов и объектов.

Известна цифровая интегрирующая структура, содержащая решающие блоки, блок коммутации, блоки ввода и вывода, блок управления и предназначенная для решения широкого класса задач, описываемых системами-дифференциальных и алгебраических уравнений и уравнениями, сводящимися к дифференциальным { .

Недостатком известной цифровой интегрирующей структуры (ЦИС) является малая вычислительная мощность, увеличению которой препятствуют боль шие затраты оборудования, возникающие при этом и не позволяющие практически создать ЦИС большой мощности.

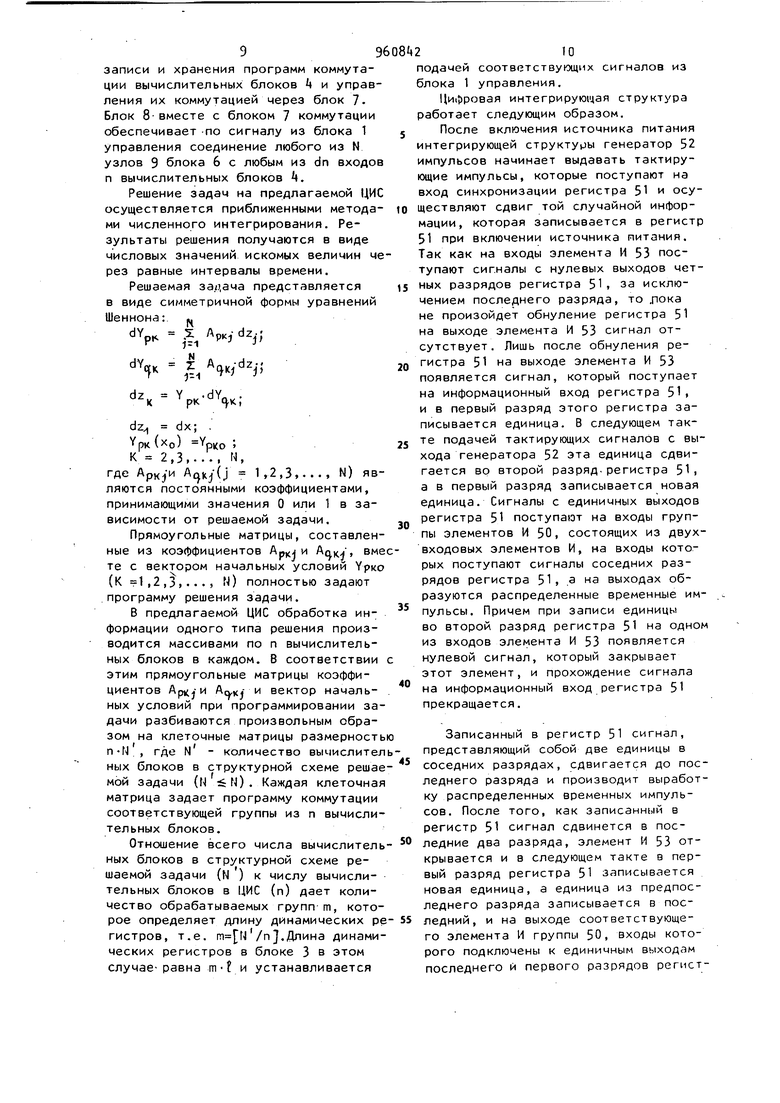

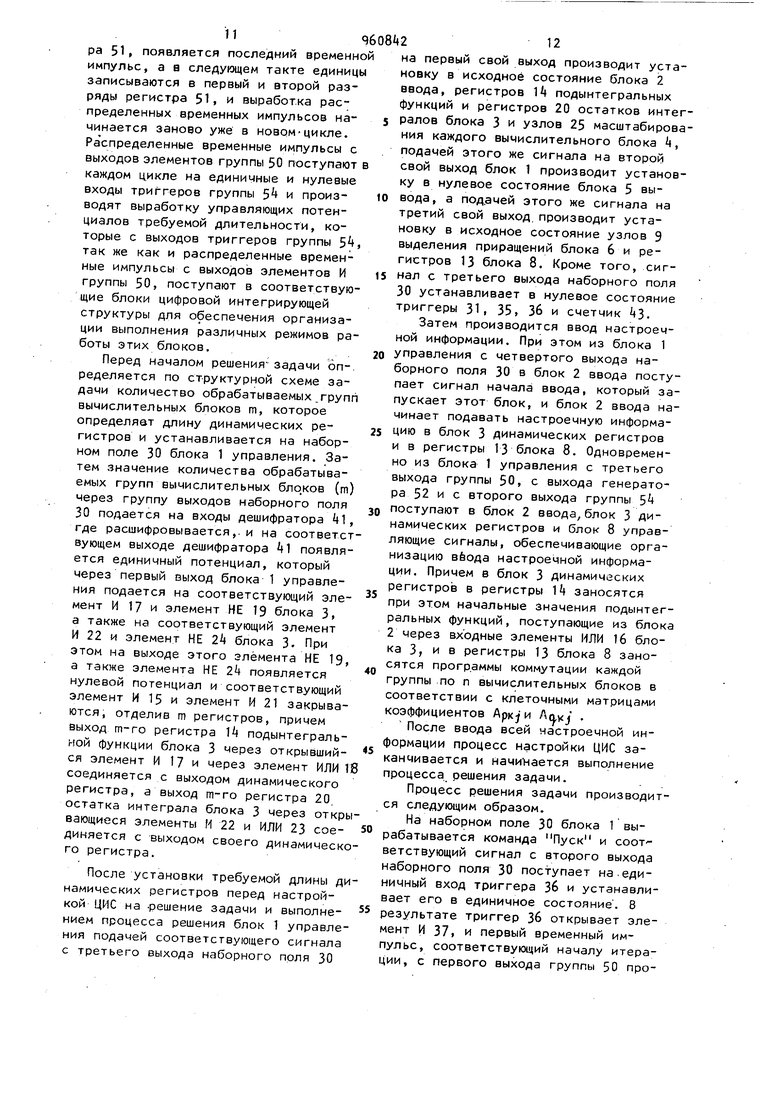

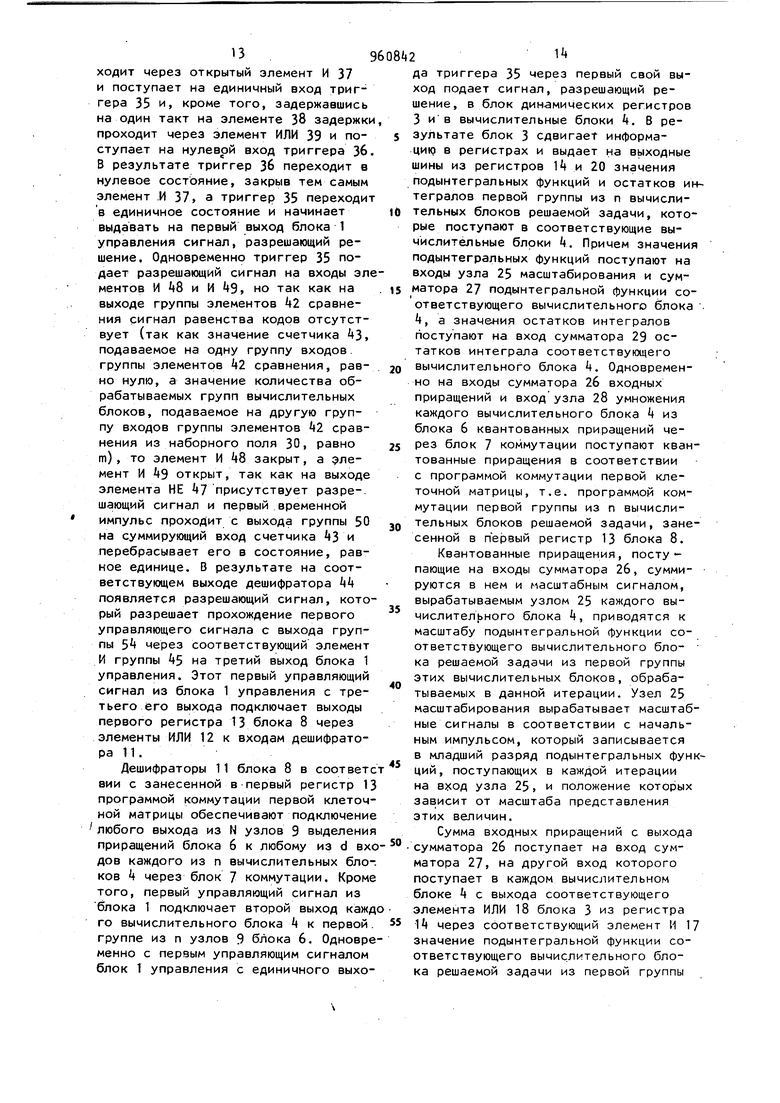

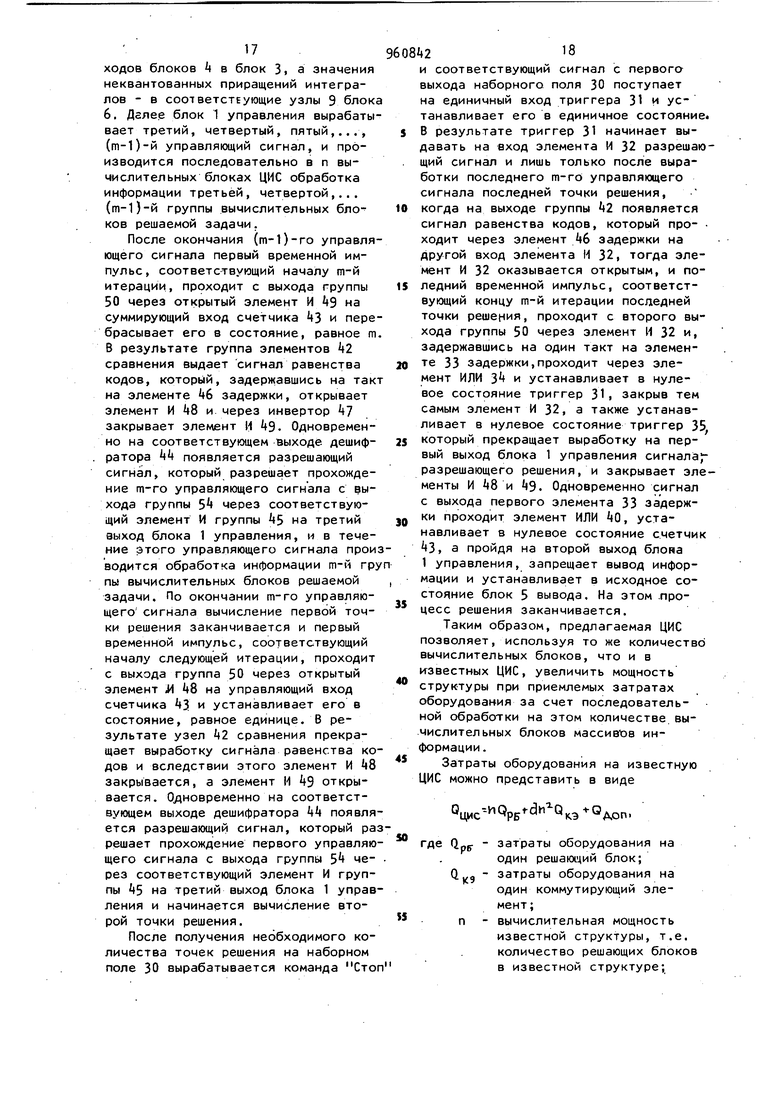

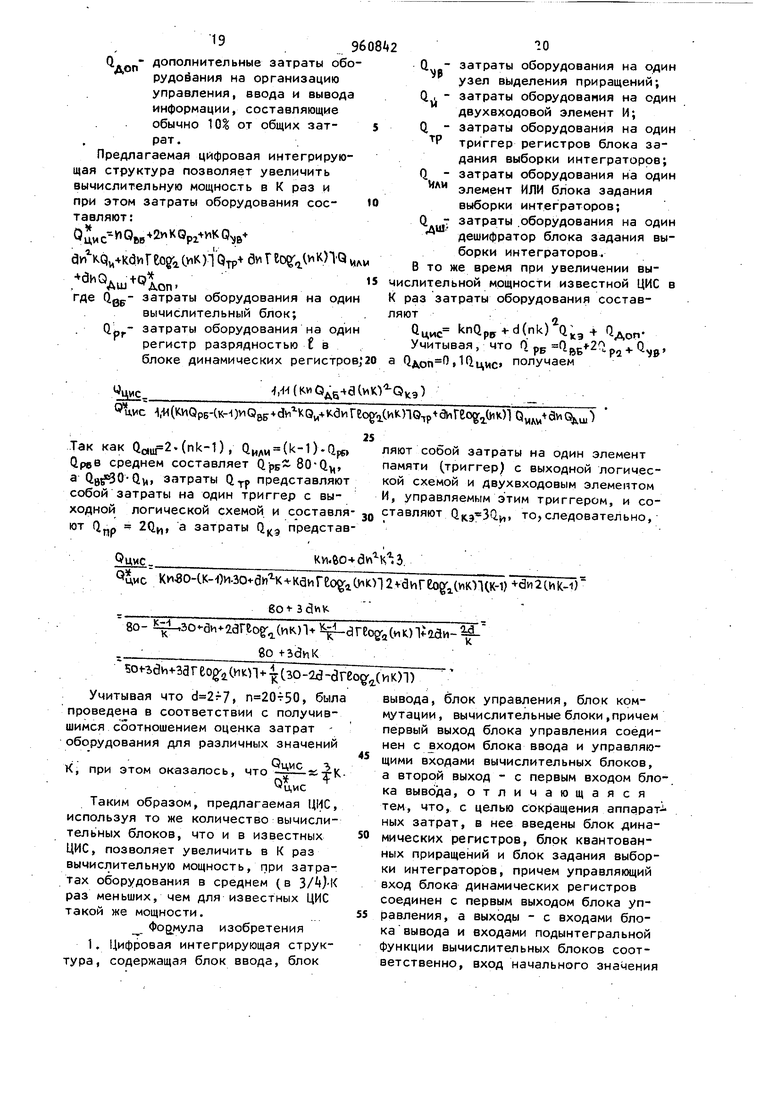

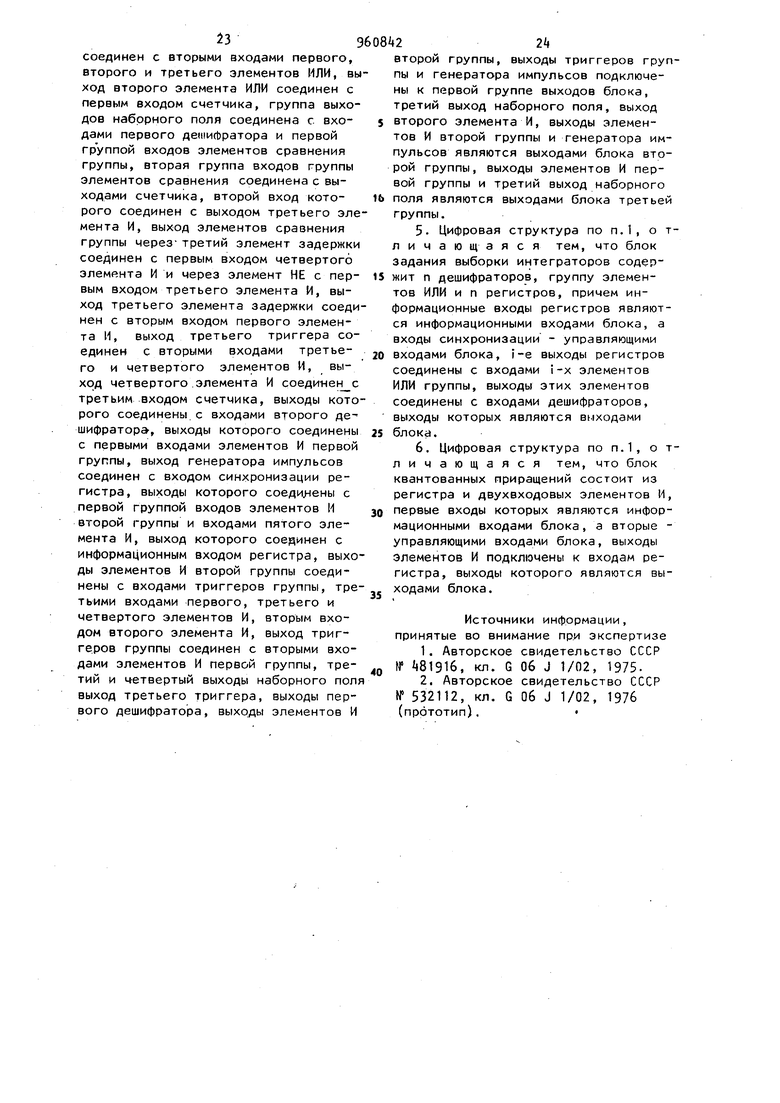

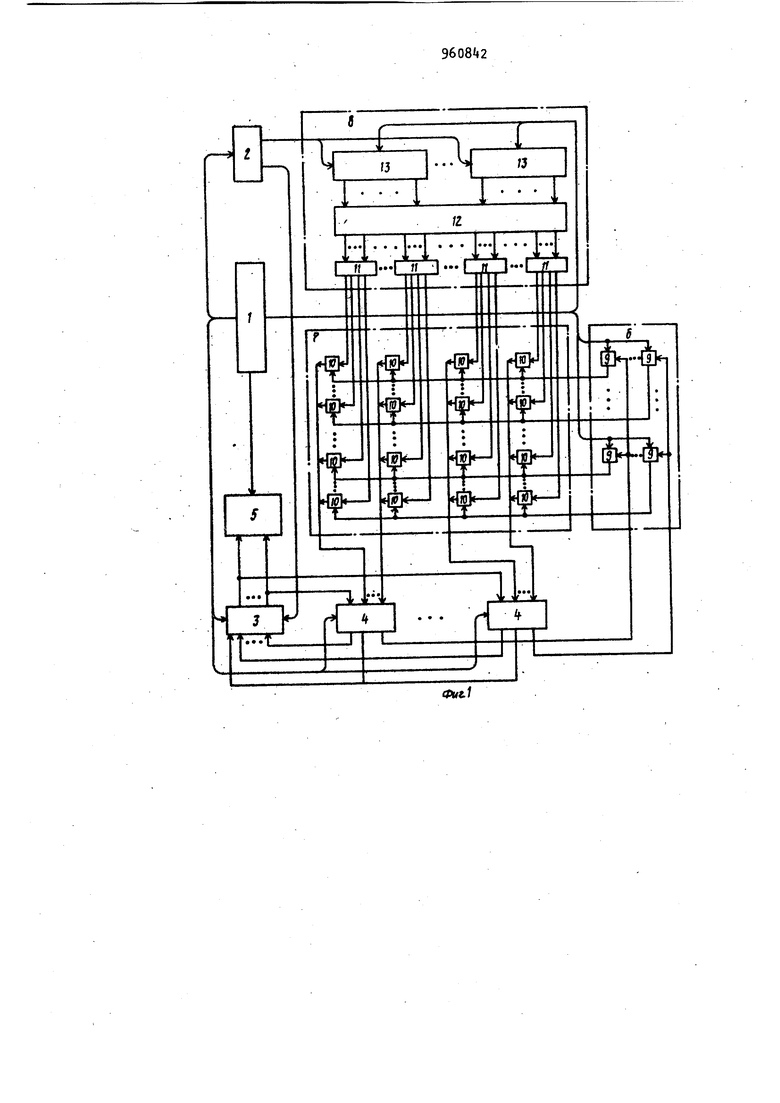

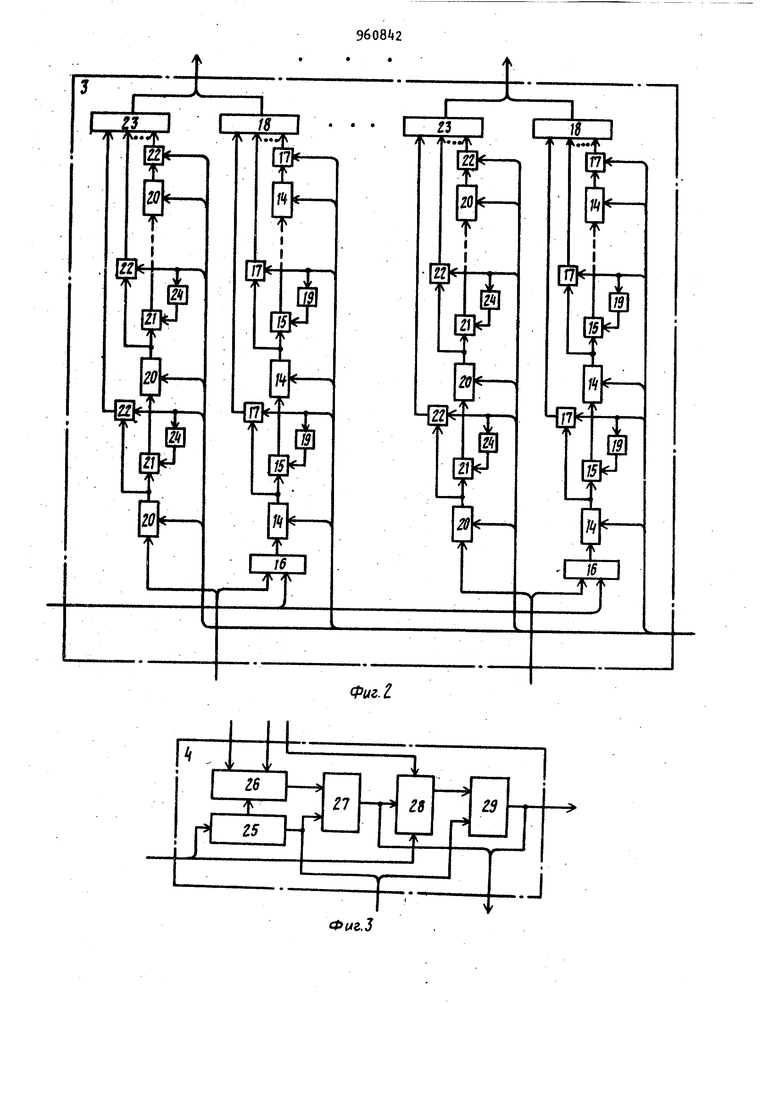

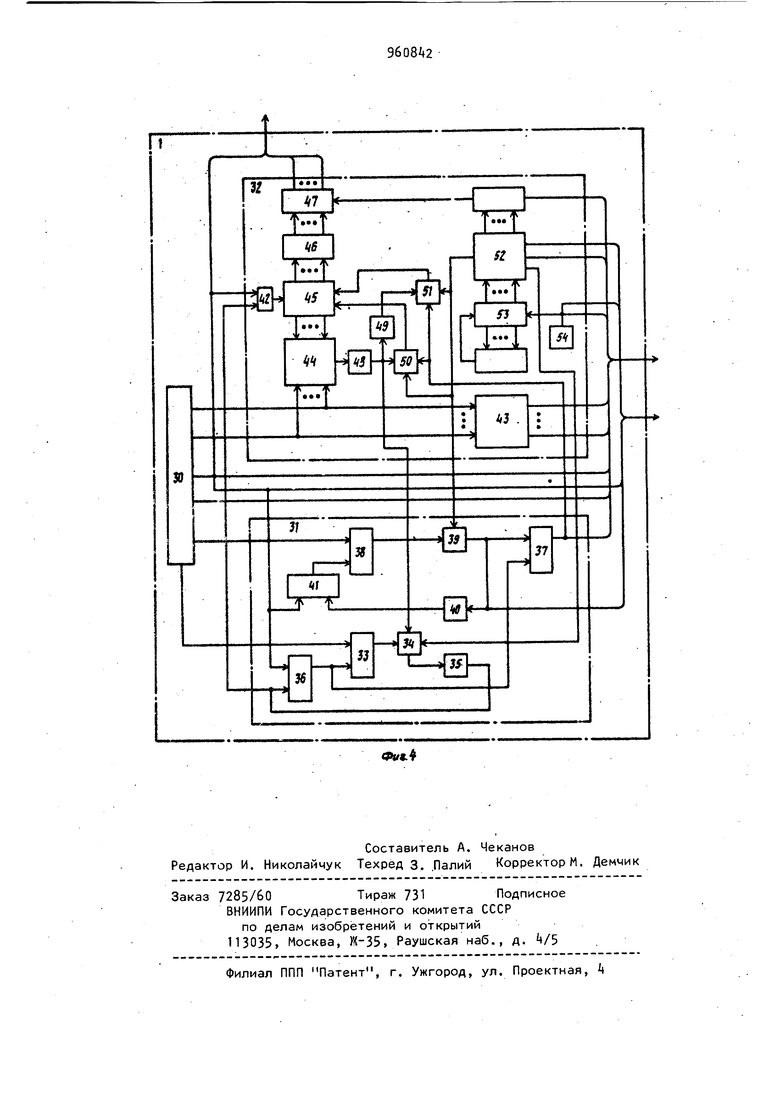

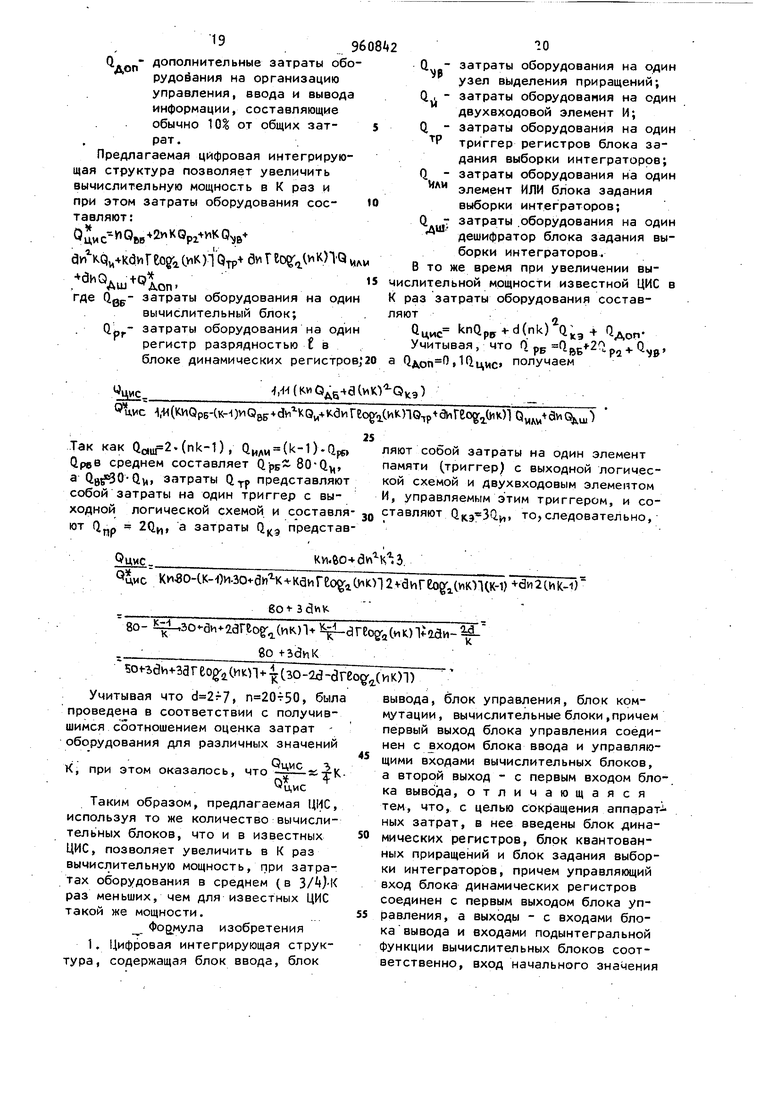

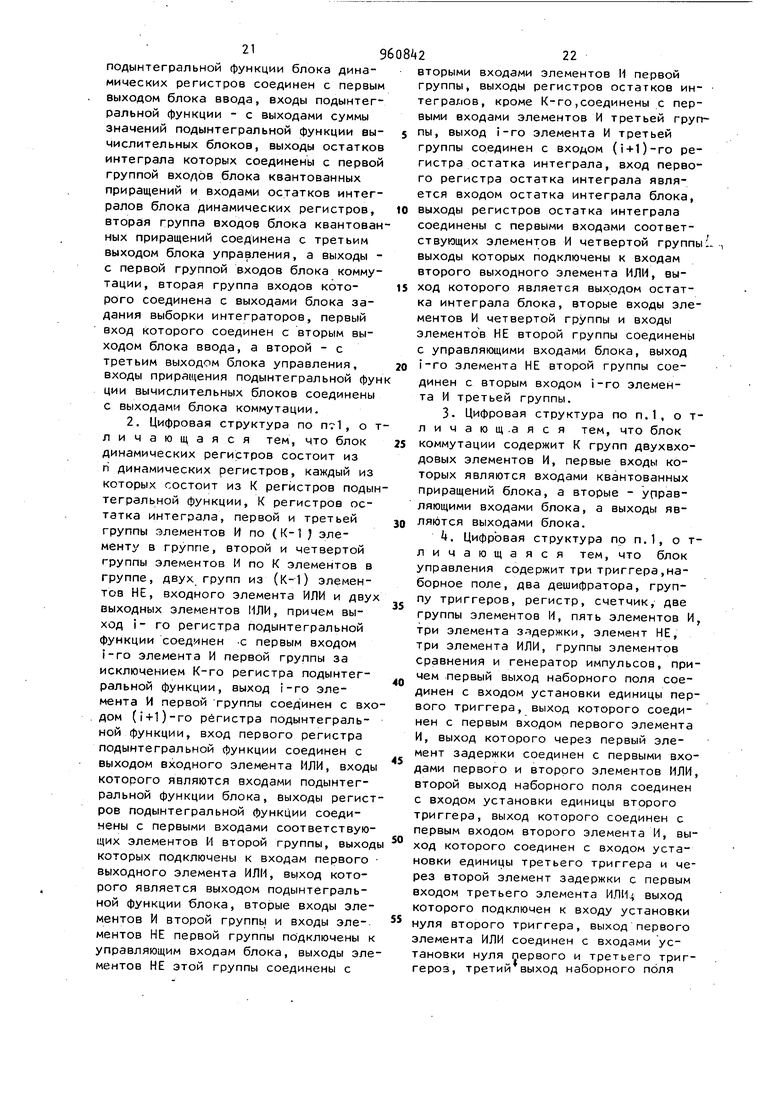

Наиболее близким техническим решением к изобретению является ЦИС, содержащая решающие блоки, блоки ввода и вывода, блоки управления, набора и коммутации, причем выход блока набора соединен с группой входов каждого решающего блока, а вход с-первым выходом каждого решающего блока, первый выход блока ввода соединен с первым входом каждого решающего блока, первый выход блока управления - с входом блока ввода и вторым входом каждого решающего блока, а вход блока управления - с ,5 вторым выходом каждого решающего блока и с первым входом блока вывода, второй вход которого соединен с вторым выходом блока управления, первая группа входов блока коммутации соединена с вторым выходом блока ввода, а каждый вход второй группы входов блока коммутации соединен также с первым выходом соответствующего решающего блока, первая группа 9ХОДОВ каждого решающего блока соединена с соответствующей группой выходов блока коммутации f2j, Недостатком известной ЦИС является малая вычислительная мощность, не позволяющая моделировать сложные про .цессы и объекты. Увеличению вычислительной мощности известной структуры препятствуют возникающие большие затраты оборудования на коммутацию решающих блоков. Вычислительная мощность ее может составлять лишь 20-50 решающих блоков. Целью изобретения является сокращение аппаратных затрат ЦИС. Поставленная цель достигается тем что в цифровую интегрирующую структуру, содержащую блок ввода, блок вы вода, блок управления, блок коммутации, вычислительные блоки, причем первый выход блока управления соединен с входом блока ввода и управляющими выходами вычислительных блоков, а второй выход - с первым входом бло ка вывода, дополнительно введены бло динамических регистров, блок квантованных приращений и блок задания выборки интеграторов, причем управляющий вход блока динамических регистров соединен с первым выходом блока управления, а выходы - с входами блока вывода и входами подынтегральной функции вычислительных блоков соответственно,вход начального значен подынтегральной функции блока динамиче ких регистров соединен с первым выходом блока ввода, входы подынтегральной функции - с выходами суммы значений подынтегральной функции вычислительных блоков, выходы остатков интеграла которых соединены с первой груп пой входов блока квантованных прит ращений и .входами остатков интегралов блока динамических регистров, вторая группа входов блока квантованных приращений соединена с третьи выходом блока управления, а выходы с первой группой входов блока ком.мутации, вторая группа входов которого соединена с выходами блока зада ния выборки интеграторов, первый вход которого соединен с вторым выходом блока ввода, а второй - с третьим выходом блока управления, входы приращения подынтегральной функции вычислительных блоков соединены с выходами блока коммутации. Кроме того, блок динамических регистров содержит п динамических регистров, каждый из которых состоит из К регистров подынтегральной функции, К регистров остатка интеграла, первой и третьей группы элементов И элементу в группе, второй и четвертой группы элементов И по К элементов в группе, двух групп из (K-l) элементов НЕ, входного элемента ИЛИ и двух выходных элементов ИЛИ, причем выход i-ro регистра подынтегральной функции соединен с первым входом i-ro элемента И первой группы за исключением К-го регистра подынтегральной функции, выход i-ro элемента И первой группы соединен с входом (i+l)-ro регистра-подынтегральной функции, вход первого регистра подынтегральной функции соединен с выходом входного элемента ИЛИ, входы которого являются входами подынтег-ральной функции блока, выходы регистров подынтегральной функции соединены с первыми входами соответствующих элементов И второй группы, выходы которых подключены к входам первого выходного элемента ИЛИ, выход которого является выходом подынтегральной функции блока, вторые входы элементов И второй группы и входы элементов- НЕ первой группы подключены к управляющим входам блока, аыходы. элементов НЕ этой группы соединены с вторыми входами элементов И первой группы, выходы регистров остатков интегралов, кроме К-го, соединены с первыми входами элементов И третьей группы, выход i-ro элемента И третьей группы соединен с входом (i+l)-ro регистра остатка интеграла,вход первого регистра остатка интеграла является входом остатка интеграла блока, выходы регистров остатка интеграла соединены с первыми входами соответствующих элементов И четвертой группы, выходы которых подключены к входам второго выходного элемента. ИЛИ, выход которого является выходом остатка интеграла блока, вторые входы элементов И четвертой группы и входы элементов НЕ второй Группы соединены с управляющими входами блока, выход i-ro элемента НЕ второй группы соединен с вторым входом i-ro элемента И третьей группы. При этом блок коммутации содержит К-групп двухвходовых элементов И, первые входы которого являются входами квантованных приращений блока, а вторые - управляющими, входами блока, а выходы являются выходами блока. Кроме того, блок управления содержит три триггера, наборное поле, два дешифратора, группу триггеров, регистр, счетчик, две группы элементов И, пять элементов И, три элемента задержки, элемент НЕ, три элемента ИЛИ, группу элементов сравнения и генератор импульсов, причем первый выход наборного поля соединен с входом установки единицы первого триггера, выход которого соединен с первым входом первого элемента И, вы ход которого через первый элемент за держки соединен с первыми входами первого и второго элементов ИЛИ, вто рой выход наборного поля соединен с входом установки единицы второго три гера, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом установки единицы третьего триггера и че рез второй элемент задержки с первым входом третьего элемента ИЛИ, вы ход которого подключен к входу установки нуля второго триггера, выход первого элемента ИЛИ соединен с входами установки нуля первого и третье го триггеров, третий выход наборного поля соединен с вторыми входами , второго и элементов ИЛИ, выход второго элемента ИЛИ соединен с первым входом счетчика, груп па выходов наборного поля соединена входами первого дешифратора и первой группой входов элементов сравнения группы, вторая группа входов группы элементов сравнения соединена с выходами счетчика, второй вход которого соединен с выходом третьего элемента И, выход элементов сравнения группы через третий элемент задержки соединен с первым входом четвертого элемента И и через элемент НЕ с первым входом третьего элемента И, выход третьего элемента задержки соединен с вторым входом первого элемента И, вь1ход третьего триггера сое динен с вторыми входами третьего и четвертого элементов И, выход четвертого элемента И соединен с третьим входом счетчика, выходы которого сое динены с входами второго дешифратора выходы которого соединены с первыми входами элементов И первой группы, выход генератора импульсов соединен с входом синхс-онизации регистра, выходы которого соединены с первой гру ПОЙ входов элементов И второй группы и входами пятого элемента И, выход которого соединен с информационным входом регистра, выходы элементов И второй группы,соединены с входами триггеров группы, третьими входами первого, третьего и четвертого элементов И, вторым входом второго элемента И, выход триггеров группы соединен с вторыми входами элементов И первой группы, третий и четвертый выходы наборного поля, выход третьего триггера, выходы первого дешифратора, выходы элементов И второй групг пы, выходы триггеров группы и генератора импульсов подключены к„первой группе выходов блока, третий выход наборного поля, выход второго элемента И, выходы элементов И второй группы и генератора импульсов являются выходами блока второй группы, выходы элементов И первой группы и третий выход наборного поля являются выходами блока третьей группы. Блок задания выборки интеграторов содержит п дешифраторов, группу элементов ИЛИ и п регистров, причем информационные входы регистров являются информационными входами блока, а входы синхронизации - управляющими входами блока, i-e выходы регистров соединены с входами i -х элементов ИЛИ группы, выходы этих элементов сое динены с входами дешифраторов, выходы которых являются выходами блока. Блок квантованных приращений состоит из регистра и двухвходовых элементов И, первые входы которых являются информационными входами блока, а вторые - управляющими входами блока, выходы элементов И подключены к входам регистра, выходы которого являются выходами блока. На фиг. 1 представлена блок-схема ЦИС; на фиг. 2 - схема реализации блока динамических регистров; на фиг. 3 - то же, вычислительного блока; на фиг. - то же, блока управления. В состав ЦИС СФИГ.1) входят блоки 1-3 управления, ввода и динамических регистров соответственно ,вычислительные блоки 4, блоки вывода, квантованных приращений, коммутации и задания выборки интеграторов, причем блок 6 квантованных приращений включает узлы 9 выделения приращений, блок 7 коммутации включает К групп двухвходовых элементов И 10, а блок 8 задания выборки интеграторов - п дешифраторов 11, группу элементов ИЛИ и п регистров 13. В состав блока 3 динамических регистров ( фиг.2 входят п динамически регистров, каждый из которых состоит из К регистров Tt подынтегральной функции, первой группы элементов И 1 входного элемента ИЛИ 16, второй гру пы элементов И 17,. первого выходного элемента ИЛИ 18, первой группы элементов НЕ 19, К регистров 20 остатка интеграла, третьей группы элементов И 21, четвертой группы элементов И 22, второго выходного элемента ИЛИ 23, второй группы элементов НЕ 2-. В состав каждого вычислительного блока 4 ЦИС ( фиг.З.) входят узел 25 масштабирования, сумматор 2б входных приращений, сумматор 27 подынтеграль ной функции, узел 28 умножения, сумматор 29 остатка интеграла. Блок 1 управления (фиг.4 ) включае наборное пол.е 30, первый триггер 31, первый элемент И 32, первый элемент 33 задержки, первый элемент ИЛИ 34, третий 35 и второй 36 триггеры,второй элемент И 37, второй элемент 38 задержки, третий 39 и второй 40 элементы ИЛИ, первый дешифратор 41, гру пу элементов 42 сравнения, счетчик 4 второй дешифратор 44, первую группу элементов И 45, третий элемент 46 задержки, элемент НЕ 47, четвертый 48 и третий 49 элементы И, вторую группу элементов И 50, регистр 5Г, генератор 52 импульсов, пя тый элемент И 53, группу триггеров 54. Блок -1 управления предназначен дл выработки управляющих сигналов, необ ходимых для работы устройства, блок 2 ввода - для ввода настроечной информации (начальных значений подынте .ральных функций и программ коммутации) в регистры 14 блока 3 динамических регистров и в регистры 13 бло ка 8 задания выборки интеграторов. Вычислительные блоки 4 - это устройства интегрирования, выполняющие численное интегрирование по Стилтьесу. Их количество (п), а также способ обработки информации в них выбираются в зависимости от требуемой вычислительной мощности ЦИС N и ее быстродействия. Блок 3 динами ческих регистров предназначен для хранения.и передачи значений подынтегральной функции и остатка интеграла и состоит из регистров подынтегральной функции разрядностью, равной t, и N регистров остатка интеграла разрядностью f, которые объединены в 2п динамических регистра по К последовательно соединенных регистров подынтегральной функции или регистров остатка интеграла в каждом. Длина динамических регистров может изменяться от до К-1 кра.тно сигналом из блока 1 управления и определяется при программировании задачи. Блок 5 вывода, предназначен для вывода результатов решения. Блок 6 -квантованных приращений состоит из N узлов выделения приращений, предназначенных для выделения и хранения квантованных приращений, причем выделение квантованных приращений, т.е. квантование приращений, представляет собой операцию выделения определенной группы разрядоз, алгоритм которой имеет вид (vz) где V Z - квантованное приращение; V Z неквантованное приращение;функция расчленения, выделяющая два знаковых разряда и разрядов после запятой. Неквантованные приращения поступают в блок 6 из вычислительных блоков 4, причем подключение соответствующей группы из п узлов выделения приращений к выходам п вычислительных блоков 4 происходит на каждой итерации автоматически подачей соответвующих сигналов из блока 1 -управления. Блок 7 коммутации состоит из dnN двухвходовых (d - количество входов вычислительного блока 4) элементов И 10 и предназначен для передачи приращений из соответствующих узлов 9 выделения приращений блока 6 на соответствующие входы вычислительных блоков 4 в соответствии с программой коммутации, хранимой в блоке 8. Блок 8 задания выборки интеграторов представляет собой К регистров 13 разрядностью dn-IloggN (где наименьшее целое число, большее X), dn дешифраторов 11 и dnflogJ lj элементов ИЛИ с К входами в группе элементов ИЛИ 12 и предназначен для записи и хранения программ коммутации вычислительных блоков k и управления их коммутацией через блок 7Блок 8-вместе с блоком 7 коммутации обеспечивает -по сигналу из блока 1 управления соединение любого из N узлов 9 блока 6 с любым из dn входо п вычислительных блоков Д. Решение задач на предлагаемой ЦИ осуществляется приближенными метода ми численного интегрирования. Результаты решения получаются в виде числовых значений искомых величин ч рез равные интервалы времени. Решаемая задача представляется в виде симметричной формы уравнений Шеннона Лрк,- dZj1 1г- I, K %K-dV; dz dx; . YpK(XD) ; К 2,3 N, где Арк.,и 1,2,3,..., N) яв ляются постоянными коэффициентами, принимающими значения О или 1 в зависимости от решаемой задачи. Прямоугольные матрицы, составлен ные из коэффициентов АлцУ, вм те с вектором начальных условий Урко (к 1,2,3,..., N) полностью задают программу решения задачи. В предлагаемой ЦИС обработка информации одного типа решения производится массивами по п вычислительных блоков в каждом. В соответствии этим прямоугольные матрицы коэффициентов Ар,(и А и вектор начальных условии при программировании за дачи разбиваются произвольным образом на клеточные матрицы размерност n-N , где N - количество вычислител ных блоков в структурной схеме решае мой задачи (N :N). Каждая клеточная матрица задает программу коммутации соответствующей группы из п вычислительных блоков. Отношение всего числа вычислитель ных блоков в структурной схеме решаемой задачи (N) к числу вычислительных блоков в ЦИС (п) дает количество обрабатываемых групп т, которое определяет длину динамических р гистров, т.е. ,Длина динами ческих регистров в блоке 3 в этом случае- равна т- и устанавливается подачей соответствующих сигналов из блока 1 управления. Цифровая интегрирующая структура работает следующим образом. После включения источника питания интегрирующей структуры генератор 52 импульсов начинает выдавать тактирующие импульсы, которые поступают на вход синхронизации регистра 51 и осуществляют сдвиг той случайной информации, которая записывается в регистр 51 при включении источника питания. Так как на входы элемента И 53 поступают сигналы с нулевых выходов четных разрядов регистра 51, за исключением последнего разряда, то лока не произойдет обнуление регистра 51 на выходе элемента И 53 сигнал отсутствует. Лишь после обнуления регистра 51 на выходе элемента И 53 появляется сигнал, который поступает на информационный вход регистра 51, и в первый разряд этого регистра записывается единица. В следующем такте подачей тактирующих сигналов с выхода генератора 52 эта единица сдвигается во второй разряд.регистра 51 а в первый разряд записывается новая единица. Сигналы с единичных выходов регистра 51 поступают на входы группы элементов И 50, состоящих из двухвходовых элементов И, на входы которых поступают сигналы соседних разрядов регистра 51, а на выходах образуются распределенные временные импульсы. Причем при записи единицы во второй разряд регистра 51 на одном из входов элемента И 53 появляется нулевой сигнал, который закрывает этот элемент, и прохождение сигнала на информационный вход регистра 51 прекращается. Записанный в регистр 51 сигнал, представляющий собой две единицы в соседних разрядах, сдвигается до последнего разряда и производит выработку распределенных временных импульсов. После того, как записанный в регистр 51 сигнал сдвинется в последние два разряда, элемент И 53 открывается и в следующем такте в первый разряд регистра 51 записывается новая единица, а единица из предпоследнего разряда записывается в последний, и на выходе соответствующего элемента И группы 50, входы которого подключены к единичным выходам последнего и первого разрядов регистpa 51, появляется последний временно импульс, а в следующем такте единицы записываются в первый и второй разряды регистра 51, и выработка распределенных временных импульсов начинается заново уже в новом-цикле. Распределенные временные импульсы с выходов элементов группы 50 поступают в каждом ц.икле на единичные и нулевые входы триггеров группы 5 и производят выработку управляющих потенциалов требуемой длительности, которые с выходов триггеров группы 5f, так же как и распределенные временные импульсы с выходов элементов И группы 50, поступают в соответствующие блоки цифровой интегрирующей структуры для обеспечения организации выполнения различных режимов работы этих блоков. Перед началом решения задачи 6п-. ределяется по структурной схеме задачи количество обрабатываемых групп вычислительных блоков т, которое определяет длину динамических регистров и устанавливается на наборном поле 30 блока 1 управления. Затем значение количества обрабатываемых групп вычислительных бло.ков (т) через группу выходов наборного поля 30 подается на входы дешифратора 41, где расшифровывается,. и на соответст вующем выходе дешифратора 1 появляется единичный потенциал, который через первый выход блока 1 управления подается на соответствующий элемент И 17 и элемент НЕ 19 блока 3, а также на соответствующий элемент И 22 и элемент НЕ 24 блока 3. При этом на выходе этого элемента НЕ 19, а также элемента НЕ 2k появляется нулевой потенциал и соответствующий элемент И 15 и элемент И 21 закрываются, отделив m регистров, причем выход т-го регистра 14 подынтегральной функции блока 3 через открывшийся элемент И 17 и через элемент ИЛИ 1 соединяется с выходом динамического регистра, а выход т-го регистра 20. остатка интеграла блока 3 через откр вающиеся элементы Н 22 и ИЛИ 23 соединяется с выходом своего динамическ го регистра. После установки требуемой длины д намических регистров перед настройкой ЦИС на .решение задачи и выполнением процесса решения блок 1 управле ния подачей соответствующего сигнала с третьего выхода наборного поля 30 на первый свои выход производит установку в исходное состояние блока 2 ввода, регистров 14 подынтегральных функций и регистров 20 остатков интегралов блока 3 и узлов 25 масштабирования каждого вычислительного блока 4, подачей этого же сигнала на второй свой выход блок 1 производит установку в нулевое состояние блока 5 вывода, а под.ачей этого же сигнала на третий свой выход, производит установку в исходное состояние узлов 9 выделения приращений блока 6 и регистров 13 блока 8. Кроме того, си|- нал с третьего выхода наборного поля 30 устанавливает в нулевое состояние триггеры 31, 35, Зб и счетчик 43. Затем производится ввод настроечной информации. При этом из блока 1 управления с четвертого выхода наборного поля 30 в блок 2 ввода поступает сигнал начала ввода, который запускает этот блок, и блок 2 ввода начинает подавать настроечную информацию в блок 3 динамических регистров и в регистры 13 блока 8. Одновременно из блока 1 управления с третьего выхода группы 50, с выхода генератора 52 и с второго выхода группы 54 поступают в блок 2 ввода, блок 3 динамических регистров и блок 8 управляющие сигналы, обеспечивающие организацию вбода настроечной информации. Причем в блок 3 динамических регистров в регистры 14 заносятся при этом начальные значения подынте(- ральных функций, поступающие из блока 2 через входные элементы ИЛИ 16 блока 3, и в регистры 13 блока 8 заносятся программы коммутации каждой группы по п вычислительных блоков в соответствии с клеточными матрицами коэффициентов . После ввода всей настроечной информации процесс настройки ЦИС заканчивается и начинается выполнение процесса решения задачи. Процесс решения задачи производится следующим образом. На наборном поле 30 блока 1 вырабатывается команда Пуск и соответствующии сигнал с второго выхода наборного поля 30 поступает на.единичный вход триггера Зб и устанавливает его в единичное состояние . 8 результате триггер 36 открывает элемент И 37, и первый временный импульс, соответствующий началу итераЦии, с первого выхода группы 50 проходит через открытый элемент И 37 и поступает на единичный вход триггера 35 и, кроме того, задержавшись на один такт на элементе 38 задержки проходит через элемент ИЛИ 39 и поступает на нулевой вход триггера 36 В результате триггер 36 переходит в нулевое состояние, закрыв тем самым элемент .И 37, а триггер 35 переходит в единичное состояние и начинает выдавать на первый выход блока 1 управления сигнал, разрешающий решение. Одновременно триггер 35 подает разрешающий сигнал на входы эл ментов И iS и И Э, но так как на выходе группы элементов 2 сравнения сигнал равенства кодов отсутствует (так как значение счетчика 43, подаваемое на одну группу входов. группы элементов k2 сравнения, равно нулю, а значение количества обрабатываемых групп вычислительных блоков, подаваемое на другую группу входов группы элементов Ц2 сравнения из наборного поля 30, равно т), то элемент И 48 закрыт, а элемент И 9 открыт, так как на выходе элемента НЕ 7 присутствует разре-. шающий сигнал и первый временной импульс проходит с выхода группы 50 на суммирующий вход счетчика 3 и перебрасывает его в состояние, равное единице. В результате на соответствующем выходе дешифратора k появляется разрешающий сигнал, кото рый разрешает прохождение первого управляющего сигнала с выхода группы 5 через соответству ющий элемент И группы 45 на третий выход блока 1 управления. Этот первый управляющий сигнал из блока 1 управления с третьего его выхода подключает выходы первого регистра 13 блока 8 через элементы ИЛИ 12 к входам дешифратора 1 1 . Дешифраторы 11 блока 8 в соответ ВИИ с занесенной в первый регистр 13 программой коммутации первой клеточной матрицы обеспечивают подключение любого выхода из N узлов 9 выделения приращений блока 6 к любому из d дов каждого из п вычислительных бло-. ков 4 через блок 7 коммутации. Кроме того, первый управляющий сигнал из блока 1 подключает второй выход каждо го вычислительного блока 4 к первой, группе из п узлов 9 б.пока 6. Одновременно с первым управляющим сигналом блок 1 управления с единичного выхо9вхо l а триггера 35 через первый свой выход подает сигнал, разрешающий реение, в блок динамических регистров 3 ив вычислительные блоки 4, В результате блок 3 сдвигает информации в регистрах и выдает на выходные ины из регистров 14 и 20 значения подынтегральных функций и остатков интегралов первой группы из п вычислительных блоков решаемой задачи, которые поступают в соответствующие вычислительные блоки 4. Причем значения подынтегральных функций поступают на входы узла 25 масштабирования и сумматора 27 подынтегральной функции соответствующего вычислительного блока . 4, а значения остатков интегралов поступают на вход сумматора 29 остатков интеграла соответствующего вычислительного блока 4. Одновременно на входы сумматора 2б входных приращений и вход узла 28 умножения каждого вычислительного блока 4 из блока 6 квантованных приращений через блок 7 коммутации поступают квантованные приращения в соответствии с программой коммутации первой клеточной матрицы, т.е. программой коммутации первой группы из п вычислительных блоков решаемой задачи, занесенной в первый регистр 13 блока 8. Квантованные приращения, поступающие на входы сумматора 26, суммируются в нем и масштабным сигналом, вырабатываемым узлом 25 каждого вычислительного блока 4, приводятся к масштабу подынтегральной функции соответствующего вычислительного бло- ка решаемой задачи из первой группы этих вычислительных блоков, обрабатываемых в данной итерации. Узел 25 масштабирования вырабатывает масштабные сигналы в соответствии с начальным импульсом, который записывается в младший разряд подынтегральных функций, поступающих в каждой итерации на вход узла 25, и положение которых зависит от масштаба представления этих величин. Сумма входных приращений с выхода сумматора 26 поступает на вход сумматора 27, на другой вход которого поступает в каждом вычислительном блоке 4 с выхода соответствующего элемента ИЛИ 18 блока 3 из регистра 14 через соответствующий элемент И 17 значение подынтегральной функции соответствующего вычислительного блока решаемой задачи из первой группы этих вычислительных блоков, обрабатываемой в этой итерации, В результате выполнения операции суммирования получаются новые значения подынтегральных функций, которые поступа.ют в каждом вычислительном блоке i с йыхода сумматора 27 на вход узла 28 умножения и на соответствующий вход блока 3 динамических регистров, и при этом каждое новое значение подынтегральных функций записывается через соответствующий элемент ИЛИ 16 в соответствующий обрабатываемому вычислительному блоку решаемой задачи освободившийся регистр Н подын тегральной функции из m последовательно соединенных регистров 1Л блока 3, подключенных к соответствующему вычислительному блоку k и количество которых (т) определено при подготовке к решению данной задачи. На второй вход узла 28 умножения каждого вычислительного блока k поступают из блока 6 через блок 7 коммутации приращения переменной интегрирования в соответствии с программой коммутации первой группы из. п вычислительных блоков решаемой задачи, а на третий вход поступает из блока 1 управления сигнал, разрешающий решение. Результат умножения в каждом вычислительном блоке поступает с выхода узла 28 на вход сум матора 29 остатка интеграла, на второй вход которого в каждом блоке поступает с выхода соответствующего элемента ИЛИ 23 блока 3 из регистра 20 через соответствующий элемент И 22 значение остатка интеграла соответст вующего вычислительного блока решаемой задачи из первой группы этих вычислительныхблоков, обрабатываемой в данной итерации, . Полученный новый остаток интеграла Р1 неквантованное приращение интеграла в каждом вычислительном блок k с выхода сумматора 29 поступают со ответственно в соответствующий обрабатываемому вычислительному блоку, решаемой задачи освободившийся ре гистр 20 остатка интеграла из m последовательно соединенных регистров 20 блока 3, подключенных к данному вычислительному блоку 4, и в соответствующий обрабатываемому вычислительному блоку решаемой задачи узел 9 выделения приращений блока 6 (из К подсоединенных к данному вычислительному блоку ), где происходит квантование и запись квантованных приращений. В результате в вычислительных блоках k в течении первого управляющего сигнала производится обработка информации первой группы из п вычислительных блоков решаемой задачи. Одновременно исходные значения подынтегральных функций первой группы вычислительных блоков решаемой задачи с выходов блока 3 поступают в блок 5 вывода, который запускается в начале первой итерации сигналом из блока 1 управления с выхода элемента И 37, и происходит печать исходных данных. По окончании первого управляющего сигнала первый временной импульс, со ответствующий началу следующей итерации, проходит с выхода группы 50 через открытый элемент И +9 на суммирующий вход счетчика 3 и перебрасывает его в состояйие, равное двум. В результате на соответствующем выходе дешифратора kk появляется разрешающий сигнал, который разрешает прохождение второго управляющего сигнала с выхода узла 5 через соответствующий элемент И узла 5 на третий выход блока 1 управления. Этот второй управляющий сигнал из блока 1 управления с третьего его выхода подключает выходы второго регистра 13 блока 8 к дешифраторам 11, ив соответствии с второй клеточной матрицей коммутац.ии соответствующие выходы из N узлов 9 блока 6 через двухвходовые элементы И 10 блока 7 подключаются к соответствующим входам вычислительных блоков . Кроме того, второй управляющий сигнал блока 1 . подключает второй выход каждого вычислительного блока 4 к второй группе из п узлов 9 блока 6. Одновременно начальные значения подынтегральных функций и остатков интегралов второй группы из п вычислительных блоков поступают из блока 3 динамических регистров на входы вычислительных блоков Ц. В течение второго управляющего сигнала происходит обработка информации во второй группе вычислительных блоков из N вычислительных блоков всей задачи и печать исходных данных этой группы в блоке 5. Одновременно новые значения подынте - ральных функций и остатков интегралов второй группы вычислительных блоков решаемой задачи поступают с выходов блоков k в блок 3, а значения неквантованных приращений интегралов - в соответстЕующие узлы 9 блок 6, Дале.е блок 1 управления вырабаты вает третий, четвертый, пятый,..., (т-1)-й управляющий сигнал, и производится последовательно в п вычислительных блоках ЦИС обработка информации третьей, четвертой,... (т-1)-й группы вычислительных блоков решаемой задачи. После окончания (m-l)-ro управля ющего сигнала первый временной импульс, соответствующий началу т-й итерации, проходит с выхода группы 50 через открытый элемент И kS на суммирующий вход счетчика k3 и пере брасывает его в состояние, равное т В результате группа элементов 42 сравнения выдает сигнал равенства кодов, который, задержавшись на так на элементе 46 задержки, открывает элемент И 48 и через инвертор 47 закрывает элемент И 49. Одновременно на соответствующем выходе дешифратора 44 появляется разрешающий сигнал, который разрешает прохождение т-го управляющего сигнала с выхода группы 54 через соответствующий элемент И группы 45 на третий выход блока 1 управления, и в течение этого управляющего сигнала прои водится обработка информации т-й гр пы вычислительных блоков решаемой задачи. По окончании т-го управляющего сигнала вычисление первой точки решения заканчивается и первый временной импульс, соответствующий началу следующей итерации, проходит с выхода группа 50 через открытый элемент Л 48 на управляющий вход счетчика 43 и устанавливает его в состояние, равное единице. В результате узел 42 сравнения прекращает выработку сигнала равенства ко дов и вследствии этого элемент И 48 закрывается, а элемент М 49 открывается. Одновременно на соответствующем выходе дешифратора 44 появля ется разрешающий сигнал, который ра решает прохождение первого управляю щего сигнала с выхода группы 54 через соответствующий элемент И группы 45 на третий выход блока 1 управ ления и начинается вычисление второй точки решения. После получения необходимого количества точек решения на наборном поле 30 вырабатывается команда Сто 218 и соответствующий сигнал с первого выхода наборного поля 30 поступает на единичный вход триггера 31 и устанавливает его в единичное состояние. В результате триггер 31 начинает выдавать на вход элемента М 32 разрешающий сигнал и лишь только после выработки последнего т-го управляющего сигнала последней точки решения, когда на выходе группы 42 появляется сигнал равенства кодов, который про- ходит через элемент 46 задержки на другой вход элемента И 32, тогда элемент И 32 оказывается открытым, и поледний временной импульс, соответствующий концу т-й итерации посдедней точки решения, проходит с второго выхода группы 50 через элемент И 32 и, задержавшись на один такт на элементе 33 задержки,проходит через элемент ИЛИ 34 и устанавливает в нулевое состояние триггер 31 закрыв тем самым элемент И 32, а также устанавливает в нулевое состояние триггер 35 который прекращает выработку на первый выход блока 1 управления сигнала;разрешающего решения, и закрывает элементы И 48 и 49. Одновременно сигнал с выхода первого элемента 33 задержки проходит элемент ИЛИ 40, устанавливает в нулевое состояние счетчик 43, а пройдя на второй выход блона 1 управления, запрещает вывод информации и устанавливает в исходное состояние блок 5 вывода. На этом .процесс решения заканчивается. Таким образом, предлагаемая ЦИС позволяет, используя то же количество вычислительных блоков, что и в известных ЦИС, увеличить мощность структуры при приемлемых затратах оборудования за счет последовательной обработки на этом количестве, вычислительных блоков массивов информации. Затраты оборудования на известную ЦИС можно представить в виде --hQ.,..tdnQ., цис- РБ затраты оборудования на один решающий блок; затраты оборудования на один коммутирующий элемент ; вычислительная мощность известной структуры, т.е. количество решающих блоков в известной структуре; 99 - дополнительные затраты обо AOf . рудования на организацию управления, ввода и вывода информации, составляющие обычно 101 от общих затрат. Предлагаемая цифровая интегрирующая структура позволяет увеличить вычислительную мощность в К раз и при этом затраты оборудования соетавляют:Q, avi.qv,-t-kdvireogiCMK)lQTp би Г )lQ ц .«ЗиОдц.чр;, где U0p затраты оборудования на оди вычислительный блок; Чрг затраты оборудования на оди регистр разрядностью I, в блоке динамических регистро

И (К.И )

%..

ЦИС ,(KV1Qp6-(K-l)V Qвp4dи KQ,.K.dиГeog,J.(иK)-l0 p+dиreo,J(ИK)1 ,)

Так как Qo((-). иАИ ()-арБ QpeB среднем составляет Qps SO-Q, а Qg{«60-Qv,, затраты представляют собой затраты на один триггер с выходной логической схемой и составля- JQ ставляют ,,, то,следовательно, ют Ц„р - 2Q, а затраты Q представ9ццс. Kvi.fto-vdrt K J.

цис Ки О-СК- и-Зо биЧл-каиГео СиЮТ 2vdnreog-.(nK)lCK-i) - dn2сиK-D

8013dv vi

K-1

3o-ah 2drtog(hK)V dreog-atviioi aaii80 -езйиК Bo ban -Bareog-j CMnv Uo-sd-ar Учитывая что , п 20т50, была проведена в соответствии с получившимся соотношением оценка затрат оборудования для различных значений К, при этом оказалось, что - уК Таким образом, предлагаемая ЦИС, используя то же количество вычислительных блоков, что и в известных ЦИС, позволяет увеличить в К раз вычислительную мощность, при затратах оборудования в среднем (в S/tj-K раз меньших, чем для известных ЦИС такой же мощности. Формула изобретения 1, Цифровая интегрирующая структура, содержащая блок ввода, блок

ляют сооой затраты на один элемент памяти (триггер) с выходной логической схемой и Двухвходовым элементом И, управляемым этим триггером, и со14затраты оборудования на один узел выделения приращений; затраты оборудования на один двухвходовой элемент И; затраты оборудования на один триггер регистров блока задания выборки интеграторрв; затраты оборудования на один элемент ИЛИ блока задания выборки интеграторов; Q 7 затраты .оборудования на один дешифратор блока задания выборки интеграторов. В то же время при увеличении вылительной мощности известной ЦИС в аз затраты оборудования составт : QUHC knQpp+-d(nk) ( + Цдор. Учитывая, что О р Q, получаем viK)) вывода, блок управления, блок коммутации , вычислительные блоки ,причем первый выход блока управления соединен с входом блока ввода и управляющими входами вычислительных блоков, а второй выход - с первым входом блока вывода, отличающаяся тем, что, с целью сокращения аппаратных затрат, в нее введены блок динамических регистров, блок квантованных приращений и блок задания выборки интеграторов, причем управляющий вход блока динамических регистров соединен с первым выходом блока управления, а выходы - с входами блока вывода и входами подынтегральной функции вычислительных блоков соответственно, вход начального значения подынтегральной функции блока динамических регистров соединен с первым выходом блока ввода, входы подынтегральной функции - с выходами суммы значений подынтегральной функции вычислительных блоков, выходы остатков интеграла которых соединены с первой группой входов блока квантованных приращений и входами остатков интегралов блока динамических регистров, вторая группа входов блока квантован ных приращений соединена с третьим выходом блока управления, а выходы с первой группой входов блока коммутации, вторая группа входов которого соединена с выходами блока задания выборки интеграторов, первый вход которого соединен с вторым выходом блока ввода, а второй - с третьим выходом блока управления, входы приращения подынтегральной фу ции вычислительных блоков соединены с выходами блока коммутации. 2. Цифровая структура по nrl, о личающаяся тем, что блок динамических регистров состоит из ri динамических регистров, каждый из которых состоит из К регистров поды тегральной функции, К регистров остатка интеграла, первой и третьей группы элементов И по (К-1 J элементу в группе, второй и четвертой группы элементов М по К элементов в группе, двух групп из (К-1) элементов НЕ, входного элемента ИЛИ и дву выходных элементов ИЛИ, причем выход i- го регистра подынтегральной функции соединен -с первым входом i-ro элемента И первой группы за исключением К-го регистра подынтегральной функции, выход i-ro элемента И первой труппы соединен с вх . дом (i+1)-ro регистра подынтегральной функции, вход первого регистра подынтегральной функции соединен с выходом входного элемента ИЛИ, вход которого являются входами подынте - ральной функции блока, выходы регис ров подынтегральной функции соединены с первыми входами соответствую щих элементов И второй группы, выход

которых подключены к входам первого выходного элемента ИЛИ, выход которого является выходом подынтегральной функции блока, вторые входы элементов И второй группы и входы элементов НЕ первой группы подключены к управляющим входам блока, выходы элементов НЕ этой группы соединены с

новки единицы третьего триггера и через второй элемент задержки с первым входом третьего элемента ИЛИ выход которого подключен к входу установки нуля второго триггера, выход первого элемента ИЛИ соединен с входами установки нуля первого и третьего три|- героз, третий выход наборного поля торыми входами элементов И первой руппы, выходы регистров остатков инегралов, кроме К-го,соединены с перыми входами элементов И третьей групы, выход i-ro элемента И третьей руппы соединен с входом (i+l)-ro регистра остатка интеграла, вход первого регистра остатка интеграла являтся входом остатка интеграла блока, выходы регистров остатка интеграла соединены с первыми входами соответствующих элементов И четвертой группы выходы которых подключены к входам второго выходного элемента ИЛИ, выход которого является выходом остатка интеграла блока, вторые входы элементов И четвертой группы и входы элементов НЕ второй группы соединены с управляющими входами блока, выход i-ro элемента НЕ второй группы соединен с вторым входом I-го элемента И третьей группы. 3. Цифровая структура по п.1, о тличающ.аяся тем, что блок коммутации содержит К групп двухвходовых элементов И, первые входы которых являются входами квантованных приращений блока, а вторые - управляющими входами блока, а выходы являются выходами блока. k. Цифровая структура по п.1, о тличающаяся тем, что блок управления содержит три триггера,наборное поле, два дешифратора, группу триггеров, регистр, счетчик, две группы элементов И, пять элементов И, три элемента ЗЭдержки, элемент НЕ, три элемента ИЛИ, группы элементов сравнения и генератор импульсов, причем первый выход наборного поля соединен с входом установки единицы первого триггера, выход которого соединен с первым входом первого элемента И, выход которого через первый элемент задержки соединен с первыми входами первого и второго элементов ИЛИ, второй выход наборного поля соединен с входом установки единицы второго триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом устасоединен с вторыми входами первого, второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым входом счетчика, группа выходов наборного поля соединена с входами первого дешифратора и первой группой входов элементов сравнения группы, вторая группа входов группы элементов сравнения соединена с выходами счетчика, второй вход которого соединен с выходом третьего элемента И, выход элементов сравнения группы через третий элемент задержки соединен с первым входом четвертого элемента И и через элемент НЕ с первым входом третьего элемента И, выход третьего элемента задержки соединен с вторым входом первого элемента И, выход третьего триггера соединен с вторыми входами третьего и четвертого элементов И, выход четвертого.элемента И соедииен с третьим входом счетчика, выходы которого соединены с входами второго дешифратор, выходы которого соединены с первыми входами элементов И первой группы, выход генератора импульсов соединен с входом синхронизации регистра, выходы которого соедияены с первой группой входов элементов И второй группы и входами пятого элемента И, выход которого соединен с информационным входом регистра, выходы элементов И второй группы соединены с входами триггеров группы, третьими входами первого, третьего и четвертого элементов И, вторым входом второго элемента И, выход три|- ге.ров группы соединен с вторыми входами элементов И первой группы, третий и четвертый выходы наборного поля выход третьего триггера, выходы первого дешифратора, выходы элементов И

второй группы, выходы триггеров группы и генератора импульсов подключены к первой группе выходов блока, третий выход наборного поля, выход второго элемента И, выходы элементов И второй группы и генератора импульсов являются выходами блока второй группы, выходы элементов И первой группы и третий выход наборного поля являются выходами блока третьей группы,

5.Цифровая структура по п,1, отличающаяся тем, что блок задания выборки интеграторов содержит п дешифраторов, группу элементов ИЛИ и п регистров, причем информационные входы регистров являются информационными входами блока, а входы синхронизации - управляющими

входами блока, i-e выходы регистров соединены с входами i-x элементов ИЛИ группы, выходы этих элементов соединены с входами дешифраторов, выходы которых являются выходами

блока.

6.Цифровая структура по п.1, о тличающаяся тем, что блок квантованных приращений состоит из регистра и двухвходовых элементов И,

первые входы которых являются информационными входами блока, а вторые управляющими входами блока, выходы элементов И подключены к входам регистра, выходы которого являются выходами блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 81916, кл. G Об J 1/02, 1975.

2.Авторское свидетельство СССР № 532112, кл. G Об J 1/02, 1976 (прототип),

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

.З

Авторы

Даты

1982-09-23—Публикация

1980-07-10—Подача