Изобретение относится к вычислительной технике и предназначено для использования в системах полуавтома- TPwecKoro и ручного управления высокодинамичными объектами или быстро протекающими процессами с прогнозированием результатов управления.

Цель изобретения - расширение области применения за счет введения и технической реализации режима периодического решения систем уравнений с быстродействием, обеспечивающим прогнозирование результатов управления, и согласования времени ре акции человека-оператора со скоростью протекания управляемого процесса.

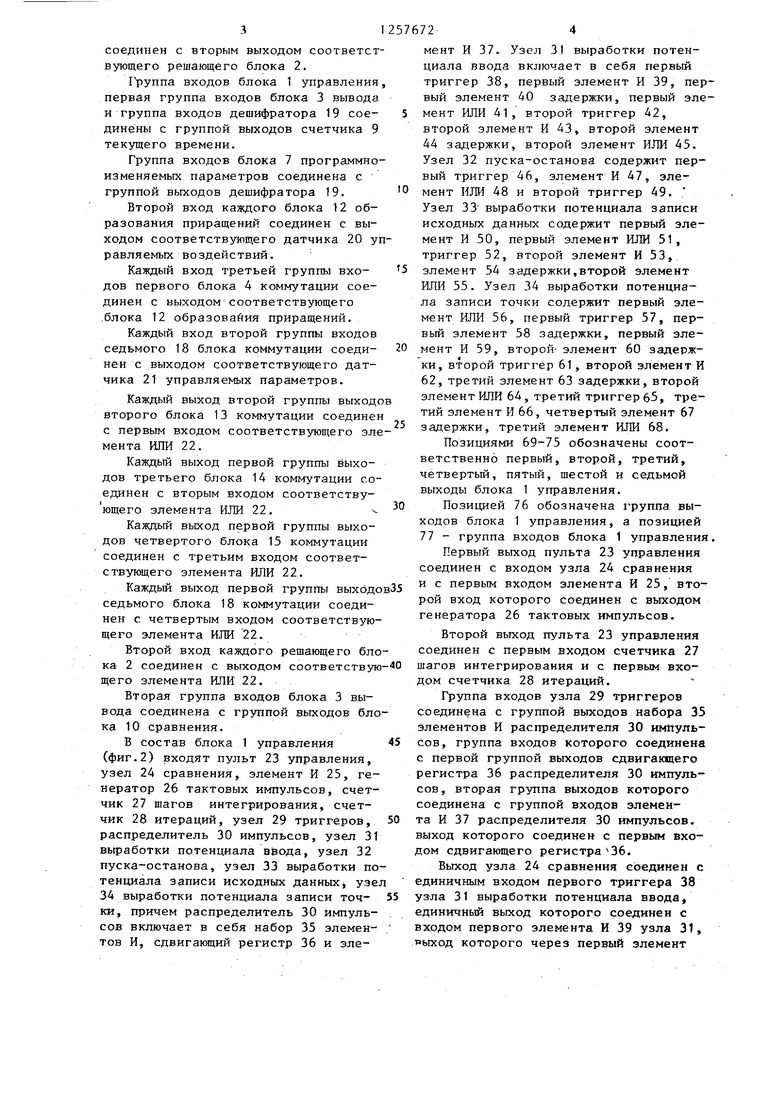

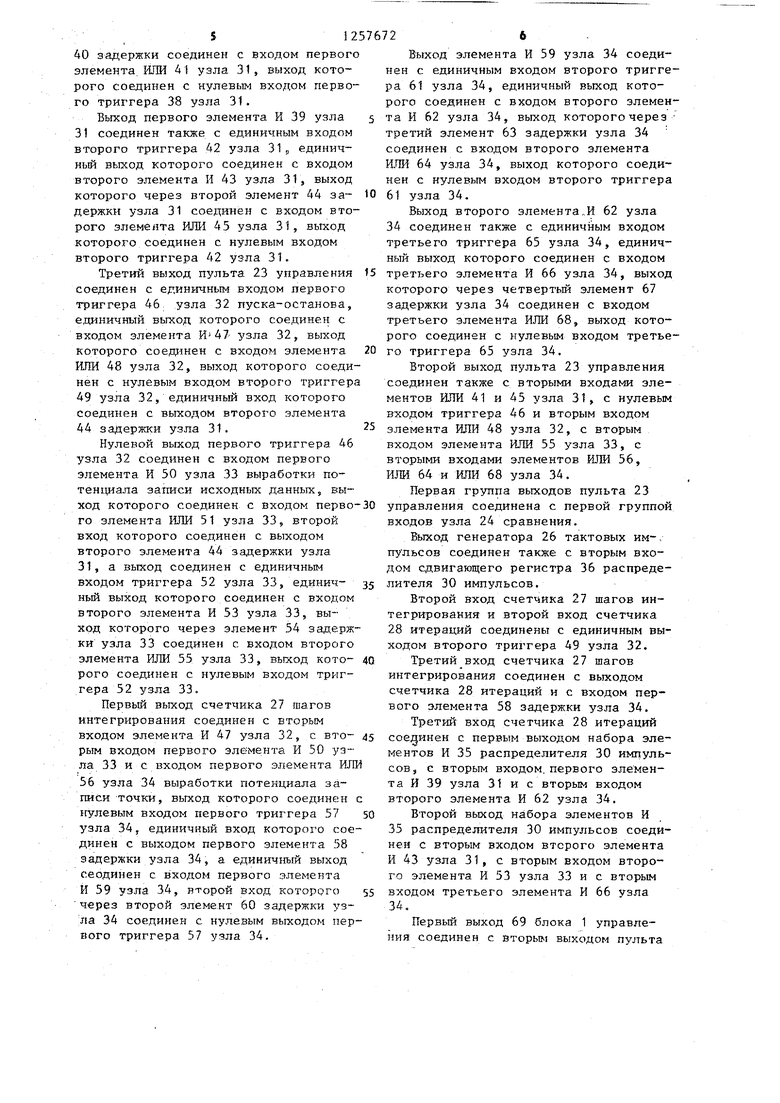

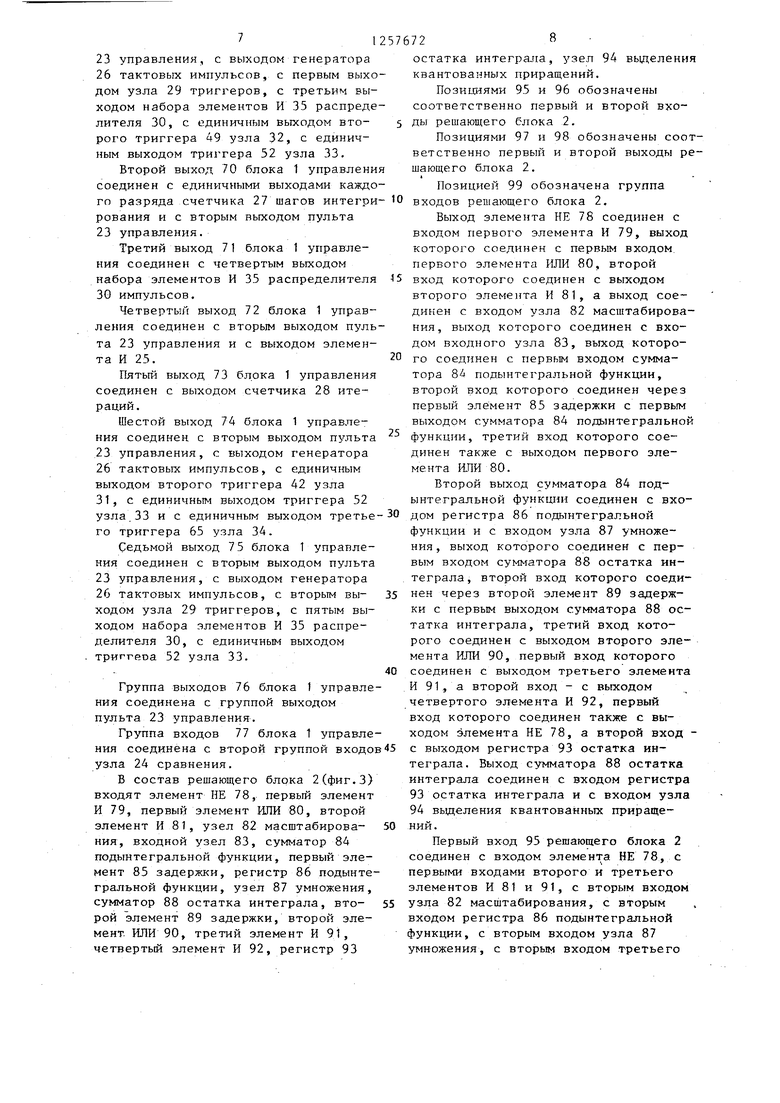

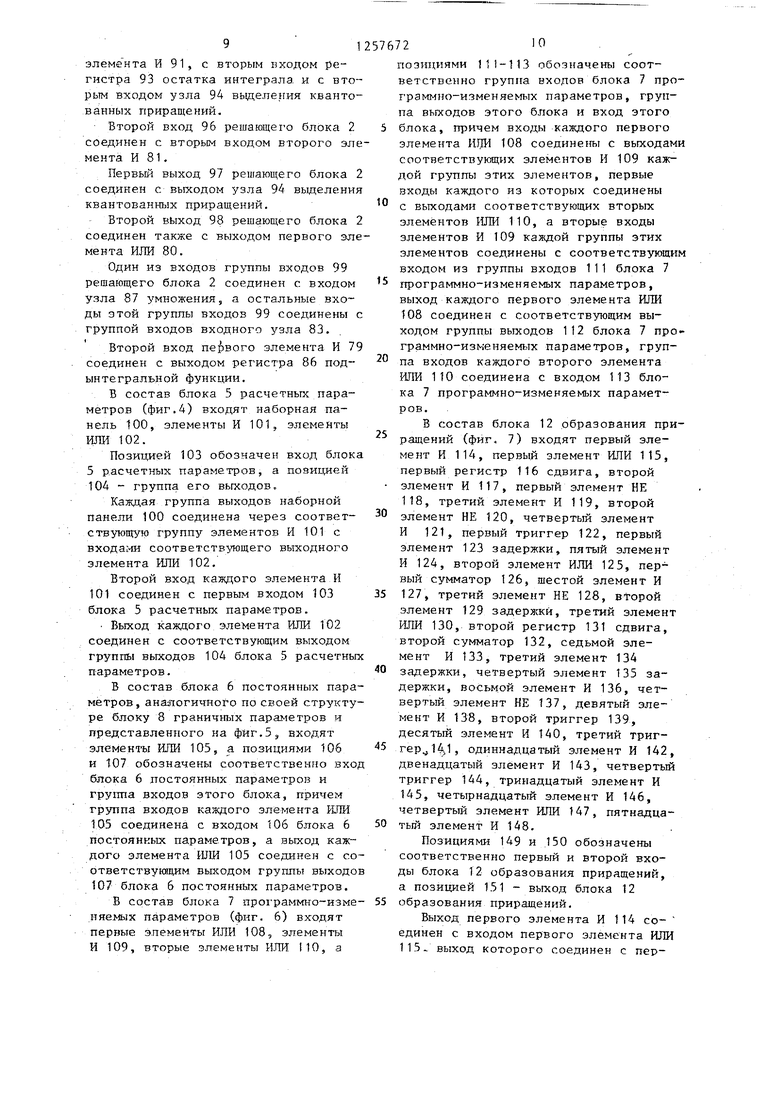

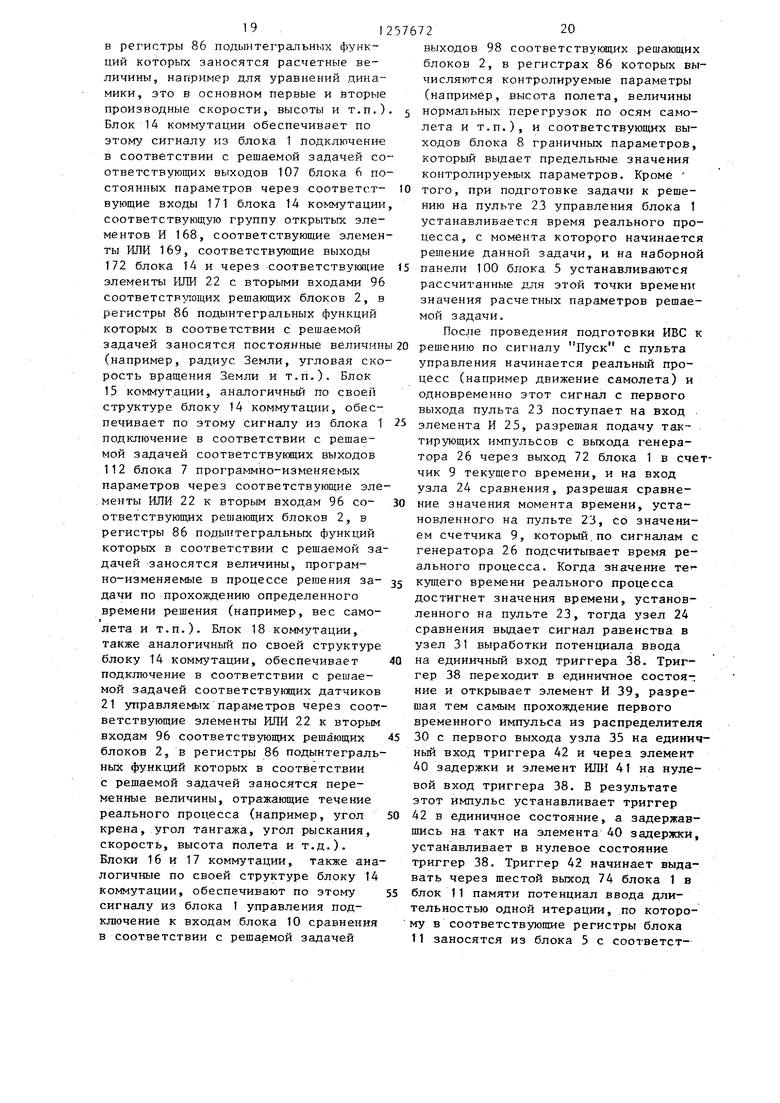

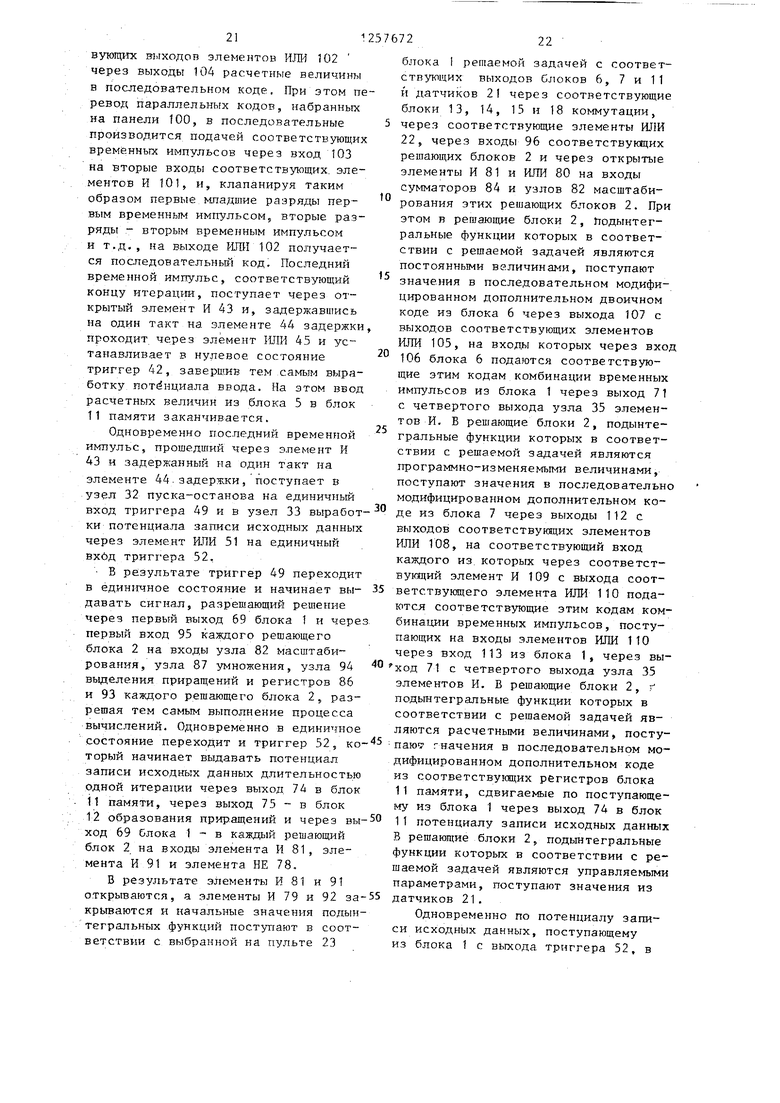

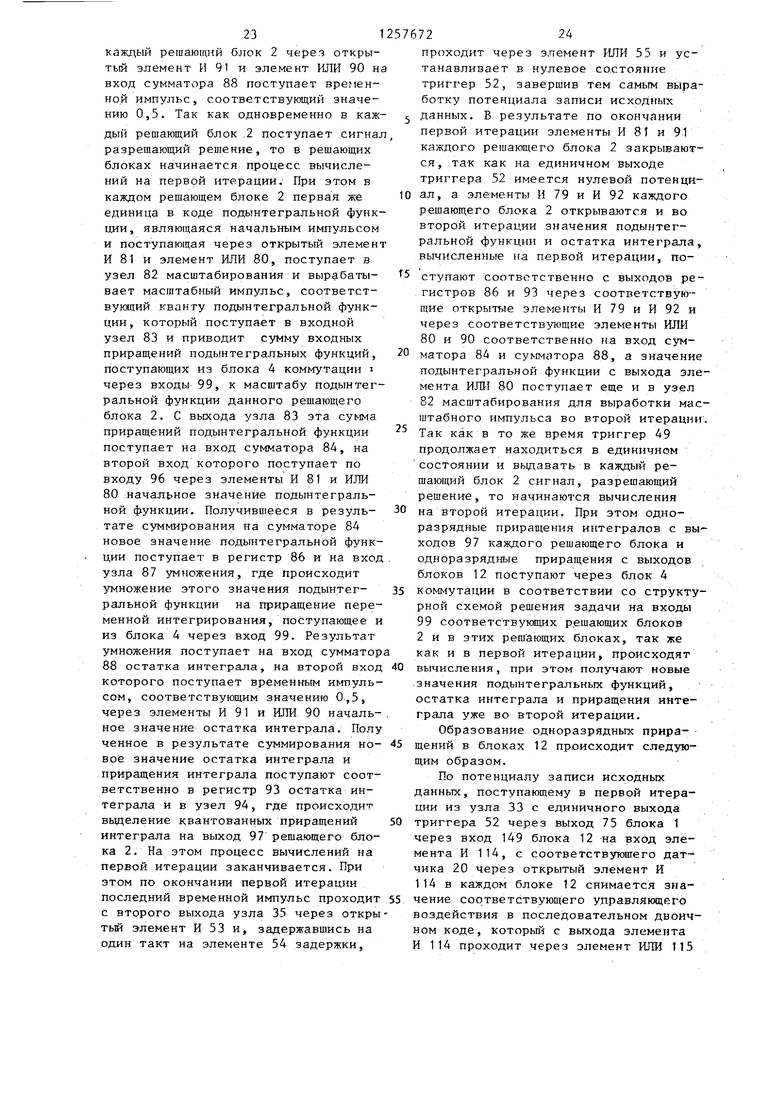

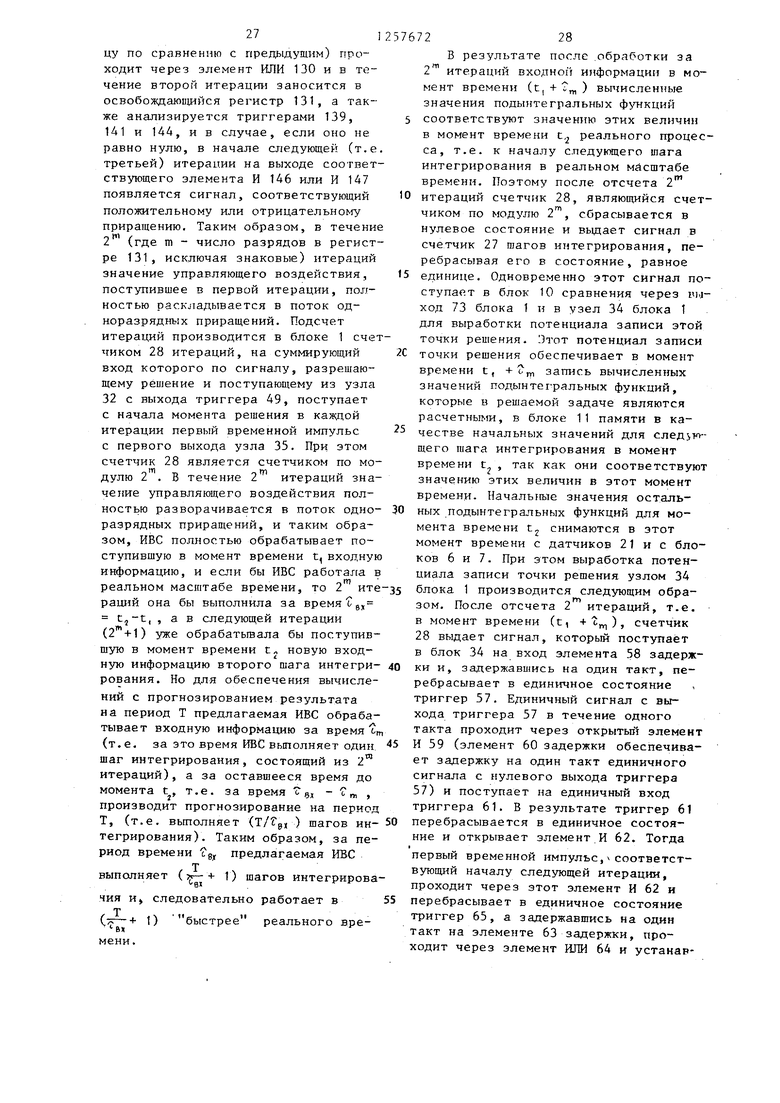

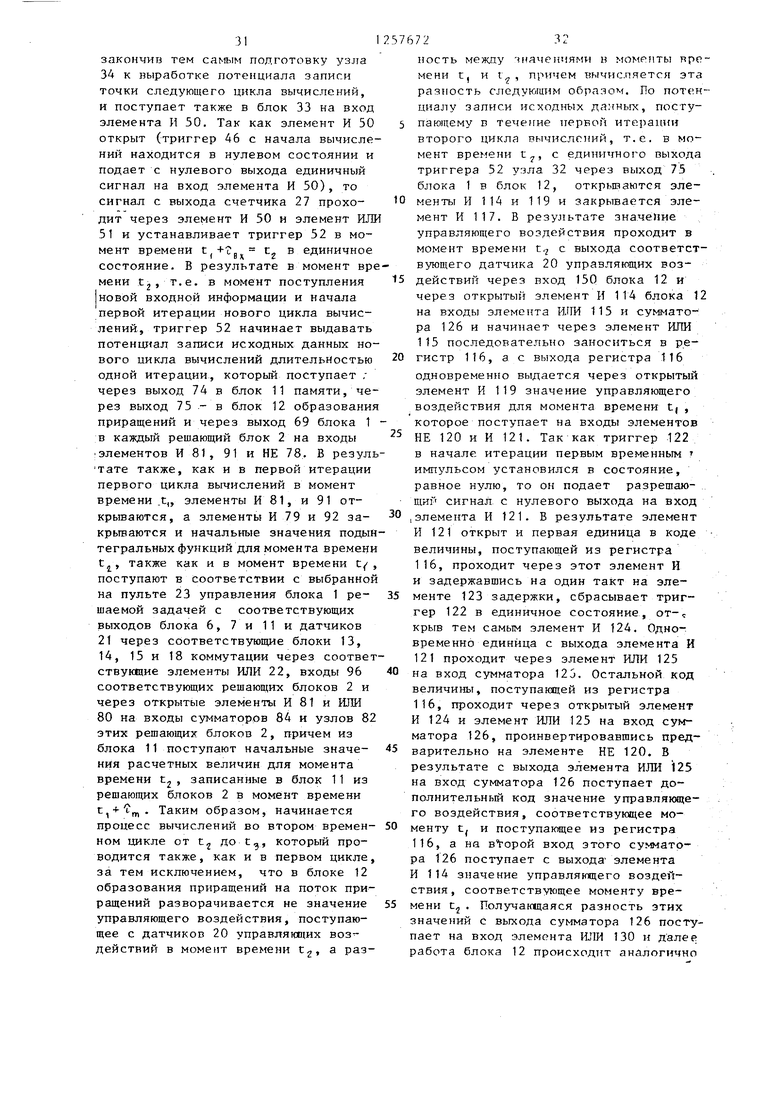

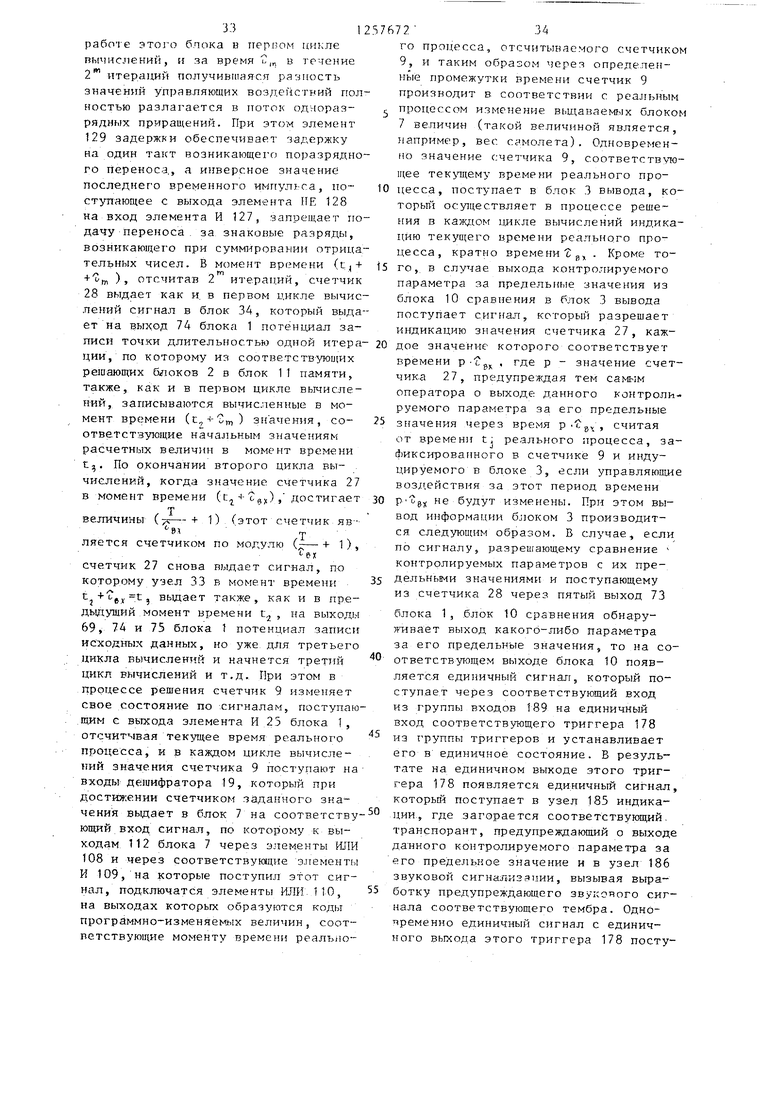

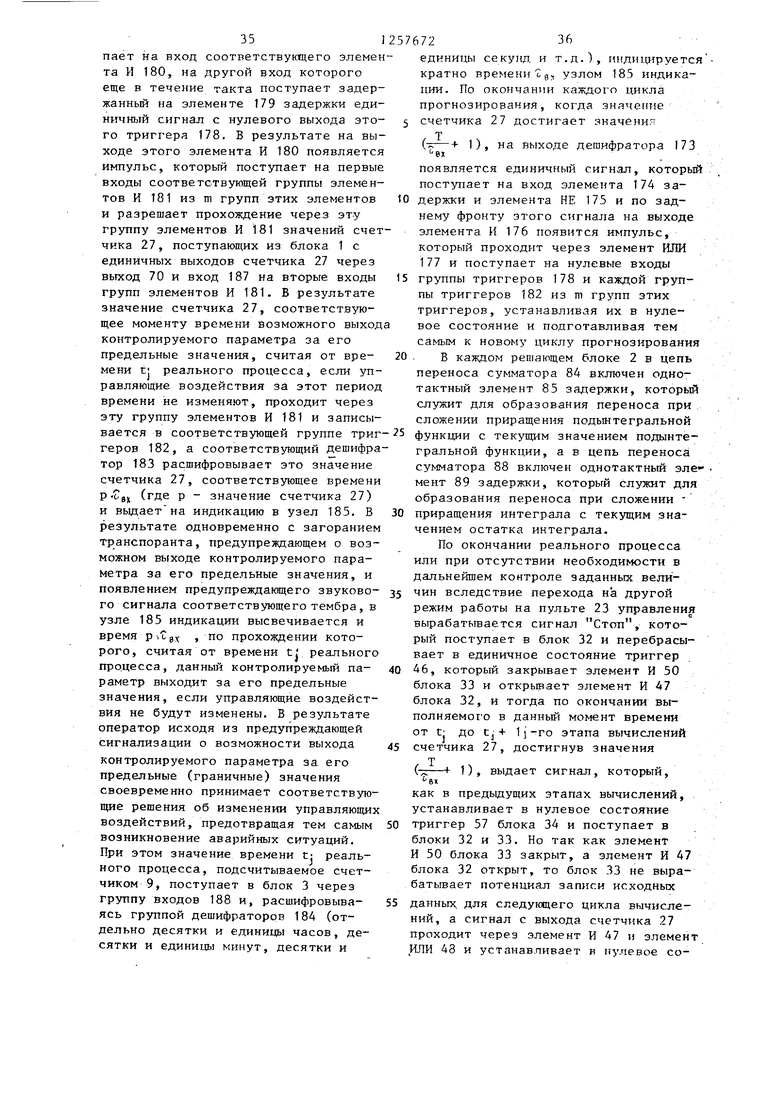

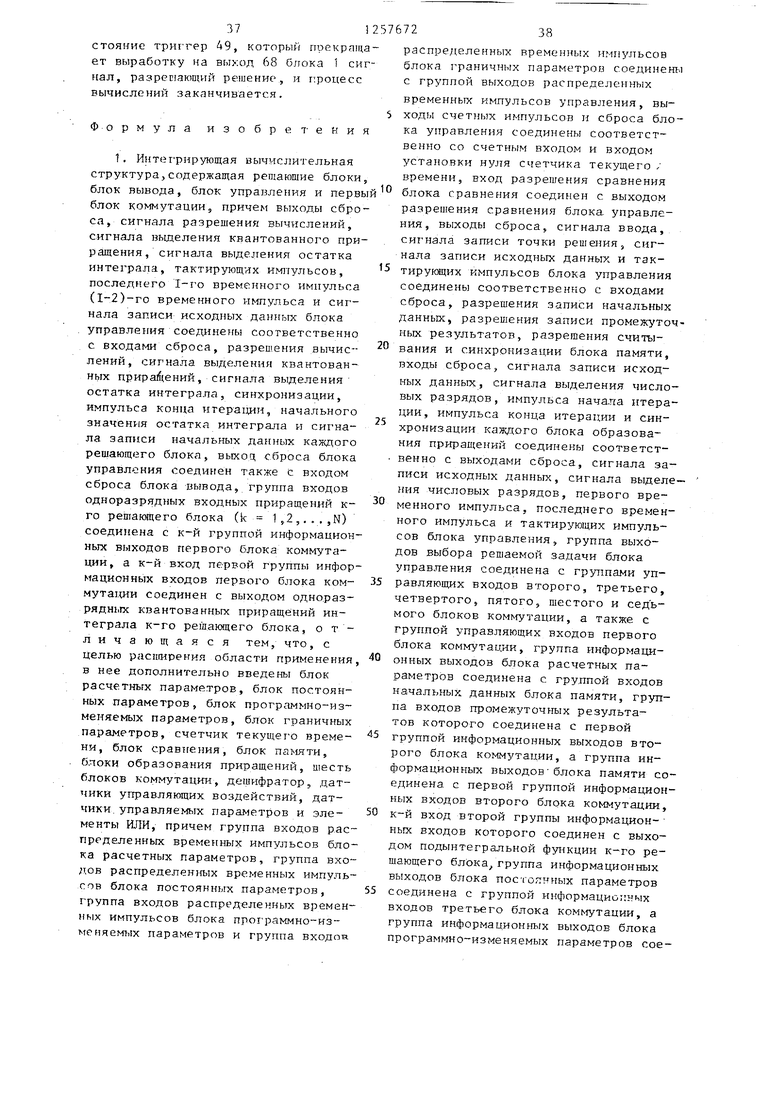

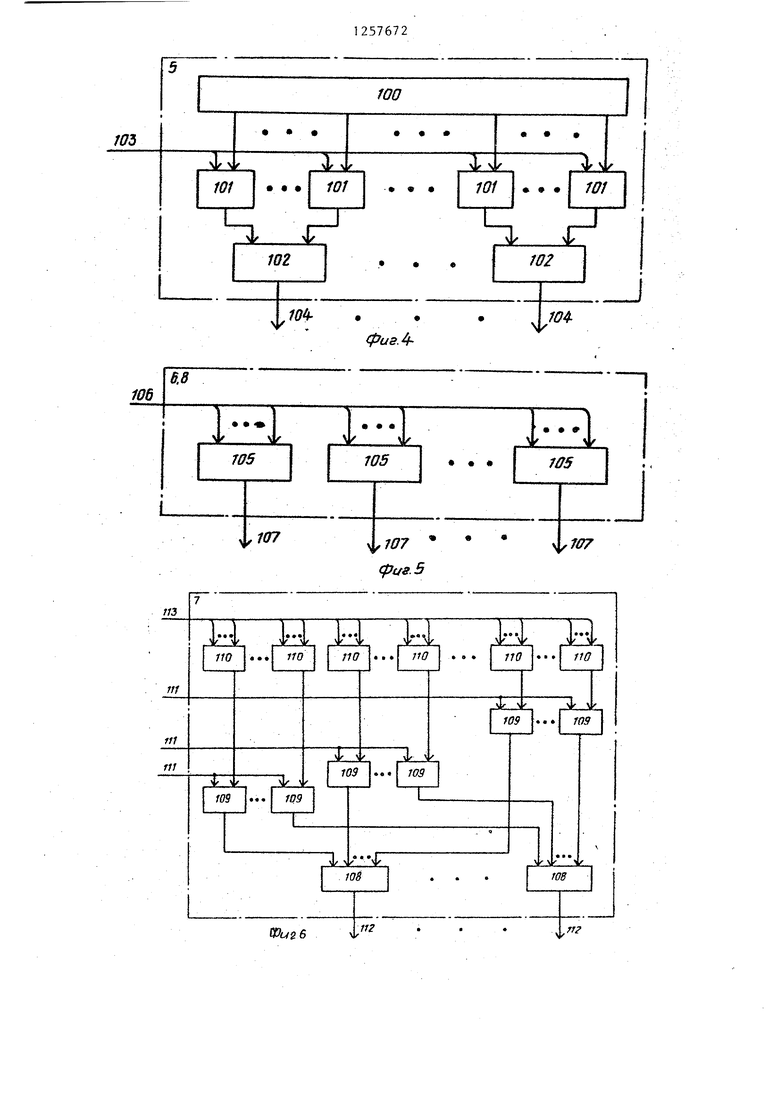

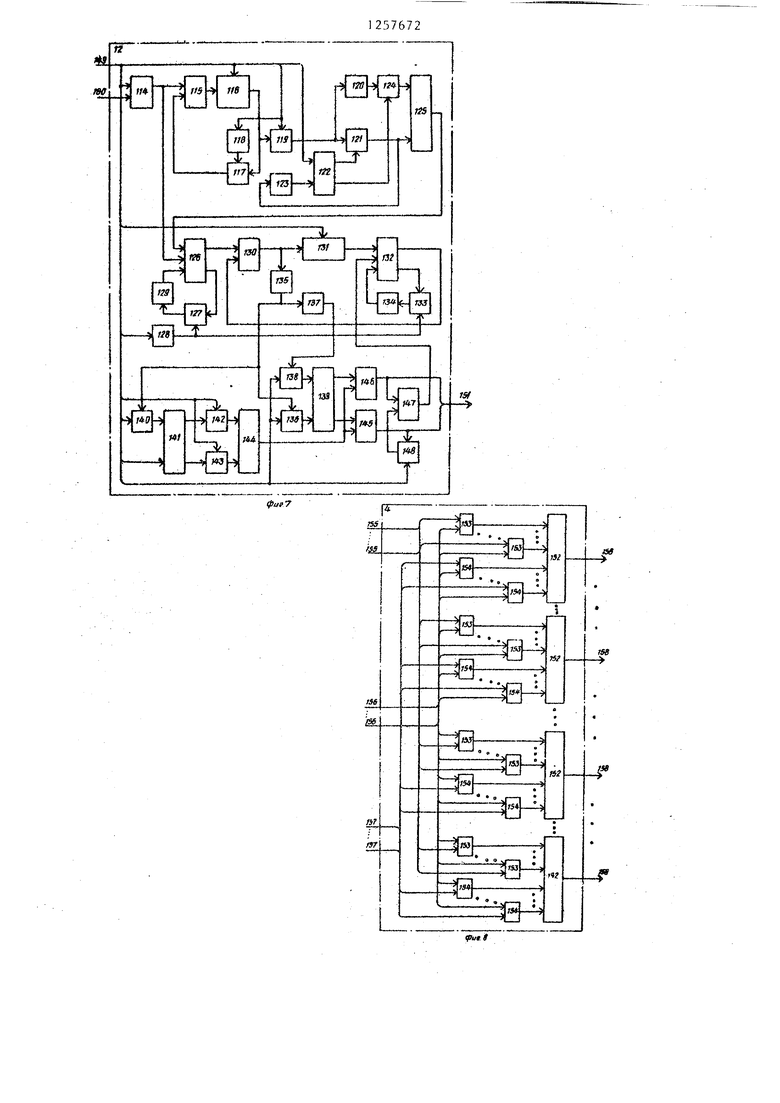

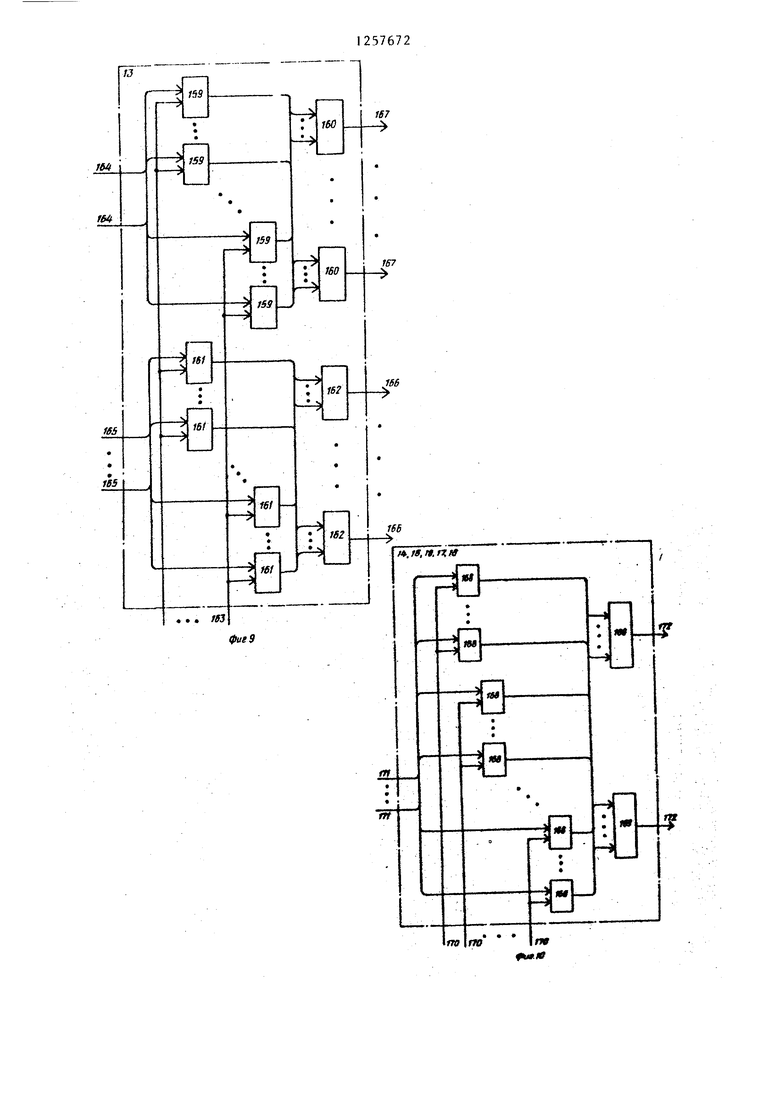

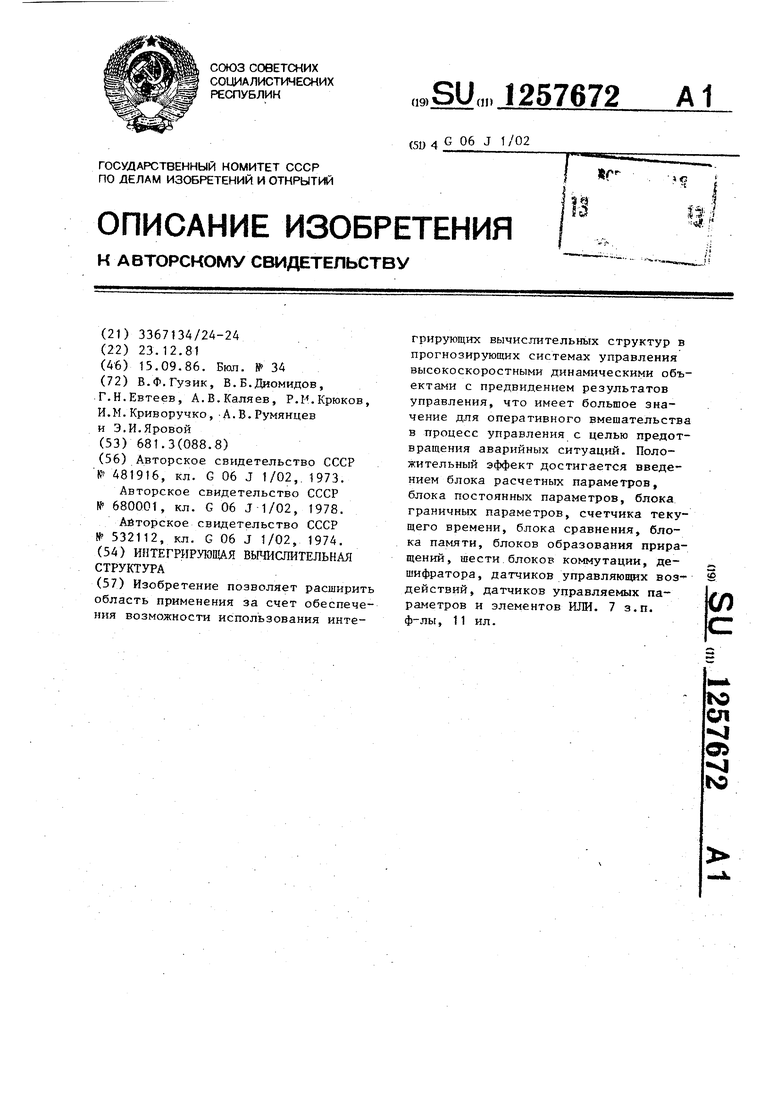

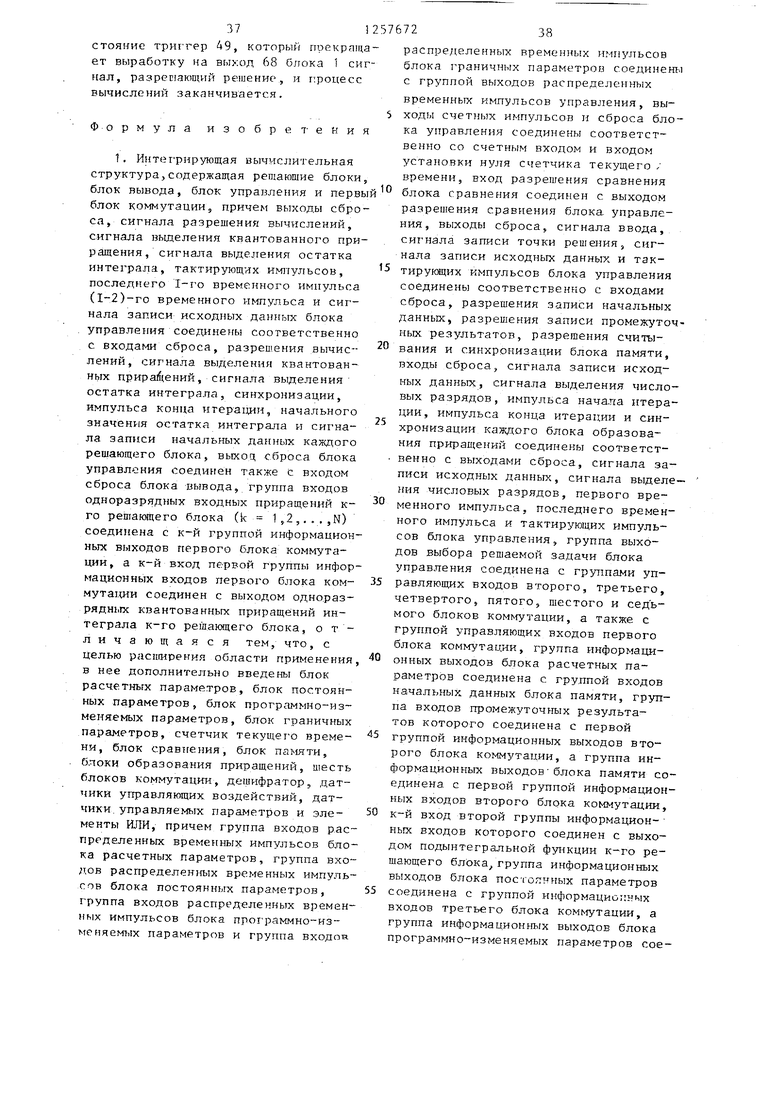

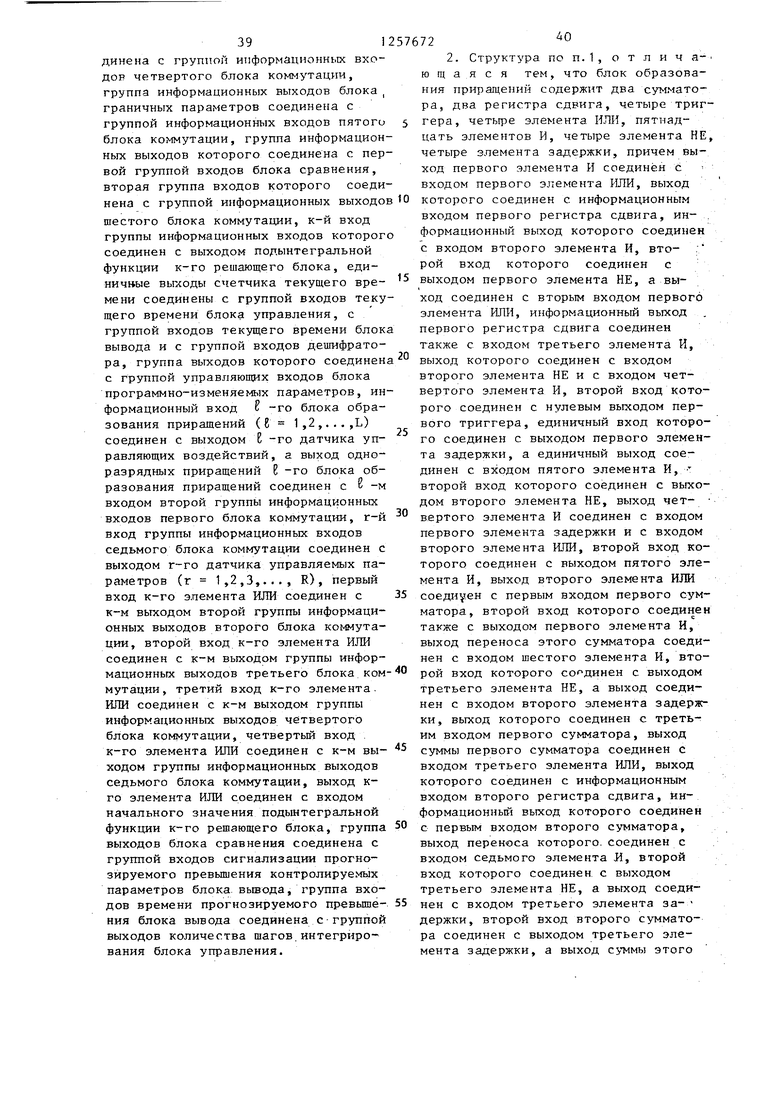

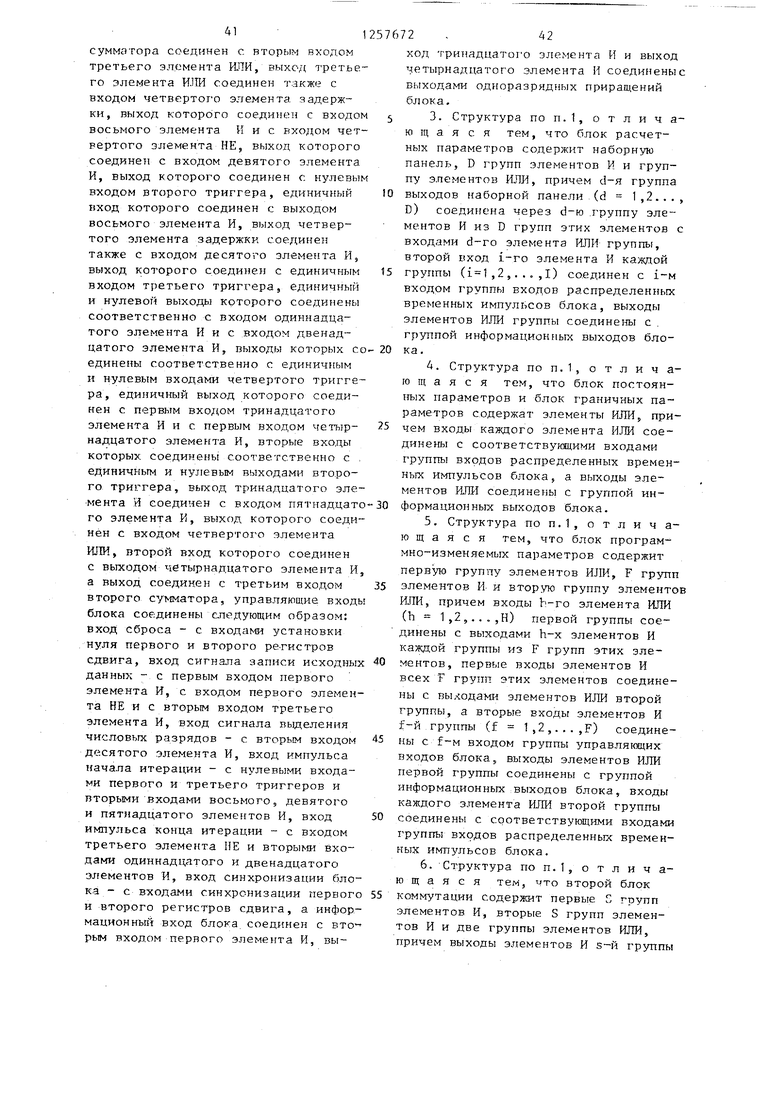

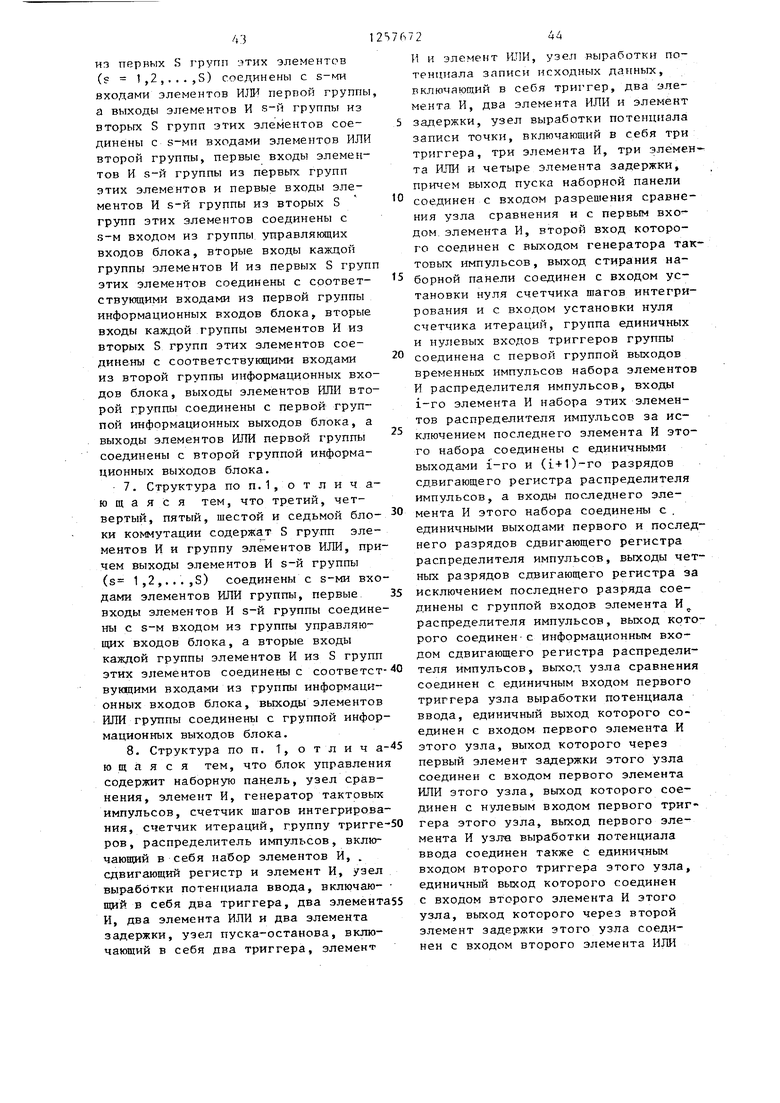

На фиг. 1 изображена блок-схема интегрирующей вычислительной структуры (НВС); на фиг.2 - пример реализа- ции блока управления-, на фиг, 3 - схема реализации решающего блока; на фиг.4 - схема реализации блока расчетных параметров; на фиг.5 - схема реализации аналогичных по CBoepi структуре блока постоянных параметро и блока граничных параметровj на фиг.6 - схема реализации блока программно-изменяемых параметров; на фиг.7 схема реализации блока обра- зования приращений; на фиг.8 - схема реализации первого блока коммутации j на фиг.9 - схема реализации второго блока коммутации; на фиг.10 - схема реализации аналогичных по свое структуре третьего, четвертого, пятого, шестого и седьмого блоков коммутации} на фиг.11 - схема реализации блока вывода.

В состав интегрирующей вычисли- .тельной структуры (фиг.1) входят бло 1 управления, решающие блоки 2, блок 3 вывода, первый блок 4 коммутации, блок 5 расчетных параметров, блок 6 постоянных параметров, блок 7 про- граммно-изменяемь х параметров, блок 8 граничных параметров, счетчик 9 текущего BpcMetm, блок 10 сравнения, блок 11 памяти, блоки 12 образования приращений, второй 13, третий 14, четвертый 15, пятый 16, шестой 17, седьмой 18 блоки коммутации, дешифратор 19, датчики 20 управляющих воздействий, датчики 21 управляемых параметров, элементы ИЛИ 22.

Первый вьгхоц блока 1 управления соединен с пepвы входом каждого решающего блока 2, а второй выход - с

0

15

5

20 0 35

40 45 50 55

входом блока 3 вьрвода. Г руппа входов каждого решающего блока 2 соединена с соответствующей группой выходов первого блока 4 коммутации, каждый вход первой группы входов которого соединен с первым выходом соответствующего решающего блока 2.

Третий выход блока 1 управления соединен с входом блока 5 расчетных параметров, с входом блока 6 постоянных параметров, с входом блока 7 программно-изменяемых параметров и с входом блока 8 граничных параметров. Четвертый выход блока 1 управления соединен с входом счетчика 9 текущего времени, а пятый выход соединен с входом блока 10 сравнения.

Шестой выход блока 1 управления соединен с входом блока 11 памяти, а седьмой выход соединен с первым входом каждого блока 12 образования приращений.

Группа выходов блока 1 управления соединена с второй группой входов первого блока 4 коммутации и с первыми группами входов второго блока 13 коммутации, третьего блока 14 коммутации, четвертого 15, пятого 16, шестого . 17 и седьмого 18 блоков коммутации.

Группа выходов блока 5 расчетных параметров соединена с первой группой входов блока 11 памяти, вторая группа входов которого соединена с первой группой выходов второго блока 13 коммутации, а группа выходов соединена с второй группой входов второго блока 13 коммутации, каждый вход третьей группы входов которого соединен с вторым выходом соответствующего решающего блока 2.

Группа выходов блока 6 постоянных параметров соединена с второй группой входов третьего блока 14 коммутации. Группа выходов блока 7 программно- изменяемых: параметров соединена с второй группой входов четвертого блока 15 коммутации.

Группа выходов блока 8 граничных - параметров соединена с второй группой входов пятого блока 16 коммутации, группа В1 1ходов которого соединена с первой группой входов блока 10 сравнения, вторая группа входов которого соединена с группой выходов шестого блока 17 коммутации, каждый вход второй группы входов которого

3

соединен с вторым выходом соответствующего решающего блока 2.

Группа входов блока 1 управления, первая группа входов блока 3 вывода и группа входов дешифратора 19 соединены с группой выходов счетчика 9 текущего времени.

Группа входов блока 7 программно- изменяемых параметров соединена с группой выходов дешифратора 19.

Второй вход каждого блока 12 образования приращений соединен с выходом соответствующего датчика 20 управляемых воздействий.

Каждый вход третьей группы входов первого блока 4 коммутации соединен с выходом соответствующего .блока 12 образовайия приращений.

Каждый вход второй группы входов седьмого 18 блока коммутации соединен с выходом соответствующего датчика 21 управляемых параметров.

Каждый выход второй группы выходо второго блока 13 коммутации соединен

1

с первым входом соответствующего элемента ИЛИ 22.

Каждый выход первой группы выходов третьего блока 14 коммутации соединен с вторым входом соответству- ющего элемента ИЛИ 22.Каждьш выход первой группы выходов четвертого блока 15 коммутации соединен с третьим входом соответствующего элемента ИЛИ 22.

Каждый выход первой группы выхбдо седьмого блока 18 коммутации соединен с четвертым входом соответствующего элемента ИЛИ 22.

Второй вход каждого решающего блока 2 соединен с выходом соответствую щего элемента ИЛИ 22.

Вторая группа входов блока 3 вывода соединена с группой выходов блока 10 сравнения.

В состав блока 1 управления (фиг.2) входят пульт 23 управления, узел 24 сравнения, элемент И 25, генератор 26 тактовых импульсов, счетчик 27 шагов интегрирования, счетчик 28 итераций, узел 29 триггеров, распределитель 30 импульсов, узел 31 выработки потенциала ввода, узел 32 пуска-останова, узел 33 выработки потенциала записи исходных данных узел 34 выработки потенциала записи точ- ки, причем распределитель 30 импуль- сов включает в себя набор 35 элемен- тов И, сдвигакнций регистр 36 и эле

в

30

35

О

55 , ;

2576724

мент И 37. Узел 31 выработки потенциала ввода включает в себя первый триггер 38, первый элемент И 39, первый элемент 40 задержки, первый эле- 5 мент ИЛИ 41, второй триггер 42,

второй элемент И 43, второй элемент 44 задержки, второй элемент ИЛИ 45. Узел 32 пуска-останова содержит первый триггер 46, элемент И 47, эле 0 мент ИЛИ 48 и второй триггер 49. Узел 33 выработки потенциала записи исходных данных содержит первый элемент И 50, первый элемент ИЛИ 51, триггер 52, второй элемент И 53,

5 элемент 54 задержки,второй элемент ИЛИ 55. Узел 34 выработки потенциала записи точки содержит первый элемент ИЛИ 56, первый триггер 57, первый элемент 58 задержки, первый эле20 мент И 59, второй- элемент 60 задержки, второй триггер 61, второй элемент И 62, третий элемент 63 задержки, второй элемент ИЛИ 64, третий триггер 65, третий элемент И 66, четвертый элемент 67

25 задержки, третий элемент ИЛИ 68.

Позициями 69-75 обозначены соответственно первый, второй, третий, четвертьш, пятый, шестой и седьмой выходы блока 1 управления.

Позицией 76 обозначена группа выходов блока 1 управления, а позицией 77 - группа входов блока 1 управления.

Первый выход пульта 23 управления соединен с входом узла 24 сравнения и с первым входом элемента И 25, вто- рой вход которого соединен с выходом генератора 26 тактовых импульсов.

Второй выход пульта 23 управления соединен с первым входом счетчика 27 шагов интегрирования и с первым входом счетчика 28 итераций.

Группа входов узла 29 триггеров соединена с группой выходов набора 35 элементов И распределителя 30 импульсов, группа входов которого соединена с первой группой выходов сдвигающего регистра 36 распределителя 30 импульсов , вторая группа выходов которого соединена с группой входов элемента И 37 распределителя 30 импульсов. выход которого соединен с первым входом сдвигакнцего регистра 36.

Выход узла 24 сравнения соединен с единичным входом первого триггера 38 узла 31 выработки потенциала ввода, единичный выход которого соединен с входом первого элемента И 39 узла 31, пьгход которого через первый элемент

45

50

40 задержки соединен с входом первого элемента. ИЛИ 41 узла 31, выход которого соединен с нулевым входом первого триггера 38 узла 31.

Выход первого элемента И 39 узла 31 соединен также с единичным входом второго триггера 42 узла 31 единичный выход которого соединен с входом второго элемента И 43 узла 31, выход которого через второй элемент 44 за- держки узла 31 соединен с входом второго элемента ИЛИ 45 узла 31, выход котора.го соединен с нулевым входом второго триггера 42 узла 31.

Третий выход пульта 23 управления соединен с единичным входом первого триггера 46. узла 32 пуска-останова, е,циничный выход которого соединен с входом элемента И 47 узла 32, выход которого соединен с входом элемента ИЛИ 48 узла 32, выход которого соединен с нулевым входом второго триггер 49 узла 32, единичный вход которого соединен с выходом второго элемента 44 задержки узла 31.

Нулевой выход первого триггера 46 узла 32 соединен с входом первого элемента И 50 узла 33 выработки потенциала записи исходных данных, выход которого соединен с входом перво го элемента IfflH 51 узла 33, второй вход которого соединен с выходом второго элемента 44 задержки узла 31, а выход соединен с единичньм входом триггера 52 узла 33, единич- ньй выход которого соединен с входом второго элемента И 53 узла 33, выход которого через элемент 54 задержки узла 33 соединен с входом второго элемента ИЛИ 55 узла 33, выход кото- рого соединен с нулевым входом триггера 52 узла 33.

Первый выход счетчика 27 шагов интегрирования соединен с вторым входом элемента И 47 узла 32, с вто- рым входом первого элемента И 50 узла 33 и с входом первого элемента ИЛ

56 узла 34 выработки потенциала записи -точки, выход которого соедин€ Н нулевым входом первого триггера 57 узла 34, единичный вход которого соединен с выходом первого элемента 58 задержки узла 34, а единичный выход сеодинен с входом первого элемента И 59 узла 34, второй вход которого через второй элемент 60 задержки уз- :ла 34 соединен с нулевым выходом первого триггера 57 узла 34.

Выход элемента И 59 узла 34 соединен с единичным входом второго триггера 61 узла 34, единичный выход которого соединен с входом второго элемента И 62 узла 34, выход которого через третий элемент 63 задержки узла 34 соединен с входом второго элемента ШШ 64 узла 34, выход которого соединен с нулевым входом второго триггера 61 узла 34.

Выход второго элемента„И 62 узла

34соединен также с единичным входом третьего триггера 65 узла 34, единичный выход которого соединен с входом третьего элемента И 66 узла 34, выход которого через четвертый элемент 67 задержки узла 34 соединен с входом третьего элемента ИЛИ 68, выход которого соединен с нулевым входом третьего триггера 65 узла 34.

Второй выход пульта 23 управления соединен также с вторыми входами элементов ИЛИ 41 и 45 узла 31, с нулевым входом триггера 46 и вторым входом элемента ИЛИ 48 узла 32, с вторым входом элемента ИЛИ 55 узла 33, с вторыми входами элементов ИЛИ 56, ИЛИ 64 и ИЛИ 68 узла 34.

Первая группа выходов пульта 23 управления соединена с первой группой входов узла 24 сравнения.

Выход генератора 26 тактовых им-, пульсов соединен также с вторым входом сдвигающего регистра 36 распределителя 30 импульсов.

Второй вход счетчика 27 шагов интегрирования и второй вход счетчика 28 итераций соединены с единичным выходом второго триггера 49 узла 32.

Третий вход счетчика 27 шагов интегрирования соединен с выходом счетчика 28 итераций и с входом первого элемента 58 задержки узла 34.

Третий вход счетчика 28 итераций соединен с первым выходом набора элементов И 35 распределителя 30 импульсов, с вторым входом, первого зле мен- та И 39 узла 31 и с вторым входом второго элемента И 62 узла 34.

Второй выход набора элементов И

35распределителя 30 импульсов соединен с вторым входом второго элемента И 43 узла 31, с вторым входом второго элемента И 53 узла 33 и с вторым входом третьего элемента И 66 узла 34.

Первый выход 69 блока 1 управления соединен с вторым выходом пульта

23 управления, с выходом генератора 26 тактовых импульсов, с первым выходом узла 29 триггеров, с третьим выходом набора элементов И 35 распределителя 30, с единичным выходом второго триггера 49 узла 32, с единичным выходом триггера 52 узла 33,

Второй выход 70 блока 1 управления соединен с единичными выходами каждого разряда счетчика 27 шагов интегри- О входов решающего блока 2, рования и с вторым выходом пульта 23 управления.

Третий выход 71 блока 1 управления соединен с четвертым выходом набора элементов И 35 распределителя -15 30 импульсов.

Четвертый выход 72 блока 1 управления соединен с вторым выходом пульта 23 управления и с вь ходом элемента И 25.20

Пятый выход 73 блока 1 управления соединен с выходом счетчика 28 итераций.

Шестой выход 74 блока 1 управления соединен с вторым выходом пульта 23 управления, с выходом генератора 26 тактовых импульсов, с единичным выходом второго триггера 42 узла 31, с единичным выходом триггера 52 узла. 33 и с единичньпч выходом третье-30 го триггера 65 узла 34.

Седьмой выход 75 блока 1 управления соединен с вторым выходом пульта с выходом генератора

вторым вы- 35

25

23 управления, 26 тактовых импульсов, с ходом узла 29 триггеров, ходом набора элементов И делителя 30, с единичным триггеоа 52 узла 33.

с пятым вы- 35 распре- выходом

Выход элемента НЕ 78 со входом первого элемента И которого соединен с первым первого элемента ИЛИ 80, в вход которого соединен с в второго элемента И 81, а в динен с входом узла 82 мас ния, выход которого соедин дом входного узла 83, выхо го соединен с первым входо тора 84 подынтегральной фу второй вход которого соеди первый элемент 85 задержки выходом сумматора 84 подьш функции, третий вход котор динен также с выходом перв мента ИЛИ 80.

Второй выход сумматора ынтегральной функции соеди дом регистра 86 подынтегра функции и с входом узла 87 ния , выход которого соедин вым входом сумматора 88 ос теграла, второй вход котор нен через второй элемент 8 ки с первым выходом суммат татка интеграла, третий вх рого соединен с выходом вт мента ИЛИ 90, первый вход соединен с выходом третьег И 91, а второй вход - с вы четвертого элемента И 92, вход которого соединен так ходом элемента НЕ 78, а вт с выходом регистра 93 оста теграла. Выход сумматора 8 интеграла соединен с входо

Группа выходов 76 блока 1 управления соединена с группой выходом пульта 23 управления.

Группа входов 77 блока 1 управления соеди:нена с второй группой входов узла 24 сравнения.

В состав решающего блока 2(фиг.З) входят элемент НЕ 78, первый элемент И 79, первый элемент ИЛИ 80, второй элемент И 81, узел 82 масштабирова- ния, входной узел 83, сумматор 84 подынтегральной функции, первый элемент 85 задержки, регистр 86 подынтегральной функции, узел 87 умножения, сумматор 88 остатка интеграла, вто- рой элемент 89 задержки, второй элемент. ИЛИ 90, третий элемент И 91, четвертый элемент И 92, регистр 93

остатка интеграла, узел 94 выделения квантованных приращений.

Позициями 95 и 96 обозначены соответственно первый и второй вхо- ды решающего блока 2.

Позициями 97 и 98 обозначены соответственно первый и второй выходы решающего блока 2.

Позицией 99 обозначена группа

О входов решающего блока 2,

-15

20

30

5

25

0

S

0 5

Выход элемента НЕ 78 соединен с входом первого элемента И 79, выход которого соединен с первым входом, первого элемента ИЛИ 80, второй вход которого соединен с выходом второго элемента И 81, а выход соединен с входом узла 82 масштабирования, выход которого соединен с входом входного узла 83, выход которого соединен с первым входом сумматора 84 подынтегральной функции, второй вход которого соединен чере.з первый элемент 85 задержки с первым выходом сумматора 84 подьштегральной функции, третий вход которого соединен также с выходом первого элемента ИЛИ 80.

Второй выход сумматора 84 подынтегральной функции соединен с входом регистра 86 подынтегральной функции и с входом узла 87 умножения , выход которого соединен с первым входом сумматора 88 остатка интеграла, второй вход которого соединен через второй элемент 89 задержки с первым выходом сумматора 88 остатка интеграла, третий вход которого соединен с выходом второго элемента ИЛИ 90, первый вход которого соединен с выходом третьего элемента И 91, а второй вход - с выходом четвертого элемента И 92, первый вход которого соединен также с выходом элемента НЕ 78, а второй вход - с выходом регистра 93 остатка интеграла. Выход сумматора 88 остатка интеграла соединен с входом регистра

93остатка интеграла и с входом узла

94выделения квантованных приращений.

Первый вход 95 решающего блока 2 соединен с входом элемента НЕ 78, с первыми входами второго и третьего элементов И 81 и 91, с вторым входом узла 82 масштабирования, с вторым входом регистра 86 подынтегральной функции, с вторым входом узла 87 умножения, с вторым входом третьего

элемента И 91, с вторым входом регистра 93 остатка интеграла, и с вторым входом узла 94 вьиеления квантованных приращений.

Второй вход 96 решающего блока 2 соединен с вторым входом второго элемента И 81.

Первый выход 97 решающего блока 2 соединен с вьпсодом узла 94 выделения квантованных приращений.

Второй выход 98 решающего блока 2 соединен также с выходом первого элемента ИЛИ 80.

Один из входов группы входов 99 решающего блока 2 соединен с входом узла 87 умножения, а остальные входы этой группы входов 99 соединены с группой входов входного узла 83.

Второй вход nefiBoro элемента И 79 соединен с выходом регистра 86 подынтегральной функции.

Б состав блока 5 расчетных параметров (фиг.4) входят наборная панель too, элементы И 101, элементы ИЛИ 102.

Позицией 103 обозначен вход блока 5 расчетных параметров, а позицией

104- группа его выходов. Каждая группа выходов наборной

панели 100 соединена через соответствующую группу элементов И 101 с входа; Ш соответствующего выходного элемента ИЛИ 102.

Второй вход каждого элемента И 101 соединен с первым входом 103 блока 5 расчетных параметров.

Выход каждого элемента ИЛИ 102 соединен с соответствующим выходом группы выходов 104 блока 5 расчетньпс параметров.

В состав блока 6 ПОСТОЯННЕЛХ параметров, аналогичного по своей структуре блоку 8 граничных параметров и представленного на фиг.5, входят элементы ИЛИ 105, а позициями 106 и t07 обозначены соответственно вход блока 6 постоянных параметров и группа входов этого блока, причем грзтпа входов каждого элемента ИЛИ

105соединена с входом 106 блока 6 постоянных параметров, а вькод каждого элемента ШШ 105 соединен с со- ответствугадим выходом группы выходов 107 блока 6 постоянных параметров.

В состав блока 7 про1 раммно-иэме- няемь х параметров (фиг. 6) входят первые элементы ИЛИ 108, элементы И 109, вторые элементы ИЛИ 110, а

10

15

20

25

25767210

ПО31П1ИЯМИ 111-113 обозначены соответственно группа входов блока 7 программно-изменяемых параметров, группа выходов этого блока и вход этого блока, причем входы каждого первого элемента ИПИ 108 соединетт с выходами соответствующих элементов И 109 каждой группы этих элементов, первые входы каждого из которых соединены с выходами соответствующих вторых элементов ИЛИ 110, а вторые входы элементов И 109 каждой группы этих элементов соединены с соответствукяцим входом из группы входов 111 блока 7 программно-изменяемых параметров, выход каждого первого элемента ИЛИ 108 соединен с соответствующим выходом группы выходов 112 блока 7 программно-изменяемых параметров, группа входов каждого второго элемента ИЛИ 110 соединена с входом 113 блока 7 программно-изменяемых параметров.

В состав блока 12 образования приращений (фиг, 7) входят первый элемент И 114, первый элемент ИЛИ 115, первый регистр 116 сдвига, второй элемент И 117, первый элемент НЕ 118, третий элемент И 119, второй элемент НЕ 120, четвертый элемент И 121, первый триггер 122, первый элемент 123 задержки, пятый элемент И 124, второй элемент ИЛИ 125, первый сумматор 126, шестой элемент И 127, третий элемент НЕ 128, второй элемент 129 задержки, третий элемент ИЛИ 130, второй регистр 131 сдвига, второй сумматор 132, седьмой элемент И 133, третий элемент 134 задержки, четвертый элемент 135 задержки, восьмой элемент И 136, четвертый элемент НЕ 137, девятый элемент И 138, второй триггер 139, десятый элемент И 140, третий триг 5 ,1, одиннадцатый элемент И 142, двенадцатый элемент И 143, четвертый триггер 144, тринадцатый элемент И 145, четырнадцатый элемент И 146, четвертый элемент ИЛИ 147, пятнадца50 тьй элемент И 148.

Позициями 149 и 150 обозначены соответственно первый и второй входы блока 12 образования приращений, а позицией 151 - выход блока 12

55 образования приращений.

Выход первого элемента И 114 со- единен с входом первого элемента ИЛИ 115 выход которого соединен с пер30

35

40

вым входом первого регистра 116 сдвига, выход которого соединен с входом второго элемента И 117, второй вход которого соединен с выходом первого элемента НЕ 118, а выход соединен с вторым входом элемента ИЛИ 115.

Выход регистра 116 сдвига соединен также с входом третьего элемента И 119, выход которого соединен с входом второго элемента НЕ 120 и с входом.четвертого элемента И 121, второй вход которого соединен с нулевым выходом первого триггера 122, единичньй вход которого соединен с выходом первого элемента 123 задержки, а единичный выход соединен с входом пятого элемента И 124, второй вход которого соединен с выходом второго элемента НЕ 120.

Выход четвертого элемента И 121 соединен с входом первого элемента 123 задержки и с входом второго элемента ИЛИ 125, второй вход которого соединен с выходом пятого элемента И 124.

Выход элемента ИЛИ 125 соединен с первым входом первого сумматора 126, второй вход которого соединен также с выходом первого элемента И 114, а первый выход соединен с входом шестого элемента И 127, второй вход которого соединен с выходом третьего элемента НЕ 128, а выход соединен с входом второго элемента 129 задержки, выход которого соединен с третьим входом первого сумматора 126.

Второй выход первого сумматора 12 соединен с входом третьего элемента ИЛИ 130, выход которого соединен с входом второго регистра 131 сдвига, выход которого соединен с первым входом второго сумматора 132, первый выход которого соединен с входом

седьмого элемента И 133, второй вход 5 надцатого 143 элементов И и второй

которого соединен с выходом третьего элемента НЕ 128, а выход соединен с входом третьего элемента 134 задержки

Второй вход второго сумматора 132 соединен с выходом третьего элемента 134 задержки, а второй выход этого сумматора соединен с вторым входом третьего элемента ИЛИ 130.

Выход третьего элемента ИЛИ 130 соединен также с входом четвертого элемента 135 задержки, выход которого соединен с входом восьмого элемента И 136 и с входом четвертого

35

10

20

5767212

элемента НЕ 137, выход которого соединен с входом девятого элемента И 138, выход которого соединен с нулевым входом второго триггера 139, единичный вход которого соединен с выходом восьмого элемента И 136.

Выход четвертого элемента 135 задержки соединен также с входом десятого элемента И 140, выход которого соединен с единичным входом третьего триггера 141, единичный и нулевой выходы которого соединены соответственно с входом одиннадцатого элемента И 142 и с входом двенадцатого эле- 15 мента И 143, выходы которых соединены соответственно с единичным и нулевым входа1-и четвертого триггера 144, единичный выход которого соединен с первым входом тринадцатого элемента И 145 и с первым входом четырнадцатого элемента И 146, вторые входы которых соединены соответственно с единичным и нулевым выходами второго триггера 139.

Выход тринадцатого элемента И 145 соединен с входом пятнадцатого элемента И 148, выход которого соединен с входом четвертого элемента ИЛИ 147, BTopoiJ вход которого соединен с выходом четырнадцатого элемента И 146, а выход соединен с третьим входом второго сумматфра 132..

Первый вход первого элемента И 114, второй вход первого регистра Мб сдвига, вход первого элемента НЕ 118, второй вход третьего элемента И 119, нулевой вход первого триггера 122, вход третьего .элемента НЕ 128, второй вход второго регистра 131 сдвига, второй вход восьмого элемента И 136, второй вход девятого элемента И 138, второй вход десятого элемента И 140, нулевой вход третьего триггера 141, вторые входы одиннадцатого 142.и две25

30

40

вход пятнадт атого элемента И 147 соединены с первым входом 149 блока образования приращений.

Второй вход первого элемента И 1 14 соединен с вторым входом 150 блока образования приращений.

Выход тринадцатого элемента И 145 и выход четьгрнадцатого элемента И 146 соединены с выходом 151 блока образования приращений.

В состав первого блока 4 коммутаций, представленного на фиг. 8, входят п элементов ИЛИ 152, п групп

13

элементов И 153 и п групп элементов И 15/4, причем первая группа входов каждого элемента ШШ 152 соединена с выходами соответствующей группы элементов И 153 из п групп этих элементов, а вторая группа входов каждого элемента ИПИ 152 соединена с выходами соответствующей группы элементов И 154 из п групп этих элементов, первые входы каждого элемента И 153 каждой из п групп этих элементов соединены с соответствующими входами из первой группы входов 155 блока 4 коммутации, а вторые входы калддого элемента И 153 каждой из п групп этих элементов и первые входы каждого элемента И 154 каждой из п групп этих элементов соединены с соответствующими Ьходами из второй группы входов 156 блока 4 коммутации, вторые входы каисдого элемента И 154 каждой из п групп этих элементов соединены с соответствующими входами из третьей группы входов .157 блока 4 коммутации, выходы элементов ИПИ 152 соединены с соответствующими выходами соответствукадих групп выходов 158 блока 4 коммутации В состав второго блока 13 коммутации (фиг. 9) входят п групп элементов И 159, первая группа элементов ИЛИ 160, п грзппп элементов И 161, вторая группа элементов ИЛИ 162, причем выходы каждой группы элементов И 159 из п групп этих элементов соединены с.соответствующими входами соответствующих элементов ИЛИ 160, а выходы каждой группы, элементов И 161. из п групп этих элементов соединены с соответствующими входами соот ветствующих элементов ИЛИ 162, первые входы каждой группы элементов И 159 из п групп этих зле ментов и первые входы каждой группы элементов И 161 из п групп этих элементов соеди- иены с соответствуюдим входом из первой группы входов 163 блока 13 коммутации, в.торые входы каждой группы элементов И 159 из п групп этих элементов соединены с соответствующими входами из второй группы входов 164 блока 13 коммутации, вторые входы i каждой группы элементов И 161 из п групп этих элементов соединены с со- ответству7ощими входами из третьей группы входов 165 блока 13 коммутации, выходы второй 1-руппы элементов ИЛИ 162 соединены с первой группой

10

is

20

25

4045sO

5767214

выходов 166 блока 13 коммутации, а выходы первой группы элементов ИЛИ 160 соединены с второй группой выходов 167 блока 13 коммутации. 5 В состав аналогичных по своей структуре блоков 14-18 коммутации (фиг. 10) входят II групп элементов И 168 и группа элементов ИЛИ 169, причем выходы каждой группы элементов И 168 из п групп этих элементов соединены с соответствующими, входами соответствующих элементов ИЛИ 169 группы, первые входы каждой группы элементов И 168 из п групп этих ментов соединены с соответствующим входом из первой группы входов 170 блоков 14-18 комз утации, а вторые входы каждой группы элементов И 168 из п групп этих элементов соединены с соответствующими входами из второй группы входов 171 блоков 14-18 коммутации, выходы группы элементов ИЛИ 169 соединены с группой выходов 172 блоков 14-18 коммутации.

В состав блока 3 вывода (фиг. 11) входят неполный дешифратор 173, эле мент 174 задержки, элемент НЕ 175, элемент И 176, элемент ИЛИ 177, группа триггеров 178, группа элементов 179 задержки, группа элементов И 180, п групп элементов И 181, п групп - триггеров 182, первая группа дешифраторов 183, вторая группа дешифраторов 184, узел 185 индикации, узел 186 звуковой сигнализации, причем выход неполного дешифратора 173 соединен с входом элемента 174 задержки и с входом элемента НЕ 175, выход элемента 174 задержки и выход элемента НЕ 175 соединены с входами элемента И 176, выход которого соединен с первым входом элемента ИЛИ 177, выход которого соединен с нулевыми входами триггеров 178 группы, нулевой выход каж- догл триггера 178 из группы этих триггеров соединен с входом соответствующего элемента 1-79 задержки из группы этих элементов, выход каждого из которых соединен с первым входом соответствующего элемента И 180 из группы этих элементов, выход каждого элемента И ISO из группы этих элементов соединен с первыми входами соответствующей группы элементов И 181 из п групп этих элементов, выходы каждой группы элементов И 181 из п групп этих элементов соединены с единичными входами соответствующей

30

35

55

15

группы триггеров 182 из п групп этих триггеров, а нулевые входы каждой группы триггеров 182 из п групп этих триггеров соединены с выходом элемента ШШ 177, единичные выходы каждой группы триггеров 182 из п групп этих триггеров соединены с

входами соответствукщих дешифраторов 183 первой группы дешифраторов, выходы второй группы дешифраторов 184 соединены с первой группой входов узла 185 индикации, вторая группа входов которого соединена с выходами первой группы дешифраторов 183, третья группа входов узла 185 индика дии соединена с единичными выходами группы триггеров 178, единичный выход каждого триггера 178 группы триггеров соединен также с вторым входом соответствующего элемента И 180 из группы этих элементов и с соответствующим входом из группы входов узла 186 звуковой сигнализации, вход 187 блока 3 вывода соединен с вторым входом Элемента ИЛИ 177, с группой вхо дов неполного дешифратора 183 и с вторыми входами каждой группы элементов И 181 из п групп этих элементов, группа входов каждого дешифратора 184 второй группы дешифраторов соединена с соответствующими входами из первой группы входов 188 блока 3 вывода, а единичный вход каждого триггера 178 группы триггеров соединен с соответствующим входом из второй группы входов 189 блока 3 вывода

Интегрирующая вычислительная структура работает следующим образом

После включения источника питания интегрирующей структуры генератор 26 тактовых импульсов блока 1 управления начинает выдавать тактирующие импульсы, которые поступают на управляющий вход сдвигающего регистра 36 и осуществляют сдвиг той случайной информации, которая была записана в регистр 36 при включении источника питания, а так как на входы элемента И 37 поступают сигналы с нулевых выходов четных разрядов сдвигающего регистра 36 за исключением последнего разряда, то пока не произойдет обнуление регистра 36, на выходе элемента И 37 сигнал будет отсутствовать. И лишь после обнуления регистра 36 на выходе элемента И 37 появляется сигнал, который поступает на информационный вход сдвигающего регистра 36

1

- .

.

20

25

25767216

и в первый разряд этого регистра записывается единица.

В следующем такте подачей такти- рлтощих сигналов с выхода генератора i 5 26 эта единица сдвигается во второй разряд регистра 36, а в первый разряд записывается новая единица. Сигналы с единичных вьгкодов регистра 36 поступают на входы группы элементов О И 35, состоящей из двухвходовых элементов И, на входы которых поступают сигналы с единичных выходов соседних разрядов регистра 36, а на выходах образуются распределенные времен- 15 ные импульсы, причем при записи единицы во второй разряд регистра 36 н.э одном из входов элемента И 37 появляется нулевой сигнал, который закрывает этот элемент и прохождение сигнала на информационный вход регистра 36 прекращается. Записанный в регистр 36 сигнал, представляющий собой две единицы в соседних разрядах, сдвигается до последнего разряда и производит выработку распределенных временных импульсов. После того, как записанный в регистр 36 сигнал сдвинется в последние два разряда, элемент И 37 открывается и в следующем такте в первый разряд регистра 36 записьшается новая единица, а единица из предпоследнего разряда записывается в последний и на выходе соответствующего элемента

35 И группы этих элементов 35, входы которого подключены к единичным входам последнего и первого разрядов регистра 36, появляется последний временной импульс, а в следующем

40 такте единицы записываются уже в первый и второй разряды регистра 36 и выработка распределенных временных импульсов начинается заново уже в новом цикле. Распределенные вре45 менные импульсы с выходов группы элементов И 35 распределителя 30 поступают в каждом цикле в узел 29 на единичные и нулевые входы триггеров и производят выработку управляющих

50 потенциалов требуемой длительности, которые с выходов узла 29 триггеров также, как и распределенные временные импульсы с выходов группы элемен тов И 35 распределителя 30, поступа55 ют в соответствующие блоки интегрирующей вычислительной структуры для обеспечения организации выполнения различных режимов работы этих блоков.

30

17

Затем подачей сигнала с второго выхода пульта 23 упраЕленил 23 блока 1 производятся установка ИВС в исходное состояние, причем подачей этого сигнала через выход 69 блока 1 в каждый решающий блок 2 на его вход 95 производится установка в исходное состояние узла 82 масштабирования, регистра 86 подынтегральной функции и рег истра 93 остатка интеграла каждого решающего блока 2, подачей же этого сигнала с второго выхода пульта 23 через выход,74 блока 1 сброс производится установка в исходное состояние блока 11 памяти, подачей этого сигнала с второго выхода пульта 23 через выход, 75 блока 1 на вход 149 блоков 12 образования приращений устана)ливаются в исходное состояние регистры 116 и 131, . подачей этого сигнала через выход 72 блока 1 устанавливается в нулевое состояние счетчик 9 текущего времени, а подачей этого сигнала через выход 70 блока 1 на вход 187 блока 3 вывода устанавливаются в нулевое состояние триггеры 178 группы и триггеры. 182 п групп этих триггеров. Кроме того, сигнал с второго выхода пульта 23, пройдя через элемент РШИ 41, устанавливает в исходное состояние триггер 38, пройдя через элемен ШШ 45, устанавливает в нулевое состояние триггер 42, пройдя через элемент И 47, устанавливает в нулевое состояние триггер 49, пройдя через элемент ИЛИ 55, устанавливает в нулевое состояние триггер 52, пройдя через элемент ИЛИ 56, устанавливает

12

нулевое состояние триггер 57, прой-40 тегрирования соответствующих решающих

дя через элемент ИЛИ 64, устанавливает в нулевое состояние триггер 61, пройдя через элемент ИЛИ 68, устанавливает в нулевое состояние триггер 65, а также сигнал с второго выхода пульта 23, устанавливает в нулевое состояние триггер 46 и счетчики 27 .и 28, Обнуление триггеров 122, 139, 141 и 144 блока 12 осуществляется временными импульсами, вырабатывае- Ь5ыми распределителем 30 сразу после включения источника питания ИВС.

Затем на пульте 23 управления нажимается клавиша, определяющая программу коммута1щи выбираемой задачи и соответствующий сигнал через соот- ветствуюшкй выход из группы выходов 76 блока 1 поступает в блок 4 коммут25767218

тации на соотвстствуюн1Ий вход из группы входов 156, в блок 13 коммутации - на соответствующий вход из группы входов 163, в блоки 14-18

5 коммутации - на соответствующий вход из группы входов 170 и обеспечивает коммутацию решающих блоков 2 между собой и с другими блоками ИВС в соответствии с решаемой задачей. При

О этом блок 4 коммутации по этому сигна лу обеспечивает в соответствии со структурной схемой решаемой задачи . соединения решающих блоков 2 между собой и с блоками 12 образования при 5 ращений (т.е. соединение выходов 97 решакяцих блоков 2 через соответствующие входы из группы входов 155 -блока 4 коммутации, через соответствующие элементы И 153 соответствующих групп из п групп этих элементов, открытие этим сигналом из блока 1 управления, через соответствующие элементы ИЛИ 152 и соответствующие выходы из групп выходов 158 с соответствующими входа- 99 приращений подынтегральной функции и переменной интегр ирования соответствующих решающих блоков 2, а также соединение выходов 151 соответствующих блоков 12 образования прира30 П1ений через соответствующие входы из групп входов 137 блока 4 коммутации, через соответствуюш 1е элементы И 154 соответствующих групп из п групп этих элементов, открытые этим сигналом

35 ИЗ блока 1 через соответствующие элементы ИЛИ 152 и соответствующие выходы из групп выходов 158 с соответствующими входами 99 приращений подынтегральной функции и переменной ин20

25

блоков 2). Блок 13 коммутации обеспечивает по этому сигналу из блока 1 подключение в соответствии с решаемой задачей входов и выходов соответствую ющи}; регистров блока 11 памяти через соответствующие выходы 166 и соответственно через соответствующее входы 164 блока 13 коммутации, через соот- ветствуюш:ие элементы ИЛИ 162 группу открыться этим сигналом элементов И 161, соответствующие входы 165 и соответственно через соответствующую группу открытых этим сигналом элементов И.159, соответствующие элементы HIM 160, соответствующие выходы 167 и соответствуилцие элементы ИЛИ 22 к выходам 98 и соответственно к входам 96 соответствующих решающих блоков 2,

в рег истры 86 подынтегральных функций которых заносятся расчетные ве- личинь, нагфимер для уравнений динамики, это в основном первые и вторые производные скорости, высоты и т.п.). Блок 14 коммутации обеспечивает по этому сигналу из блока 1 подключение в соответствии с решаемой задачей соответствующих выходов 107 блока 6 по172 блока 14 и через соответствующие элементы ИЛИ 22 с вторыми входами 96 соответств тащих решающих блоков 2, в регистры 86 подынтегральных функций которых в соответствии с решаемой

устанавливается время реального процесса, с момента которого начинается решение данной задачи, и на наборной

стоянных параметров через соответст- 0 того, при подготовке задачи к реше- вующие входы 171 блока 14 коммутации, нию на пульте 23 управления блока 1 соответствующую группу открытых элементов И 168, соответствующие элементы ИЛИ 169, соответствующие выходы

15 панели 100 блока 5 устанавливаются рассчитанные для этой точки времени значения расчетных параметров решаемой задачи.

После проведения подготовки ИВС к задачей заносятся постоянные величины 20 решению по сигналу Пуск с пульта (например, радиус Земли, угловая ско- управления начинается реальный прорость вращения Земли и т.п.). Блок цесс (например движение самолета) и 15 коммутации, аналогичный по своей структуре блоку 14 коммутации, обеспечивает по этому сигналу из блока 1 подключение в соответствии с решаемой задачей соответствующих выходов 112 блока 7 программно-изменяемых

одновременно этот сигнал с первого выхода пульта 23 поступает на вход . 25 элемента И 25, разрешая подачу тактирующих импульсов с выхода генератора 26 через выход 72 блока 1 в счет чик 9 текущего времени, и на вход узла 24 сравнения, разрешая сравнение значения момента времени, установленного на пульте 23, cd значением счетчика 9, который.по сигналам с генератора 26 подсчитывает время реального процесса. Когда значение те параметров через соответствующие элементы ИЛИ 22 к вторым входам 96 со- ответствующих решающих блоков 2, в регистры 86 подынтегральных функций которых в соответствии с решаемой задачей заносятся величины, програм

но-изменяемые в процессе регаения за- 35 кущего времени реального процесса

дачи по прохождению определенного времени решения (например, вес самолета и т.п.). Блок 18 коммутации, также аналогичный по своей структуре блоку 14 коммутации, обеспечивает подключение в соответствии с решаемой задачей соответствуищих датчиков 21 управляемых параметров через соответствующие элементы ИЛИ 22 к вторым входам 96 соответствующих решающих блоков 2, в регистры 86 подынтегральных функций которых в соответствии с решаемой задачей заносятся переменные величины, отражающие течение реального процесса (например, угол крена, угол тангажа, угол рыскания, скорость, высота полета и т.д.). Блоки 16 и 17 коммутации, также аналогичные по своей структуре блоку 14 коммутации, обеспечивают по этому сигналу из блока 1 управления подключение к входам блока 10 сравнения в соответствии с решаемой задачей

выходов 98 соответствукицих решающих блоков 2, в регистрах 86 которых вычисляются контролируемые параметры (например, высота полета, величины нормальных перегрузок по осям самолета и т.п.), и соответствующих выходов блока 8 граничных параметров, который выдает предельные значения контролируемых параметров. Кроме

устанавливается время реального процесса, с момента которого начинается решение данной задачи, и на наборной

того, при подготовке задачи к реше- нию на пульте 23 управления блока 1

После проведения подготовки ИВС к решению по сигналу Пуск с пульта управления начинается реальный процесс (например движение самолета) и

одновременно этот сигнал с первого выхода пульта 23 поступает на вход . элемента И 25, разрешая подачу тактирующих импульсов с выхода генератора 26 через выход 72 блока 1 в счетчик 9 текущего времени, и на вход узла 24 сравнения, разрешая сравнение значения момента времени, установленного на пульте 23, cd значением счетчика 9, который.по сигналам с генератора 26 подсчитывает время реального процесса. Когда значение те достигнет значения времени, установленного на пульте 23, тогда узел 24 сравнения выдает сигнал равенства в узел 31 выработки потенциала ввода на единичный вход триггера 38. Триггер 38 переходит в единичное состояние и открывает элемент И 39, разрешая тем самым прохождение первого временного импульса из распределителя 30 с первого выхода узла 35 на единич НЕ)й вход триггера 42 и через элемент 40 задержки и элемент ИЛИ 41 на нулевой вход триггера 38. В результате этот импульс устанавливает триггер 42 в единичное состояние, а задержавшись на такт на элемента 40 задержки, устанавливает в нулевое состояние триггер 38. Триггер 42 начинает выдавать через шестой выход 74 блока 1 в блок 11 памяти потенциал ввода длительностью одной итерации, по которому в соответствующие регистры блока 11 заносятся из блока 5 с соответствугощтс ныходов элементов ИШ 102 через выходы 104 расчетные величи -гы в последовательном коде. При этом перевод параллельных кодов, набранных на панели 100, в последовательные производится подачей соответствующих време.нных импульсов через вход 103 на вторые входы соответствующих, элементов И 101, и, клапанируя таким образом первые младшие разряды первым временным импульсом, вторые разряды - BTopbfM временным импульсом и т.д., на выходе ИЛ1 102 получается поспедовательный код. Последний временной импульс, соответствующий концу итерации, поступает через открытый элемент И 43 и, задержавшись на один такт на элементе 44 задержки, проходит через элемент ИЛИ 45 и устанавливает в нулевое состояние триггер 42, завершив тем самым выработку потенциала ввода. На этом ввод расчетных величин из блока 5 в блок 11 памяти заканчивается.

Одновременно последний временной импульс, прошедший через элемент И 43 и задержанный на один такт на элементе 44. задержки, поступает в узел 32 пуска-останова на единичный вход триггера 49 и в узел 33 выработки потенциала записи исходных данных через элемент ИЛИ 51 на единичный вхбд триггера 52,

В ре;зультате триггер 49 переходит в единггчное состояние и начинает выдавать сигнал, разрешающий решение через первый выход 69 блока 1 и через первый вход 95 каждого решающего блока 2 на входы узла 82 масштабирования, узла 87 умножения, узла 94 выделения приращений и регистров 86 и 93 каждого решающего блока 2, разрешая тем сам.ьгм выполнение процесса вычислений. Одновременно в единичное

to

15

20

блока I решаемой задачей с соответствующих выходов блоков 6, 7 и 11 и датчиков 21 через соответствующие блоки 13, 14, 15 и 18 коммутации, 5 через соответствующие элементы ИЛИ 22, через входы 96 соответствукщих решающих блоков 2 и через открытые элементы И 81 и ИЛИ 80 на входы сумматоров 84 и узлов 82 масштабирования этих решающих блоков 2. При этом в решаю111 1е блоки 2, подынтегральные функции которых в соответствии с решаемой задачей являются постоянными величинами, поступают значения в последовательном модифицированном дополнительном двоичном коде из блока 6 через выхода 107 с выходов соответствующих элементов ИЛИ 105, на входы которых через вход 106 блока 6 подаются соответствующие этим кодам комбинации временных импульсов из блока 1 через выход 71 с четвертого выхода узла 35 элементов И, В решающие блоки 2, подынтегральные функции которых в соответствии с решаемой задачей являются программно-изменяемыми величинами, поступают значения в последовательно модифицированном дополнительном коде из блока 7 через выходы 112 с выходов соответствугацих элементов ИЛИ 108, на соответствующий вход каждого из которых через соответст- вукящй элемент И 109 с выхода соответствующего элемента ИЛИ 110 подаются соответствующие этим кодам комбинации временных импульсов, поступающих на входы элементов ИЛИ 110 через вход 113 из блока 1, через вы- ход 71 с четвертого выхода узла 35 элементов И. В решающие блоки 2, f подьштегральные функции которых в соответствии с решаемой задачей являются расчетными величинами, посту25

30

35

40

из соответствумцих регистров блока 11 памяти, сдвигаемые по поступающему из блока 1 через выход 74 в блок

состояние переходит и триггер 52, ко- паю- гначения в последовательном моторый начинает выдавать потенциалдифицированном дополнительном коде записи исходных данных длительностью одной итерации через выход 74 в блок

11памяти, через выход 75 - в блок

12образования прир.ащений и через вы-501 1 потенциалу записи исходных данных ход 69 блока 1 - в каждый решающийВ решаюпще блоки 2, подынтегральные блок 2 на входы элемента И 81, эле-функции которых в соответствии с ре- мента И 91 и элемента НЕ 78.шаемой задачей являются управляемыми

В результате элементы И 81 и 91параметрами, поступают значения из

о.ткрьтаются, а элементы Ц 79 к 92 за-55датчиков 21,

крываются и начальные значения подын- Одновременно по потенциалу запитегральных функций поступают в соот-си исходных данных, поступающему

ветствии с выбранной на пульте 23из блока 1 с выхода триггера 52, в

блока I решаемой задачей с соответствующих выходов блоков 6, 7 и 11 и датчиков 21 через соответствующие блоки 13, 14, 15 и 18 коммутации, через соответствующие элементы ИЛИ 22, через входы 96 соответствукщих решающих блоков 2 и через открытые элементы И 81 и ИЛИ 80 на входы сумматоров 84 и узлов 82 масштабирования этих решающих блоков 2. При этом в решаю111 1е блоки 2, подынтегральные функции которых в соответствии с решаемой задачей являются постоянными величинами, поступают значения в последовательном модифицированном дополнительном двоичном коде из блока 6 через выхода 107 с выходов соответствующих элементов ИЛИ 105, на входы которых через вход 106 блока 6 подаются соответствующие этим кодам комбинации временных импульсов из блока 1 через выход 71 с четвертого выхода узла 35 элементов И, В решающие блоки 2, подынтегральные функции которых в соответствии с решаемой задачей являются программно-изменяемыми величинами, поступают значения в последовательно модифицированном дополнительном коде из блока 7 через выходы 112 с выходов соответствугацих элементов ИЛИ 108, на соответствующий вход каждого из которых через соответст- вукящй элемент И 109 с выхода соответствующего элемента ИЛИ 110 подаются соответствующие этим кодам комбинации временных импульсов, поступающих на входы элементов ИЛИ 110 через вход 113 из блока 1, через вы- ход 71 с четвертого выхода узла 35 элементов И. В решающие блоки 2, f подьштегральные функции которых в соответствии с решаемой задачей являются расчетными величинами, посту

паю- гначения в последовательном моиз соответствумцих регистров блока 11 памяти, сдвигаемые по поступающему из блока 1 через выход 74 в блок

дифицированном дополнительном коде

каждый решающий 6jroK 2 через откры- тьй элемент И 91 и элемент ИЛИ 90 на вход сумматора 88 поступает временной импульс, соответствующий значению 0,5. Так как одновременно в каждый решающий блок .2 поступает сигнал разрешающий решение, то в решающих блоках начинается процесс вычислений на первой итерации. При этом в каждом решающем блоке 2 первая же единица в коде подынтегральной функции, являющаяся начальным импульсом и поступающая через открытый элемент И 81 и элемент ИЛИ 80, поступает в узел 82 масштабирования и вырабаты- вает масштабный импульс, соответст- вукхций кванту подынтегральной функции, который поступает в входной узел 83 и приводит сумму входных приращений подынтегральных функций, поступающих из блока 4 коммутации i через входы 99, к масштабу подынтегральной функции данного решающего блока 2, С выхода узла 83 эта сумма приращений подынтегральной функции поступает на вход сумматора 84, на второй вход которого поступает по входу 96 через элементы И 81 и ИЛИ 80 Начальное значение подынтегральной функции. Получившееся в резуль- тате суммирования на сумматоре 84 новое значение подынтегральной функции поступает в регистр 86 и на вход узла 87 умножения, где происходит умножение этого значения подынтег- ральной функции на приращение переменной интегрирования, поступающее и из блока 4 через вход 99. Результат умножения поступает на вход сумматор 88 остатка интеграла, на второй вход которого поступает временным импульсом, соответствующим значению 0,5, через элементы И 91 и ИЛИ 90 начальное значение остатка интеграла. Полу ченное в результате суммирования но- вое значение остатка интеграла и приращения интеграла поступают соответственно в регистр 93 остатка интеграла и в узел 94, где происходит вьзделение квантованных приращений интеграла на выход 97 решающего блока 2. На этом процесс вычислений на первой итерации заканчивается. При этом по окончании первой итерации последний временной импульс проходит с второго выхода узла 35 через открытый элемент И 53 и, задержавшись на один такт на элементе 54 задержки.

проходит через элемент ИЛИ 55 и устанавливает в нулевое состояние триггер 52, завершив тем самым выработку потенциала записи исходных

данных. В результате по окончаний первой итерации элементы И 8Т и 91 каждого решающего блока 2 закрываются, так как на единичном выходе триггера 52 имеется нулевой потенциал, а элементы И 79 и И 92 каждого решающего блока 2 открываются и во второй итерации значения подынтегральной функции и остатка интеграла, вычисленные на первой итерации, по

ступают соответственно с выходов регистров 86 и 93 через соответствующие открытые элементы И 79 и И 92 и через соответствующие элементы ИЛИ 80 и 90 соответственно на вход сумматора 84 и сумматора 88, а значение подынтегральной функции с выхода элемента ИЛИ 80 поступает еще и в узел 82 масштабирования для выработки масштабного импульса во второй итерации. Так как в то же время триггер 49 продолжает находиться в единичном состоянии и выдавать в каждый решающий блок 2 сигнал, разрешающий решение, то начинаются вычисления на второй итерации. При этом одноразрядные приращения интегралов с вы ходов 97 каждого решающего блока и одноразрядные приращения с выходов блоков 12 поступают через блок 4 коммутации в соответствии со структурной схемой решения задачи на входы 99 соотВетствукяцих решающих блоков 2 и в этих решающих блоках, так же как и в первой итерации, происходят вычисления, при этом получают новые значения подынтегральных функций, остатка интеграла и приращения интеграла уже во второй итерации.

Образование одноразрядных приращений в блоках 12 происходит следующим образом.

По потенциалу записи исходных данных, поступающему в первой итерации из узла 33 с единичного выхода триггера 52 через выход 75 блока 1 через вход 149 блока 12 на вход элемента И 114, с соответствующего датчика 20 через открытый элемент И 114 в каждом блоке 12 снимается значение соответствующего управляющего воздействия в последовательном двоичном коде, которьп с выхода элемента И 114 проходит через элемент ИЛИ 115

и в течение первой итерации записывается в регистр 116 (элемент И 117 в течение первой итерации закрыт ин-- версным сигналом потенциатга записи исходных данкьтх, поступакхцего через элемент НЕ .118 через вход 149 из узла 33 блока 1). Одновремершо значение уггравляющего воздействия поступает с выхода элемента И 114 на вход

сумь5атора 126, на второй вход которо- О который в течение второй итерации

го с выхода элемента ИЛИ 125 поступает нулевой сигнал, так как с выхода регистра 116 вследствие предварительного обнуления в течение первой итерации поступает нулевой сигнал, который проходит на выход элемента ИЛИ 125 через открытые элементы И 119 (на второй вход этого элемента в течение первой ,ии подается потенциал записи исходных данных) и открытый элемент И 121 (на второй вход этого, элемента подается единич- ньй сигнал с нулевого выхода триггер 122, который устанавливается в нулевое состояние первым временным импульсом, соответствующим началу итерации), В результате значение управляющего воздействия щ)оходит через сумматор 126 без изменений и, пройдя через элемент ЙШ1 130,, в течение пер вой итерации заносится в регистр 131 Одновременно это значение с выхода элемента ИЛИ 130 поступает на вход элемента 135 задержки и, задержавшис на один такт, поступает через откры- тьй элемент И 140 (на второй вход этого элемента И подается из блока 1 через выход 75 с второго выхода узла 29 триггеров разрешающий потенци- ап,, выделяющий числовые разряды, исключая знаковые) на единичный вход триггера 141, который анализирует модуль числа и в случае,, если поступающая с выхода элемента ИЖ /130 величина не равна нулю, триггер t4t устанавливается в единичное состояние, а по последнему временному импульсу, соответствукядему конду итерации и поступающему на входы элементов И 14.2 и 143 из блока 1 с пя- того выхода узла 35, это состояние. трИ1 гера 141 перезаписывается в триг гер .144. По первому временному импульсу, соответствующему началу сле- дуи.щей. итерации я поступакяцему на входы элементов И 136 и 138 из блока 1 с пятого выхода узла 35s триггер 139 производит анализ знака величины

поступающей с лыхода элеък-нта 133 задержки. В результате, если знак оказывается положительным и значение поступающей неличины равно нулю, то триггер 139 находится в нулевом состоянии, а триггер 144 - в единичном состоянии и на выходе элемента И 146 появляется единичный сигнал, соответствующий положительному приращению,

20

35 50

поступает через выход 151 .блока 12 и через блок 4 в соответствии со структурной схемой решаемой задачи на со- ответствукадие входы 99 соответст- 5 вующих рещающих блоков 2. Если же знак поступающей величины оказывается отрицательным и значение ее не равно нулю, то триггеры 139 и 144 находятся в единичном состоянии и на выходе элемента И 145 появляется единичньм сигнал, соответствующий отрицательному приращению, который в течение второй итерации поступает через выход 151 блока 12 и через блок 4 на соответствующие входы 99 соответствующих решающих блоков 2. Одновременно инверсное значение приращения (т.е. если приращение положительное, то оно проходит с выхода 30 элемента И 146 через элемент ИЛИ 147 в виде потенциала, соответствующего

дополнительному коду отрицательного приращения, а если приращение отрицательное то, проклапанировавшись первым временньм импульсом на элементе И 148, оно проходит через элемент ИЛИ 147 в виде одиночного импульса, соответствующего дoпoлнитeльнo ry коду положительного приращения) поступает во второй итерации с выхода элемента ИЛИ 148 на вход сумматора 132 и вычитается из значения управляющего воздействия, поступающего во второй итерации на второй вход сумматора 132..С выхода регистра 131. При этом элемент 134 задержки обеспечивает задержку на один такт возникающего поразрядного переноса, а инверсные значения последнего временного импульса, поступающего с выхода элемента НЕ 128 на вход элемента И 133, запрещают подачу переноса за знаковые разряды, возникающего при суммирова- тт отрицательных чисел, в младший разряд следукядего числа. Получающееся на выходе сумматора 132 во второй итерации новое значение управляющет о воздействия (уменьшенное на едини40

45

55

271257672

по сравнению с предыдущим) проит через элемент ИЛИ 130 и Б теие второй итерации заносится в обождающийся регистр 131, а таканализируется триггерами 139, з и 144, и в случае, если оно не но нулю, в начале следующей (т.е. тьей) итерации на выходе соответующего элемента И 146 или И 147 вляется сигнал, соответствующий Ю ожительному или отрицательному ращению. Таким образом, в течение

м

з с в с и вр и чи

ну сч р ед ст хо дл то то вр зн ко ра че ще вр зн вр ны ме мо ко ци бл зо в 28 в ки ре тр хо та И ет си 57 тр

счетчик 28

дулю 2. В течение 2

2 (где m - число разрядов в регистре 131, исключая знаковые) итераций значение управляющего воздействия, поступившее в первой итерации, полностью раскладывается в поток од- норазряднь х приращений. Подсчет итераций производится в блоке 1 счетчиком 28 итераций, на суммирующий вход которого по сигналу, разрешающему решение и поступающему из узла 32 с выхода триггера 49, поступает с начала момента решения в казвдой итерации первый временной импульс с первого выхода узла 35. При этом

является счетчиком по мо- итераций значение управляющего воздействия полностью разворачивается в поток одно- разрядных приращений, и таким образом, иве полностью обрабатывает поступившую в момент времени t, входную информацию, и если бы liBC работала в реальном масштабе времени, то 2 ите раций она бы выполнила за время 1)9, t,-t, , а в следующей итерации () уже обрабатьгоала бы поступившую в момент времени t новую входную информацию второго шага интегри- рования. Но для обеспечения вычислений с прогнозированием результата на период Т предлагаемая НЕС обрабатывает входную информацию за время с (т.е. за это время иве выполняет один шаг интегрирования, состоящий из 2 итераций), а за оставшееся время до момента t, т.е. за время од, п, ,

нулевое состояние и выдает сигнал в счетчик 27 шагов интегрирования, пе ребрасывая его в состояние, равное единице. Одновременно этот сигнал п ступает в блок 10 сравнения через r ход 73 блока 1 и в узел 34 блока 1 для выработки потенциала записи это точки решения. Этот потенциал запис точки решения обеспечивает в момент времени t, + запись вычисленных значений подынтегральных функций, которые в решаемой задаче являются расчетными, в блоке 11 памяти в качестве начальных значений для след. щего шага интегрирования в момент времени t , так как они соответству значению этих величин в этот момент времени. Начальные значения остальных подынтегральных функций для момента времени t снимаются в этот момент времени с датчиков 21 и с бл ков 6 и 7. При этом выработка потен циала записи точки решения узлом 34 блока 1 производится следующим обра зом. После отсчета 2 итераций, т.е в момент времени (t, + ь ), счетчик 28 выдает сигнал, который поступает в блок 34 на вход элемента 58 задер ки и, задержавшись на один такт, пе ребрасывает в единичное состояние триггер 57. Единичный сигнал с выхода триггера 57 в течение одного такта проходит через открытьй элеме И 59 (элемент 60 задержки обеспечив ет задержку на один такт единичного сигнала с нулевого выхода триггера 57) и поступает на единичный вход триггера 61. В результате триггер 6

производит прогнозирование на период

Т, (т.е. вьтолняет (T/ fp, ) шагов ий- 50 перебрасывается в единичное состоя- тегрирования). Таким образом, за период времени tg,, предлагаемая ИВС Т

выполняет (;j-ч- 1) шагов интегрировачия и следовательно работает в 55

Т . ( 1) быстрее реального вре вхмени.

ние и открывает элемент И 62. Тогда

первый временной импульс,соответствующий началу следующей итерации, проходит через этот элемент И 62 и перебрасывает в единичное состояние триггер 65, а задержавшись на один такт на элементе 63 задержки, проходит через элемент ИЛИ 64 и устанав

2

28

В результате после .обработки за 2 итераций входно информации в момент времени (t.

) вьпшсленные

значения подынтегральных функций соответствуют значению этих величин в момент времени с. реального процесса, т.е. к началу следующего шага интегрирования в реальном мйсштабе времени. Поэтому после отсчета 2 итераций счетчик 28, являющийся счетчиком по модулю 2, сбрасывается в

нулевое состояние и выдает сигнал в счетчик 27 шагов интегрирования, перебрасывая его в состояние, равное единице. Одновременно этот сигнал поступает в блок 10 сравнения через ri.j- ход 73 блока 1 и в узел 34 блока 1 для выработки потенциала записи этой точки решения. Этот потенциал записи точки решения обеспечивает в момент времени t, + запись вычисленных значений подынтегральных функций, которые в решаемой задаче являются расчетными, в блоке 11 памяти в качестве начальных значений для след.К1-- щего шага интегрирования в момент времени t , так как они соответствуют значению этих величин в этот момент времени. Начальные значения остальных подынтегральных функций для момента времени t снимаются в этот момент времени с датчиков 21 и с блоков 6 и 7. При этом выработка потенциала записи точки решения узлом 34 блока 1 производится следующим образом. После отсчета 2 итераций, т.е. в момент времени (t, + ь ), счетчик 28 выдает сигнал, который поступает в блок 34 на вход элемента 58 задержки и, задержавшись на один такт, перебрасывает в единичное состояние триггер 57. Единичный сигнал с выхода триггера 57 в течение одного такта проходит через открытьй элемент И 59 (элемент 60 задержки обеспечивает задержку на один такт единичного сигнала с нулевого выхода триггера 57) и поступает на единичный вход триггера 61. В результате триггер 61

перебрасывается в единичное состоя-

ние и открывает элемент И 62. Тогда

первый временной импульс,соответствующий началу следующей итерации, проходит через этот элемент И 62 и перебрасывает в единичное состояние триггер 65, а задержавшись на один такт на элементе 63 задержки, проходит через элемент ИЛИ 64 и устанавjntnaeT в нулевое состояние тршч ер Ы, который закрывает элемент Л 62. В результате триттер 65 начинает выдавать на выход 74 блока 1 потенциал записи точки решения ;щитель- ностью одной итерации (так как последний кремеиной импульс, соответствующий концу итерация, проходит с в(гхода узла 35 через элемент И 66 и, задержавшись на такт на элементе 67 задержки, проходит через элемент ИЛИ 68 и сбрасывает триггер 65 в нулевое состояние), который поступает в блок II памяти и разрешает запись вычисленных за 2 итераций значений подын- тепральных функций, которые соответствуют значению этих величин в момен времени t , через блок 13 коммутации из тех ретаающих блоков 2, начальные значения подынтегральных функций ко- торых являются расчетными величинами

В результате вычисленные значения подынтегральных функций поступают с выходов регистров 86 этих решающих блоков 2 через открытые элементы И 79, элементы ИЛИ 80 и выходы 98 решающих блоков 2 и через блок 13 коммутации записываются в соответствующие регистры блока 11 памяти в качестве начальньгх значений расчетных величин к моменту времени г. , т.е. к очередному тагу интегрирования реального масштаба времени.

Кроме того, после отработки 2 итера1дай, т.е. в момент времени (t(+ ()„,), сигнал с выхода счетчика 28 гтоступает в илок 10 сравнения, разрешая сравнсн ие предельных значений контролируемых параметров, по- ступаюп их в соответствии с решаемой задачей с соответствуетцих выходов блока 8 граничных параметров (структура этого блока аналогична структуре блока 6) через блок 16 коммутации с вычисленными значениями подынтег- ральнмх функций, поступающих в соответствии с решаемой задачей с выходо 9в.тех решающих блоков 2, в регистра 86 которых фиксируются контролируемы параметры (например высота полета при Полетах на низких высотах).

После отработки входной информаци за время t, в первом шаге интегрирования реального процесса и записи вычисленных значений в блок 11 памяти узел 32 цродо-пжает выдавать сигнал, разрешающий решение, в решающие блок 2. вычисления в них продолжаются, и

за оставшееся время (tg,- m ) До следующего момента с поступления входной информации ИВС производит erne шагов интет-рироваршя по 2 итераций в каждом, прогнозируя поведение динамического объекта на вермя Т при условии, что управляющие воздействия (т.е. например, положени рулей высоты и т.п.) останутся неизменными. При этом после шага интегрирования счетчик 28, отсчитав 2 итераций, выдает сигнал, который изменяет, состояние счетчика 27 шагов интегрирования и одновременно разре- нает сравнение контролируемых параметров с их предельнь ми значениями в блоке 10 сравнения.

Б случае выхода какого-либо параметра за предельные значения на соответствующем выходе блока 10 появляется сигнал, который поступает в блок 3 вывода и разрешает индикацию значения счетчика 27, каждое значение которого соответствует времени p.Tgj, где р - значение счетчика 27, предупреждая тем самым оператора о выходе данного контролируемого параметра через время р Л , считая от времени tj реального процесса, за его предельные значения, если управляющие воздействия за этот период не будут изменены, и в результате оператор принимает соответствующие решения об изменении управляющих воздействий. Подсчет текуЕтего времени t реального процесса производится счетчиком 9 по сигналам из блока 1 с выхода элемента Н 25, и подачей сигналов с соответствующих выходов счетчика 9 в блок 3 вывода осуществляется индикация текущего времени кратно времени Tg, . По окончании последней итерации (/ +1) шага интегри&Х/ N

рования В момент времени (с,+(,, ) (счетчик 28, отсчитав последние 2 итераций на первом интервале Т , вырабатывает сигнал, который устанавливает счетчик 27 в состояние равное

Т (- + 1) и счетчик 27 вырабатывает

6Х .

в момент времени (t ) в начале итерации сигнал, который поступает i на вход элемента И 47 узла 32, но не проходит через него, так как триггер 46 установлен в нулевое состояние. Кроме того, этот сигнал, пройдя через элемент ИШ 56, устанавливает в нулевое состояние триггер 57,

закончив тем самым подготовку узла 34 к выработке потенциала записи точки следующего цикла вычислений, и поступает также в блок 33 на вход элемента И 50. Так как элемент И 50 открыт (триггер 46 с начала вычислений находится в нулевом состоянии и подает с нулевого выхода единичный сигнал на вход элемента И 50), то сигнал с выхода счетчика 27 проходит через элемент И 50 и элемент ИЛИ 51 и устанавливает триггер 52 в момент времени t +.,

( в X

t В единичное

состояние. В результате в момент времени tj, т.е. в момент поступления Iновой входной информации и начала первой итерации нового цикла вычислений, триггер 52 начинает выдавать потенциал записи исходных данных нового цикла вычислений длительностью одной итерации, который поступает ; через выход 74 в блок 11 памяти, через выход 75 - в блок 12 образования приращений и через выход 69 блока 1 в каждый решающий блок 2 на входы Элементов И 81, 91 и НЕ 78. В резуль тате также, как и в первой итерации первого цикла вычислений в момент времени .t,, элементы И 81, и 91 открываются, а элементы И 79 и 92 закрываются и начальные значения подынтегральных функций для момента времени t, также как и в момент времени t , поступают в соответствии с выбранной на пульте 23 управления блока 1 решаемой задачей с соответствующих выходов блока 6, 7 и 11 и датчиков 21 через соответствующие блоки 13, 14, 15 и 18 коммутации через соответ ствукадие элементы ИЛИ 22, входы 96 соответствующих решающих блоков 2 и через открытые элементы И 81 и ШШ 80 на входы сумматоров 84 и узлов 82 этих решающих блоков 2, причем из блока 11 поступают начальные значения расчетных величин для момента времени t, записанные в блок 11 из решающих блоков 2 в момент времени . Таким образом, начинается процесс вычислений во втором временном цикле от tj до t, который проводится также, как и в первом цикле, за тем исключением, что в блоке 12 образования приращений на поток приращений разворачивается не значение управляющего воздействия, поступающее с датчиков 20 управляицих воздействий в момент времени t, а раз10

ность между чнячеииями в моменты пре- мени г, и t, причем вычисляется эта разность следующим образом. По потенциалу записи исходных данных, поступающему в Течение первой итерации второго цикла вычислений, т.е. в момент времени t, с единичного выхода триггера 52 узла 32 через выход 75 блока 1 в блок 12, открьгоаются элементы И 114 и 119 и закрывается элемент И 117. В результате зна.чеяие управляющего воздействия проходит в момент времени t. с выхода соответствующего датчика 20 управляющих воз- 15 действий через вход 150 блока 12 и через открытый элемент И 114 блока 12 на входы элемента ИЛИ 115 и сумматора 126 и начинает через элемент ИЛИ 115 последовательно заноситься в ре- 20 гистр 116, а с выхода регистра 116 одновременно выдается через открытый элемент И 119 значение управляющего воздействия для момента времени t(, которое поступает на входы элементов 5 НЕ 120 и И 121. Так как триггер 122 в начале итерации первым временным импульсом установился в состояние, равное нулю, то он подает разрешаю- щий сигнал, с нулевого выхода на вход 30 , элемента И 121. В результате элемент И 121 открыт и первая единица в коде величины, поступающей из регистра 116, проходит через этот элемент И и задержавшись на один такт на эле- 35 менте 123 задержки, сбрасывает триггер 122 в единичное состояние, от- крыв тем самым элемент И 124. Одновременно единица с выхода элемента И 121 проходит через элемент ИЛИ 125 на вход сумматора 12о. Остальной код величины, поступагацей из регистра 116, проходит через открытый элемент И 124 и элемент ИЛИ 125 на вход сумматора 126, проинвертировавшись предварительно на элементе НЕ 120. В результате с выхода элемента ИЛИ 125 на вход сумматора 126 поступает дополнительный код значение управляющего воздействия, соответствующее моменту t и поступающее из регистра 116, а на второй вход этого сумматора 126 поступает с выхода элемента И 114 значение управляющего воздействия , соответствующее моменту вре- 5 мени с . Получаицаяся разность этих значений с выхода сумматора 126 поступает на вход элемента ИЛИ 130 и далее работа блока 12 происходит аналогично

0

5

0

33

работе блока в периом iuiK.ae вычислений, и за время i,,, в течение 2 итераций получиыпаяот разность значений управляющих воздействий полностью разлагается в поток од нораз- рядных приращений. При этом элемент 129 задержки обеспечивает задержку на один такт возникающего поразрядного переноса., а инверсное значение последнего временного импул1-са, по- стулающее с выхода элемента НЕ 128 на вход элемента И 127, запрещает подачу переноса . за знаковые разряд 1, возникающего при суммз- ропании отрицаго процесса, отсчитываемого счетчиком 9, и таким образом через определенные промежутки времени счетчик 9 производит в соответствии с с процессом изменение вьщаваемр11х блоком 7 величин (такой величиной является, например, вес самолета). Одновременно значение счетчика 9, соответствующее тек тцему време И реального про- 10 цесса, поступает в блок 3 вывода, ко- Topbrii осуществляет в процессе решения в каждом дакле вычислений индика- цИю текуа(его времени реал1 ного процесса, кратно времениtg, . Кроме тотельных чисел. В момент времени (t,+ 15 го,, в случае выхода контролируемого - т ) отсчитав 2 итераций, счетчик параметра за предельные значения из 28 выдает как и в первом цикле вычис- блока 10 сравнения в блок 3 вывода лений сигнал в блок 34, который выда-- поступает сигнал, который разрещает ет на выход 74 блока 1 потенциал за- индикацию значения счетчика 27, каж- писи точки длительностью одной Итера- 20 дое значение которого соответствует ции, по которому из соответствующих решающих блоков 2 в блок 11 памяти, также, как и в первом цикле вьиисле- н-ий, записываются вычисленные в момент времени (с,,,,) значения, со- 25 ответстзующие начальным значениям расчетных величин в момент времени

времени р -L , где р - значение счетчика 27, предупреждая тем самым оператора о выходе данного контролируемого параметра за его предельные значения через время p tgy/, считая

от времени t; реального процесса, за- фиксировагтного в счетчике 9 и индуцируемого в блоке 3, если управляющие воздействия за этот период времени 30 ® будут изменены. При этом вывод информации блоком 3 производится следующим образом. В случае, если по сигналу, разрешающ ему сравнение контролируемых параметров с их пре- дельньми значениямр и поступающему из счетчика 28 через пятый выход 73

Г. По окончании второго цикла вычислений, когда значение счетчика 27 в момент времени (с н- о) , достигает

Т величины ( 1) (этот счетчик яв

-

1),

ляется счетчиком по модулю (;;:- +

-&(

счетчик 27 снова выдает сигнал, по которому узел 33 в момент времени tj-t- Lgj t, выдает также, как и в предыдущий момент времени t , на выходы 69, 74 и 75 блока I потенциал записи исходных данных, но уже для третьего цикла вычислент{й и начнется треттгй цикл вычислений и т.д. При этом в процессе решения счетчик 9 изменяет свое состояние по -сигналам, поступаю- ,щим с выхода элемента И 25 блока 1, отсчитмвая текущее время реального процесса, и в каяздом цикле вычислений значения счетчика 9 поступают на входы дешифратора 19, который при достижении счетчиком заданного зна

35

от времени t; реального процесса, за фиксировагтного в счетчике 9 и индуцируемого в блоке 3, если управляющи воздействия за этот период времени 30 ® будут изменены. При этом вывод информации блоком 3 производится следующим образом. В случае, если по сигналу, разрешающ ему сравнение контролируемых параметров с их пре- дельньми значениямр и поступающему из счетчика 28 через пятый выход 73

блока 1, блок 10 сравнения обнаруживает выход какого-либо параметра за его предельные значения, то на со ответствующем выходе блока 10 появ- ляетс-я единичный сигнал, который поступает через соответствующий вход из группы входов 189 на единичный вход соответствующего триггера 178 из группы триггеров и устанавливает его в единичное состояние. В результате на единичном выходе этого триггера 178 появляется единичный сигнал которь й поступает в узел 185 индика40

45

чения выдает в блок 7 на соответству- ции., где загорается соответствующий, ющий вход сигнал, по которому к выходам 112 блока 7 через элементы ИЛИ 108 и через соответствующие э.пементы И 109, на которые поступил этот сигнал, подключатся элементы ИЛИ 110, на выходах которых образуются коды прогрйммно-изменяем ях величин, соответствующие моменту времени реаль1Ютранспорант, предупреждающий о выход данного контролируемого параметра за его предельное значение и в узел 186 звуковой сигнализэиии, вызывая выра- 55 ботку предупреждающего звукового сиг нала соответствующего тембра. Одновременно единичный сигнал с единичного выхода этого триггера 178 посту

57672 34

го процесса, отсчитываемого счетчиком 9, и таким образом через определенные промежутки времени счетчик 9 производит в соответствии с с процессом изменение вьщаваемр11х блоком 7 величин (такой величиной является, например, вес самолета). Одновременно значение счетчика 9, соответствующее тек тцему време И реального про- 10 цесса, поступает в блок 3 вывода, ко- Topbrii осуществляет в процессе решения в каждом дакле вычислений индика- цИю текуа(его времени реал1 ного процесса, кратно времениtg, . Кроме то15 го,, в случае выхода контролируемого параметра за предельные значения из блока 10 сравнения в блок 3 вывода поступает сигнал, который разрещает индикацию значения счетчика 27, каж- 20 дое значение которого соответствует 25

го,, в случае выхода контролируемого параметра за предельные значения из блока 10 сравнения в блок 3 вывода поступает сигнал, который разрещает индикацию значения счетчика 27, каж- дое значение которого соответствует

времени р -L , где р - значение счетчика 27, предупреждая тем самым оператора о выходе данного контролируемого параметра за его предельные значения через время p tgy/, считая

го,, в случае выхода контролируемого параметра за предельные значения из блока 10 сравнения в блок 3 вывода поступает сигнал, который разрещает индикацию значения счетчика 27, каж- дое значение которого соответствует

от времени t; реального процесса, за- фиксировагтного в счетчике 9 и индуцируемого в блоке 3, если управляющие воздействия за этот период времени ® будут изменены. При этом вывод информации блоком 3 производится следующим образом. В случае, если по сигналу, разрешающ ему сравнение контролируемых параметров с их пре- дельньми значениямр и поступающему из счетчика 28 через пятый выход 73

блока 1, блок 10 сравнения обнаруживает выход какого-либо параметра за его предельные значения, то на соответствующем выходе блока 10 появ- ляетс-я единичный сигнал, который поступает через соответствующий вход из группы входов 189 на единичный вход соответствующего триггера 178 из группы триггеров и устанавливает его в единичное состояние. В результате на единичном выходе этого триггера 178 появляется единичный сигнал, которь й поступает в узел 185 индика

ции., где загорается соответствующий,

транспорант, предупреждающий о выходе данного контролируемого параметра за его предельное значение и в узел 186 звуковой сигнализэиии, вызывая выра- ботку предупреждающего звукового сигнала соответствующего тембра. Одновременно единичный сигнал с единичного выхода этого триггера 178 поступает на вход соответствуктцего элемента И 180, на другой вход которого еще в течение такта поступает задержанный на элементе 179 задержки единичный сигнал с нулевого выхода этого триггера 178. В результате на выходе этого элемента И 180 появляется импульс, который поступает на первые входы соответствующей группы элементов И 181 из тп групп этих элементов и разрешает прохождение через эту группу элементов И 181 значений счетчика 27, поступакмцих из блока 1 с единичных выходов счетчика 27 через выход 70 и вход 187 на вторые входы групп элементов И 181. В результате значение счетчика 27, соответствующее моменту времени возможного выхода контролируемого параметра за его предельные значения, считая от времени t реального процесса, если упединицы секунд и т.д.), индицируется кратно времени 2 (,« узлом 185 индикации. По окончании каждого цикла прогнозирования, когда значение 5 счетчика 27 достигает значения

Т (--+ 1), на выходе дешифратора 173

ех ,

появляется единичный сигнал, который поступает на вход элемента 174 заtO держки и элемента НЕ 175 и по заднему фронту этого cTirHajia на выходе элемента И 176 появится импульс, который проходит через элемент ИЛИ 177 и поступает на нулевые входы

15 группы триггеров 178 и каждой группы триггеров 182 из m групп этих триггеров, устанавливая их в нулевое состояние и подготавливая тем самым к новому циклу прогнозирования

20 . Б каждом решающем блоке 2 в цепь переноса сумматора 84 включен одно- тактный элемент 85 задержки, который служит для образования переноса при сложении приращения подынтегральной