Изобретение относится к вычислительной технике и предназначено для решения широкого класса задач, описываемых системами дифференциальных и алгебраических уравнений и уравнениями, сводящимися к дифференциальным, для моделирования сложных динамических систем, непрерывных процесс и подвижных объектов, а также для использования в системах управления этими процессами и объектами. Известна цифровая интегрирующая структура, содержащая решающие блоки блок коммутации, блоки ввода и вывот да и блок управления, и предназначенная для решения широкого класса задач, описываемых системами диффере циальных и алгебраических уравнений и уравнениями, сводящимися к диффег ренциальным II. Недостатком известной структуры является трудность миниатюризации из-за наличия блока коммутации, имею щего очень большое количество внешних выводов и требующего больших затрат оборудования. Наиболее близкой по технической сущности к предлагаемому изобретени является цифровая интегрирующая структура, содержащая решающие блок блок ввода, блок вывода, блок набора, блок управления, блок коммутации, причем выход блока набора соединен с группой входов каждого решающего блока, а вход блока набора соединен с первым выходом каждого решающего блока, первый выход блока ввода соединен с первым входом каждого решающего блока, первый выход блока управления соединен с входом блока. ввода и вторым входом каждого решающего блока, а вход блока управления соединен с вторым выходом каждого решающего блока и с первым входом блока вывода, второй вход которого соединен с вторым выходом блока управления, первая группа входов блока коммутации соединена с вторым выходом блока ввода, а каждый вход второй группы входов блока коммутаций соединен с первым выходом соответствующего решающего блока, первая группа входов каждого решающего блока соединена также с соответствующей группой выходов блока коммутации С23 . Недостатком известной .интегрирующей структуры является ее низкая надежность.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что в структуру, содержащую блок ввода, блок управления, блок вывода и решающие блоки, каждый из которых включает арифметико-логический узел, причем выход блока ввода соединен с первым входом арифметико-логического узла каждого решающего блока, первый выход блока управления соединен с входом блока ввода и вторым входом арифметико-логического узла каищого решающего блока, второй выход блока управления соединен с входом блока вывода, группа входов которого соединена с первыми выходами арифметико-логического узла каждого решающего блока, введены адресный счетчик, элемент ИЛИ положительных приращений, элемент ИЛИ отрицательных приращений и в каждый решающий блок введены группа регистров адреса, регистр адреса, триггеры положительных и отрицательных приращений, группа узлов сравнения, узел сравнения, входные элементы И положительных и отрицательных приращений, выходные элементы И положительных и отрицательных приращений, причем вход адресного счетчика соединен с третьим выходом блока управления, выход каждого разряда адресного счетчика соединен с группой входов блока управления, с первой группой ВХОДОВ узла сравнения каждого решающего блока и с первой группой входов узлов сравнения группы каждого решающего блока, выход блока ввода соединен с первьлми входами регистра адреса и регистров адреса группы каждого решающего блока, первый выхс2 д блока управления соединен с вторым входом регистра адреса, с вторыми входами регистров адреса группы и с нулевыми входами триггеров положительных и отрицательных приращений каждого решающего блока, в каждом решающем блоке вторая группа входов узлов сравнения группы соединена с выходом каждого разряда соответствующего регистра адреса группы и вторая группа входов узлов сравнения соединена с выходом каждого разряда регистра, адреса, выходы узлов сравнения группы соединены с первыми входами соответствующих входных элементов И положительных и отрицательных приращений каждого решающего блока, группы ,входов арифметико-логического узла соединена с выходом триггеров положительных и отрицательных приращений каждого решающего блока, единичные входы которых соединены соответственно с выходами входных элементов И положительных и отрицательных приращений каждого решающего блока, второй и третий выходы арифметико-логического

узла соединены соответственно с первыми входами выходных элементов И положительных и отрицательных приращений в каждом решающем блоке, вторые входы которых соединены с выходом узла сравнения каждого решающего блока, входы элементов ИЛИ положительных и отрицательных приращений соединены соответственно с выходами выходных элементов И положительных и отрицательных приращений каждого решающего блока, а их выходы соединены соответственно с вторыми входами каждого входного элемента И положительных и отрицательных приращений каждого решаиощего блока.

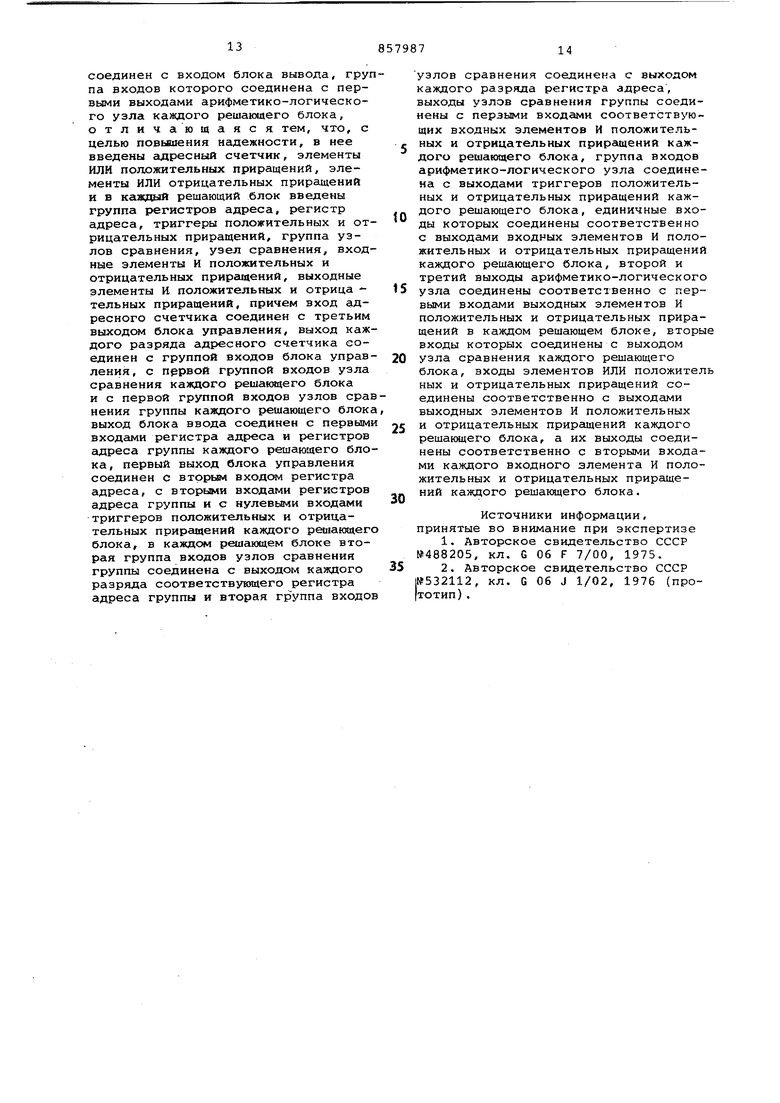

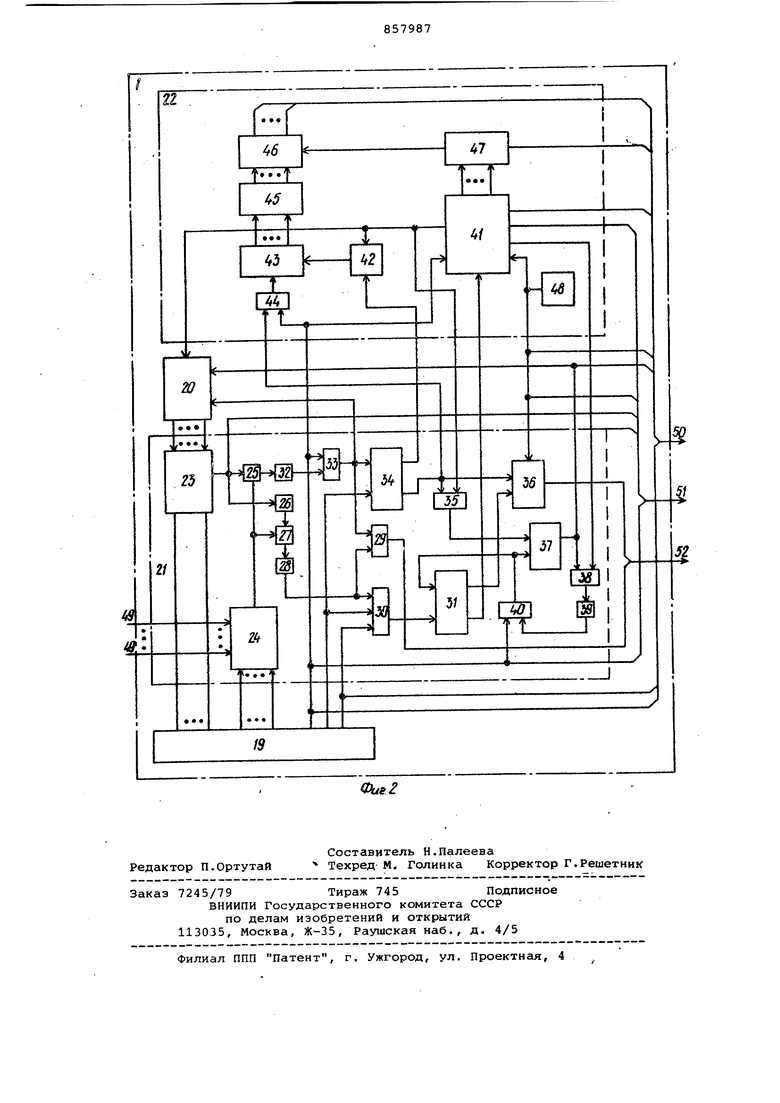

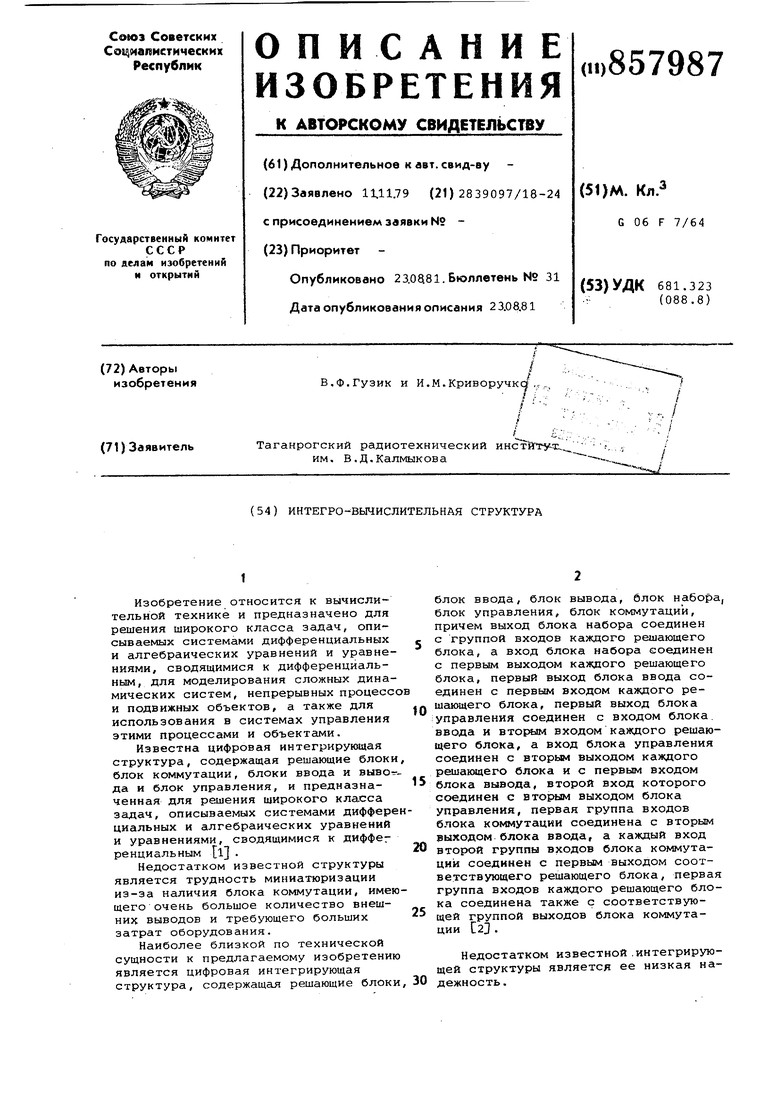

На фиг. 1 представлена блок-схема интегро-вычислительной структуры; на фиг. 2 - блок управления структуры .

Структура содержит блок 1 управления , блок 2 ввода, блок 3 вывода, адресный счетчик 4, элемент ИЛИ 5 положительных приращений, элемент ИЛИ б отрицательных приращений и решающие блоки 7, содержащие арифметико-логический узел 8, регистр 9 адреса, группу регистров 10 адреса, триггеры 11 положительных приращений, триггеЕ«л 12 отрицательных приращений, узел 13 сравнения, группу узлов 14 сравнения адресов, входные элементы И 15 положительных приращений, .входные элементы И 16 отрицательных приращений, выходной элемент И 17 положительных приращений, выходной элемент И 18 отрицательных приращений-.

Блок 1 управления (фиг,2) содержи пульт 19 управления, счетчик 20 итераций, узел 21 пуска-останова, узел 22 управляющих импульсов и потенциалов. Узел 21 содержит первый элемент 23 сравнения, второй элемент 24 сравнения, первый элемент И 25, инвертор 26, второй элементИ 27, первый элемент 28 задержки, первый элемент ИЛИ 29, второй элемент ИЛИ 30, первый триггер 31, второй элемент 32 задержки, третий элемент ИЛИ 33, второй триггер 34, третий элемент И 35, четвертый элемент И 36, третий триггер 37, пятый элемент И 38, третий элемент 39 задержки, четвертый элемент ИЛИ 40.

Узел 22 управляющих импульсов и потенциалов содержит распределитель 41 импульсов, элемент И 42, счетчик 43, элемент ИЛИ 44, дешифратор 45, групп 46 клапанов, группу 47 триггеров, генератор 48 тактовых импульсов, группу входов 49 бЛока управления, первый выход 50 блока управления, второй выход 51 блока управления, третий выход 52 блока управления.

Решение задач на интегро-вычислительной структуре осуществляется приближенными методами численного интегрирования. Результаты решения получаются в виде числовых значений искомых величин через разные интерва лы времени. Решаемая задача представляется в виде симметричной формы уравнений Шеннона .52.-, . ( ; Vp(X)rVpj,o.,3,...,N, где Ap(t4 и (j 1, 2, . . . ,N) являютс постоянными коэффициентами, принимающими значения О или 1 в зависи,мости от решаемой задачи. На входе арифметико-логических узлов информация подается в виде приращений подынтегральной функции и переменной интегрирования. Арифме тико-логический узел оперирует с одноразрядными приращениями, представленными в тернарной системе кодирования, и выполняет цифровое инт рирование,суммирование приращений, функцию знака, ограничение,слежение Программа коммутации для каждого решающего блока записывается в виде адресов входных приращений по каждо му входу. Перед настройкой интегро-вычисли тельной структуры на решение задачи и выполнением процесса решения производится установка в исходное поло жение блока 2 ввода и узла 8, регистра 9, регистров 10, триггеров 1 и 12, соответствующего сигнала с вы хода пульта 19 управления на выход 50 блока 1 управления. Одновременно подачей этого же сигнала на выход 5 блока 1 управления производится уст новка в исходное состояние блока 3 вывода, а подачей этого сигнала с вы хода пульта 19 управления через эле менты ИЛИ 33 и ИЛИ 29 блока 21 на третий выход 52 блока 1 управления производится установка в нулевое по ложение адресного счетчика 4. Кроме того, этот сигнал с выхода пульта 19 управления, пройдя через ИЛИ 33, устанавливает в нулевое положение триггер 34 блока 21 и счетчик 20, пройдя через элемент ИЛИ 40, устанав ливает в нулевое положение триггеры 31 и 37 блока 21, пройдя через элемент ИЛИ 44, устанавливает в нулевое положение счетчик 43 блока 22, а также устанавливает в исходное поло жение распределитель 41 импульсов блока 22, поступив на третий его вход Затем производится настройка интегро-вычислительной структуры на решение задачи. При этом с выхсда пульта 19 управления подается сигнал начала настройки, который через выход 50 блока 1 управления поступает в блок 2 ввода и через элемент ИЛИ 30 блока 21 поступает на единичный вход триггера 31 этого же блока. В результате триггер 31 блока 21 переходит в единичное состояние и подает на первый вход распределителя 41 импульсов блока 22 сигнал разрешения запуска. По этому сигналу распределитель 41 блока 22 запускается и начинает вырабатывать распределенные временные импульсы, которые с выходов распределителя 41 поступают на единичные и нулевые входы группы 47 триггеров блока 22 и производят выработку управляющих потенциалов соответствующей длительности, которые с второго выхода узла 47, так же как и распределенные временные импульсы с третьего выхода распределителя 41, поступают через первый выход 50 блока 1в блок 2 ввода и решающие блоки 7 для обеспечения организации ввода настроечной информации. Кроме того, первый временной импульс в каждом цикле проходит с первого выхода распределителя 41 через открытый элемент И 42 блока 22 (так как триггер 34 блока 21 после установки в исходное состояние выдает с нулевого выхода разрешающий сигнал на второй вход И 42 блока 22) на суммирующий вход счетчика 43 и изменяет его состояние. Счетчик 43 является счетчиком по модулю (d + 3), где d - количество входов подынтегральной функции и переменной интегрирования в узле 8, т.е. через каждые (d+3) цикла состояние счетчика повторяется и на (d + 3) выходах .дешифратора 45 блока 22 последовательно появляются разрешающие сигналы, которые поступают на соответствующие клапаны узла 46 и последовательно пропускают потенциалы соответствующей длительности с выхода узла 47 через узел 46 и первый выход 50 блока 1 на управляющий вход соответствующего адресного регистра 9 или 10, или регистра подынтегральной функции или регистра кода операции в узле 8 для организации последовательного ввода настроечной информа ии в каждом цикле в соответствующий регистр из (d+3) регистров выдранного решающего блока 7. . В то же время, после подачи сигнала начала настройки одновременно с выработкой блоком 1 управления управляющих сигналов, необходимых для организации ввода настроечной информации в решающие блоки 7, сигнал начала настройки поступает с выхода пульта 19 управления через первый выход 50 блока 1 в блок 2ввода, запускает его и этот блок начинает считывать с внешних носителей настроечную информацию и подавать ее в последовательно выбираемые решающие блоки 7. И за (d+3) цикла подаваемая в выбранный решающий блок 7 настроечная информация последовательно вводится в соответствующие регистры этого блока с помощью последовательно поступающих в каждом цикле на соответствующий регистр блока 7 с выходов группы 46 клапанов узла 22 управляющих потенциалов соответствующей длительности. При этом в каждый решающий блок 7, в регистр 9 заносится адрес, соответствующий номеру решающего элемента на структурной схеме задачи, в узел 8 заносятся соответствующие этому решающему элементу начальные значения подынтегральной функции и кода операций, а в регистры 10 - соответствующие ему адреса входных приращений, т.е. номера тех решающих элементов, которые по структурной, схеме решения задачи соединены с соответ.ствующим входом данного решающего элемента.

После ввода всей настроечной информации в решающие блоки 7 настройки Предлагаемой интегро-вычислительной структуры на решение задачи заканчвается и начинается выполнение процесс решения,которцй на каждой итерации разбивается на два этапа: этап вычислений и этап передачи приращений.

Перед началом решения на пульте 19 управления блока 1 устанавливается необходимое количество итераций, в течение которого вычисляется точка решения, и устанавливается количество решающих модулей, задействованных в решаемой задаче. Затем на пульте 19 управления вырабатывается команда Пуск и соответствующий сигнал с второго выхода пульта 19 управлёння поступает на единичный вход триггера 34 узла 21, устанавливая его в единичное состояние, и через элемент ИЛИ 30 - на единичный вход триггера 31, подтверждая его единичное состояние. В результате триггер 34 узла 21 закрывает элемент И 42 узла 22 и подачей сигнала с единично.го выхода через ИЛИ 44 узла 22.устанавливает в нулевое состояние счетчик 43, запрещая тем самым выработку управляющих сигналов, обеспечивающих ввод настроечной информации в регистры решающих блоков 7. Одновременно сигнал с единичного выхода триггера 34 21 открывает, элемент И 35 узла 21 и первый временный импульс, соответствующий началуитерации, с первого выхода распределителя 41 узла 22 проходит через элемент И 35 и устанавливает в единичное состояние триггер 37 узла 21, который начинает выдавать через первый выход 50 блока 1 в узел 8 каждого решающего блока 7 сигнал, разрешающий решение. Одновременно в решгцощие блоки 7 из блока 1 управления с выходо распределителя 41 и группы 4/ триггеров поступают временные импульсы и управляющие потенциалы, обеспечивающие процесс вычислений.

Начинается этап вычислений на первой итерации, в течение которого в узле 8 каждого решающего блока 7 производятся вычисления приращений интеграла для следующей итерации. Одновременно с выхода триггера 37 узла 21 поступает на управляющий вход счетчика 20 разрешающий сигнал который разрешает суммирование, и первый временной импульс, соответствующий началу итерации, поступает с выхода распределителя 41 импульса узла 22 и перебрасывает счетчик 20 в состояние, равное единице.

По окончании этапа вычислений на первой итерации последний временной импульс, соответствующий концу итерции , поступает с третьего выхода распределителя 41 через первый выхо 50 блока 1 на нулевые входы триггеров 11 и 12 каждого решающего блока 7 и устанавливает их в нулевое состояние, подготовляя их этим к выпонению этапа передачи приращений. Одновременно последний временной импульс пройдет с второго выхода распделителя 41 узла 22 через открытый элемент И 38 узла 21 и, задерживаяс на один такт на элементе 39 задержки, поступает через ИЛИ 40 на нулевые вхоДы триггеров 31 и 37 узла 21 и устанавливает их в нулевое состояние. В результате триггер 31 узла 21 прекращает выработку сигнала разрешения запуска в распределитель 41 узла 22, и распределитель 41 перестает выдавать на выход 50 блока 1 распределенные временные импульсы, а группа 47 триггеров управляющие потенциалы, необходимые для организации процесса вычислений в решающих блоках 7, а триггер 37 узла 21 прекращает выработку сигнала, разрешающего решение.

На этом этап вычислений заканчивается и, начиная со следующего такта, тактирующие импульсы с выхода генератора 48 узла 22 через открыты элемент И 36 узла 21 (так как триггер 31 после окончания этапа вычислений устанавливается в нулевое состояние, а триггер 34 находится с начала процесса решения задачи в единичном состоянии) и через третий выход 52 блока 1 начинают поступать как импульсы адресации на с.уммирующий вход адресного счетчика 4, последовательно изменяя его состояние от О до N (N i N, Где N - количество решающих блоков, згщействованных в решаемой задаче, а N - общее количество решающих модулей в-структуре) и, обеспечивая передачу выходных одноразрядных приращений, представленных в тернарной системе коди рования, на входы решающих блоков 7 начинается этап передачи приращений для второй итерации. При этом первый импульс, поступивший в счетчик 4 из блока 1 управления с выхода элемента И 36, перебрасывает этот счетчик в состояние, равное единице, В результате в решающем блоке 7/ в регистр 9 которого записан адрес, равный единице, узел 13 выдает сигнал равенства адресов и разрешает подачу выходных приращений этого решающего блока 7, соотве ствующего первому решающему элементу на структурной схеме задачи, через соответствующие элементы И 17 и И 18 этого блока и через соответствующие элементы ИЛИ 5 и ИЛИ 6 на входы всех решающих блоков 7. Одновременно в решающих блоках 7, соответствующих решающим элементам, входы которых по структурной схеме задачи соединены с выходом первого решающего элемента, в соответствующих регистрах 10 записывается адрес равный 1единице, и соответствующие им узлы 14 сравнения ВЕдцают сигналы равенства адресов, которые открываю соответствующие входные элементы И15иИ1би выходные приращения первого решающего элемента с выходов ИЛИ 5 и ИЛИ 6 через эти элементы И 15 и И 16 поступают на единичные входы соответствующих триггеров ,11 и 12 и записываются в них. В следующем такте из блока 1 управления с выхода элемента И 36 в счетчик 4 поступает второй импуль Счетчик 4 устанавливается в состояние, равное двум, и выходные приращения из решающего блока 7, соответ ствующего второму решающему элемент записываются в соответствующие триг геры 11 и 12 тех решающих блоков 7, которые соответствуют решающим элементам, соединенным по структурной схеме задачи с выходом второго решающего элемента. В следующем такте счетчик 4 уста навливается в состояние, равное тре и происходит переадресация приращений третьего решающего элемента и т.д. до N-ro такта, в котором про исходит переадресацйя приращений по леднего N-ro решающего элемента решаемой задачи. Одновременно в N-OM такте установленное на пульте 19 управления блока 1 значение числа решающих модулей, задействованных в решаемой задаче, совпадает с кодо поступающим через группу входов 49 блока. 1 из адресного счетчика 4. В результате элемент 24 сравнения выдает сигнал равенства кодов, кото рый поступает на входы элементов И 25 и И 27. Но так как на выходе элемента 23 сравнения сигнал равенс ва кодов еще отсутствует, то элемент И 25 закрыт, а элемент И 27 открыт, так как на выходе инвертора 26 разрешающий сигнал, и сигнал равенства кодов -поступает в N-OM такте с выхода элемента 24 через И 27, и, зещерживаясь на один такт на элементе 28 задержки, происходит в следующем такте через элемент ИЛИ 29 в счетчик 4, устанавливая его в нулевое состояние, а через элемент ИЛИ 30 на единичный вход триггера 31, устанавливая его в единичное состояние и запрещая тем самым прохождение импульсов адресации через элемент И 36 на вход счетчика 4 и одновременно разрешая запуск распределителя 41 подачей сигнала разрешения запуска с единичного выхода триггера 31. На этом этап передачи приращений заканчивается, распределитель 41 импульсов запускается и первый временной импульс пройдет через открытый элемент И 35, так как триггер 34 находится с начала процесса решения задачи в единичном состоянии, и устанавливает в единичное состояние триггер 37, который начнет выдавать через первый выход 50 блока 1 в узел 8 каждого решающего блока 7 сигнал, разрешающий решение. Одновременно в решающие блоки 7 из блока 1 управления с выходов распределителя 41 и группы 47 триггеров поступают временные импульсы и управляющие потенциалы, обеспечивающие процесс вычислений. Начинается этап вычислений на второй итерации, в течение которого одноразрядные приращения, представленные в тернарной системе кодирования, с выходов триггеров 11 к 12 поступают Б виде потенциалов, соответствующих +1 или -1, на соответствующие входы узла 8 каждого решающего блока 7 и в них производятся вычисления новых значений подынтегральной функции и приргицений интеграла для следующей интерации. Одновременно с выхода триггера 37 узла 21 поступает на управляющий вход счетчика 20 итераций разрешаннций сигнал, который, разрешает суммирование, и первый временной импульс, соответствующий началу итерации, поступает с выхода распределителя импульсов 41 узла 22 и перебрасывает счетчик 20 в состояние, равноедвум. По окончании этапа вычислений на второй итерации последний временной импульс, соответствующий концу итерации, поступает с третьего выхода распределителя 41 через первый выход 50 блока 1 на нулевые-входы триггеров 11 и 12 и устанавливает их в ну-;левое состояние, подготовляя тем самым к выполнению этапа передачи приращений. Одновременно последний временной импульс проходит с второго

выхода распределителя 41 узла 22 через открытый элемент И 38 узла 21 и, задержавшись на один такт на элементе 39 задержки, поступает через ИЛИ 40 на нулевые входы триггеров 31 и 37 и устанавливает их в нулевое состояние. В результате триггер 31 узла 21 прекращает выработку сигнала разрешения запуска в распределитель 41 узла 22, и распределитель 41 перестает выдавать на выход 50 блока 1 распределенные временные импульсы, а группа 47 триггеров управляющие потенциалы, необходимые для организации процесса вычислений в решающих блоках 7, а триггер 37 узла 21 прекращает выработку сигнала разрешающего решение.

На этом этап вычислений заканчивается и со следующего такта начинается этап передачи приращений. Далее этап вычислений и этап передачи приращений периодически повторяется Синхронизация работы всех блоков структуры осуществляется подачей синхронизирующих импульсов с выхода генератора 48 узла 22.

После обработки заданного количества итераций счетчик 20 в начале этапа вычислений на последней итерации первым временным импульсов перебрасывается в состояние, соответствующее заданному на пульте управления количеству итераций и в результте элемент 24 сравнения блока 21 выдает сигнал равенства кодов, который через второй выход 51 поступает в блок 3 вывода и запускает его, Блок 3 производит вывод на печать получаемых на последней итерации знчений подынтегральных функций из тех узлов 8, в коде операции которы имеется признак печати. После прове дйния этапа вычислений на последней итерации выполняется этап передачи приращений, по окончании которого элемент 24 сравнения выдаёт сигнал равенства кодов и, так как на выходе элемента 23 сравнения тоже имеется сигнал равенства кодов, элемент И 27 закрыт и не пропускает сигнал на запуск распределителя 41, но в то же время элемент И 25 открыт и сигнал с выхода узла 24 проходит через элемент И 25 и, задержавшись на один такт на элементе задержки 32, проходит через элемент ИЛИ 33 и устанавливает в нулевое состояние триггер 34 узла 21, счетчик итераци 20, а, пройдя через ИЛИ 29 и третий выход 52 блока 1, устанавливает в нулевое состояние адресный счетчик

На этом процесс вычисления первой точки решения заканчивается и после окончания печати всей выводимой информации данной точки решения подачей сигнала Пуск с второго выхода пульта 19 управления устанавлибаются в единичное состояние

триггера 31 и 34 узла 21 и начинают ся вычисления второй точки решения.

После получения необходимого количества точек решения процесс решения задачи заканчивается.

Таким образом, предлагаемая интегро-вычислительная структура с одноразрядными приращениями позволяет устранить трудно поддающийся миниатюризации блок коммутации за счет изменения принципа передачи приращений и введения коммутационного оборудования в решающие модули, в результате чего обеспечивается возможность миниатюризации структуры, так как реализация решающих модулей с введенным в них коммутационным оборудованием, а также остальных блоков структуры в виде больших интегральны схем не представляет затруднений.

В то же время реализация блоков известной интегро-вычислительной структуры в виде больших интегральных схем не представляется возможной из-за наличия блока коммутации, имеющего очень большое количество внешних выводов и требующего больших затрат оборудования, а расчленение блока коммутации на отдельные узлы с целью реализации их в виде отдельных больших инте,гральных схем малоэффективно, так как, во-первых, число этих интегральных схем для известной структуры оказывается значительным, а во-вторых, число внешних выводов еще более возрастает. Кроме того, устранение блока коммутации повышает надежность предложенной интегро-вычислительной структуры так как значительно сокращается число внешних выводов и уменьшились затраты оборудования. При всем этом предлагаемая структуре, сохраняет универсальность коммутации, которую известная интегро-вычйслительиая структура обеспечивает посредством блока коммутации, так как любой вход любого решающего модуля предлагаемой структуры можно соединить с выходом любого решающего модуля, задав соответствующующий адрес в регистр адреса входных приращений выбранного решающего модуля.

Формула изобретения

Интегро-вычислительная структура, содержащая блок ввода, блок управления, блок вывода и решающие блоки, каждый из которых включает арифметико-логический узел, причем выход блока ввода соединен с первым входом арифметико-логического узла какдого решающего блока, первый выход блока управления соединен с входом блока ввода и вторым входом арифметикологического узла каждого решающего 5 блока, второй Ви1ход блока управления

соединен с входом блока вывода, группа входов которого соединена с первыми выходами арифметико-логического узла каждого решающего блока, отличающаяся тем, что, с целью повышения надежности, в нее введены адресный счетчик, элементы ИЛИ положительных приращений, элементы ИЛИ отрицательных приргццений и в каждый решающий блок введены группа регистров адреса, регистр адреса, триггеры положительных и отрицательных приращений, группа узлов сравнения, узел сравнения, входные элементы И положительных и отрицательных приращений, выходные элементы И положительных и отрица тельных приращений, причем вход адресного счетчика соединен с третьим выходс л блока управления, выход каждого разряда адресного счетчика соединен с группой входов блока управления , с пррвой группой входов узла сравнения каждого решающего блока и с первой группой входов узлов сравнения группы каящого решающего блока выход блока ввода соединен с первьнчи входами регистра адреса и регистров адреса группы каждого решающего блока, первый выход блока управления соединен с втррьм входом регистра адреса, с вторыми входами регистров адреса группы и с нулевьми входами триггеров положительных и отрицательных приращений каждого решающего блока, в каждом решающем блоке вторая группа входов узлов сравнения группы соединена с выходом каждого разряда соответствующего регистра адреса группы и вторая группа входов

узлов сравнения соединена с выходом каждого разряда регистра адреса, выходы узлов сравнения группы соединены с первыми входами соответствующих входных элементов И положительг ных и отрицательных приращений каждого решающего блока, группа входов арифметико-логического узла соединена с выходами триггеров положительных и отрицательных приращений каждого решающего блока, единичные входы которых соединены соответственно с выходами входных элементов И положительных и отрицательных приращений каждого решающего блока, второй и третий выходы арифметико-логического

5 узла соединены соответственно с первьлми входами выходных элементов И положительных и отрицательных приращений в каждом решающем блоке, вторые входы которых соединены с выходом

0 узла сравнения каждого решающего

блока, входы элементов ИЛИ положитель ных и отрицательных приращений соединены соответственно с выходами выходных элементов И положительных

5 и отрицательных приращений каждого решающего блока, а их выходы соединены соответственно с вторыми входами каждого входного элемента И положительных и отрицательных приращеНИИ каждого решающего блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР №488205, кл. G Об F 7/00, 1975. 2. Авторское свидетельство СССР 1№532112, кл. G Об J 1/02, 1976 (про(тотип) . шею ГЖ1Г771

S

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Устройство для управления распределением задач | 1977 |

|

SU696471A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

Авторы

Даты

1981-08-23—Публикация

1979-11-11—Подача