(54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ

t

Изобретение относится к вычислительной технике .и может быть испольэова.W-J в магнитных запоминающих устройствах (ЗУ).

Известно устройство для считьтання информации, содержащее мостовую схему, к одной диагонали моста подключен буферный каскад, а к другой - ли- ;ния задержки, в плечах моста включ)ны резисторы , к общим точкам которых, подк лючен дифференииалысый усилитель .

Наиболее близким техническим решением к данному является блок для считывания информации, содержащий усилители считьюания, подключенные к разрядно-считьтающим шинам числовых линеек накопителя, к входам числового регистра и к формирователю стробируюшего сигнала, эталонные усилители считывания, подключенные к разрядно-сч тываюшим линиям эталонных числовых линеек накопителя Г2, ИЗ НАКОПИТЕЛЯ

Известные устройства не позволяют осуществить воспроизведение сигналов чтения в ЗУ с высокой степенью поме-хозашищенности в них отсутствуют блоки и элементы, позволяющие учитьюать время стробирования сигналов чтения в зависимости от уровня помех в разрядно-считывающих шинах.

Цель изобретения - повышение помехозащищенности устройства для счи10тывания информашш из иакопителя.

Поставленная цель достигается тем, что в устройстве для считывания инфор.лации из накопителя, содержащее усилители считывания , одни входы которых

ts подключены к разрядно-считьтающим шинам чигповых линеек накопителя, другиек выходу формирователя стробируюш го сигнала, а выходы усилителей считывания подалючены к входам . числового регистра, эталонные усилители считьюа- , ния, подключенные к разряано-считываюшим шинам эталонных числовых линеек накотштеля, введены инвертор, сумматор, ждущий мультивибратор и дифференшфующий элемент, выход которого подключен к входу формирователя стробрующего сигнала, а вход - к выходу ждущего мультивибратора, вход которого соединен с выходом сумматора, первый вход которого подключен к выходу первого эталонного усилителя счтывания, а второй - к выходу инвертора вход инвертора соединен с выходом второго эталонного усилителя считьшания.

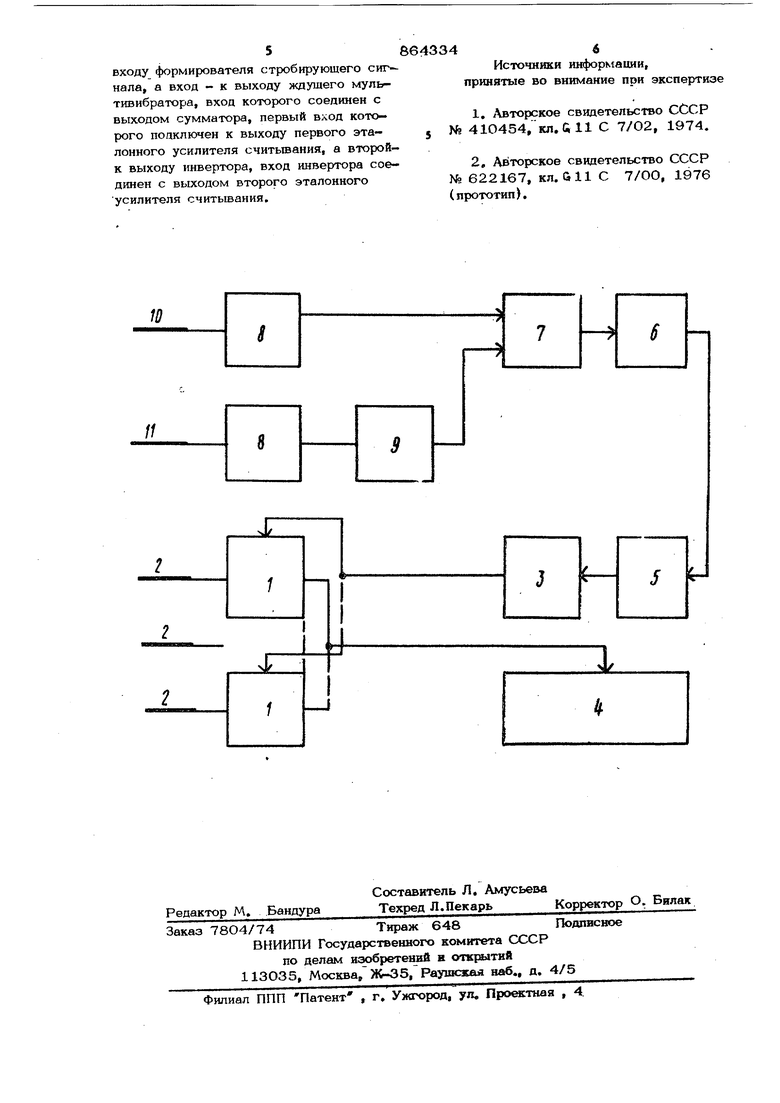

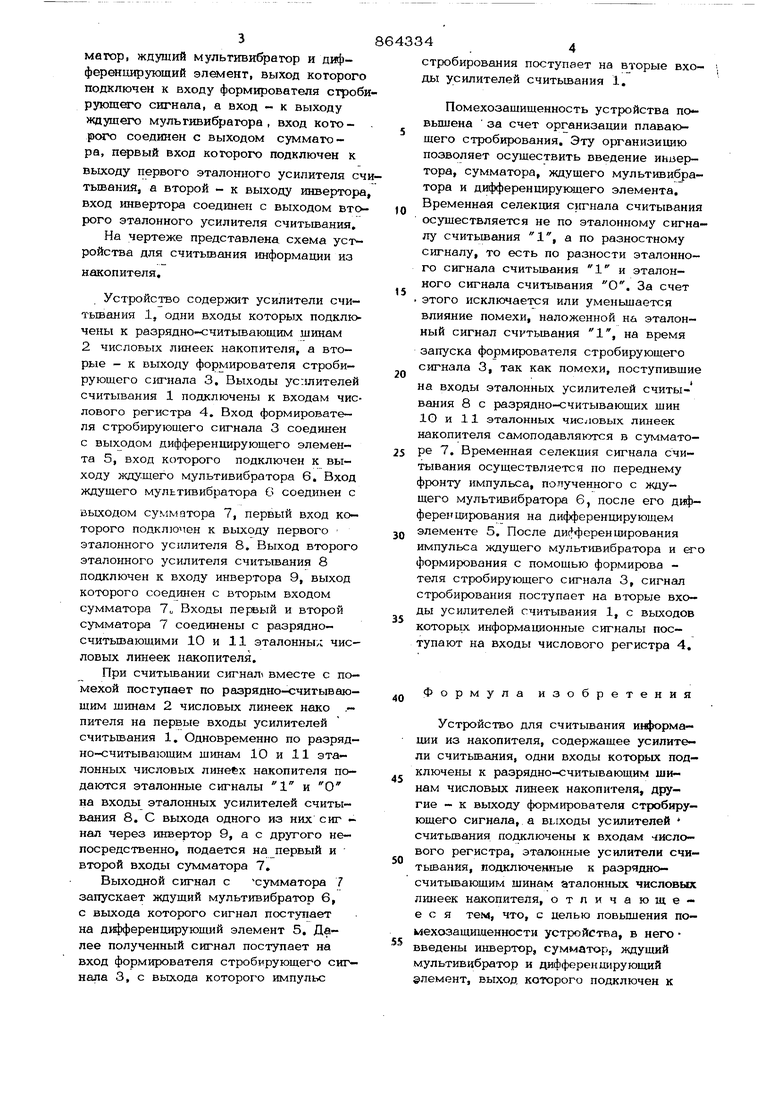

На чертеже представлена схема устройства для считьшания информации из накопителя.

Устройство содержит усилители счи- тьшания 1, одни входы которых подключены к разрядно-считывающим шинам 2 числовых линеек накопителя, а вторые - к выходу формирователя строби- рующего сигнала 3, Выходы усилителей считывания 1 подключены к входам числового регистра 4. Вход формирователя стробирующего сигнала 3 соединен с выходом дифференцирующего элемента 5, вход которого подключен к выходу ждущего мультивибратора 6. Вход ждущего мультивибратора G соединен с

выходом сумматора 7, первый вход которого подключен к выходу первого эталонного усилителя 8. Выход второго эталонного усилителя считывания 8 подключен к входу инвертора 9, выход которого соединен с вторым входом сумматора 7„ Входы перзый и второй сумматора 7 соединены с разрядносчитьшаюшими 10 и 11 эталонны/; числовых линеек накопителя.

При считывании сигнал вместе с помехой поступает по разрядко-считывающим щинам 2 числовых линеек нако .пителя на первые входы усилителей считьшания 1. Одновременно по разрядно-считывающим щинам 10 и 11 эталонных числовых линеек накопителя подаются эталонные сигналы 1 и О на входы эталонных усилителей считывания 8. С выхода одного из них сигнал через инвертор 9, а с другого непосредственно, подается на первый и второй входы сумматора 7,

Выходной сигнал с сумматора 7 запускает ждущий мультивибратор 6, с выхода которого сигнал поступает на ди{)ференшфующий элемент 5. Далее полученный сигнал поступает на вход формирователя стробирующего сигнала 3, с выхода которого импульс

стробирования поступает на вторые входы усилителей считьшания 1,

Помехозащищенность устройства по вышена за счет организации плавающего стробирования. Эту организицию позволяет осуществить введение инвертора, сумматора, ждущего мультивибратора и дифференцирукдцего элемента. Временная селекция сигнала считывания осуществляется не по эталонному сигналу считьшания 1, а по разностному сигналу, то есть по разности эталонного сигнала считывания 1 и эталонного сигнала считывания О. За счет этого исключается или уменьшается влияние помехи, наложенной на эталонный сигнал считьшания 1, на время запуска формирователя стробирующего сигнала 3, так как помехи, поступивщие

на входы эталонных усилителей считы вания 8 с разрядно-считывающих щин 1О и 11 эталонных числовых линеек накопителя самоподавляются в сумматоР® Временная селекция сигнала считывания осуществляется по переднему фронту импульса, полученного с ждущего мультивибратора 6, после его дифференцирования на дифференцирующем

элементе 5, После ди(ферен цирования

импульса ждущего мультивибратора и его формирования с помощью формирова теля стробирующего сигнала 3, сигнал стробирования поступает на вторые входы усилителей считывания 1, с выходов которцх информационные сигналы поступают на входы числового регистра 4.

Формула изобретения

40

Устройство для считывания ции из накопителя, содержащее усилители считывания, одни входы которых подключены к разрядно-считывающим шинам числовых линеек накопителя, другие - к выходу формирователя стробирующего сигнала, а выходы усилителей считьтания подключены к входам числового регистра, эталонные усилители счи- тьюания, подключенные к разрядносчитьшающим шинам эталонных числовых линеек накопителя, отличающееся тем, что, с целью повьпиения помехозащищенности устройства, в него введены инвертор, сумматор, ждущий мультивибратор и дифференцирующий элемент, выход которого подключен к входу формирователя стробируюшего сиг- нала, а вход - к выходу ждущего мультивибратора, вход которого соединен с выходом сумматора, первый вход которого подключен к выходу первого эталонного усилителя считьшания, а второйк выходу инвертора, вход инвертора соединен с выходом второго эталонного усилителя считьшания. 6643 5 46 Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 410454, кл. fill С 7/02, 1974. 2,Авторское свидетельство СССР № 622167, кл. G11 С 7/ОО, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НАКОПИТЕЛЕЙ ИНФОРМАЦИИ | 1973 |

|

SU409296A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Полупостоянное запоминающее устройство | 1982 |

|

SU1049976A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Запоминающее устройство | 1979 |

|

SU824304A1 |

| Запоминающее устройство | 1975 |

|

SU590823A1 |

| Запоминающее устройство | 1980 |

|

SU892475A1 |

| Формирователь импульсов тока для запоминающих устройств | 1970 |

|

SU449520A3 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

Авторы

Даты

1981-09-15—Публикация

1980-03-03—Подача