1

Изобретение относится к автоматике и технике управления, и может быть использовано для передачи информации в каналах связи.

Известен дешифратор, используемый в системе телеуправления,содержащий регистры, триггеры, элементы И П.

Недостатком известного дешифратора является сложность конструкции.

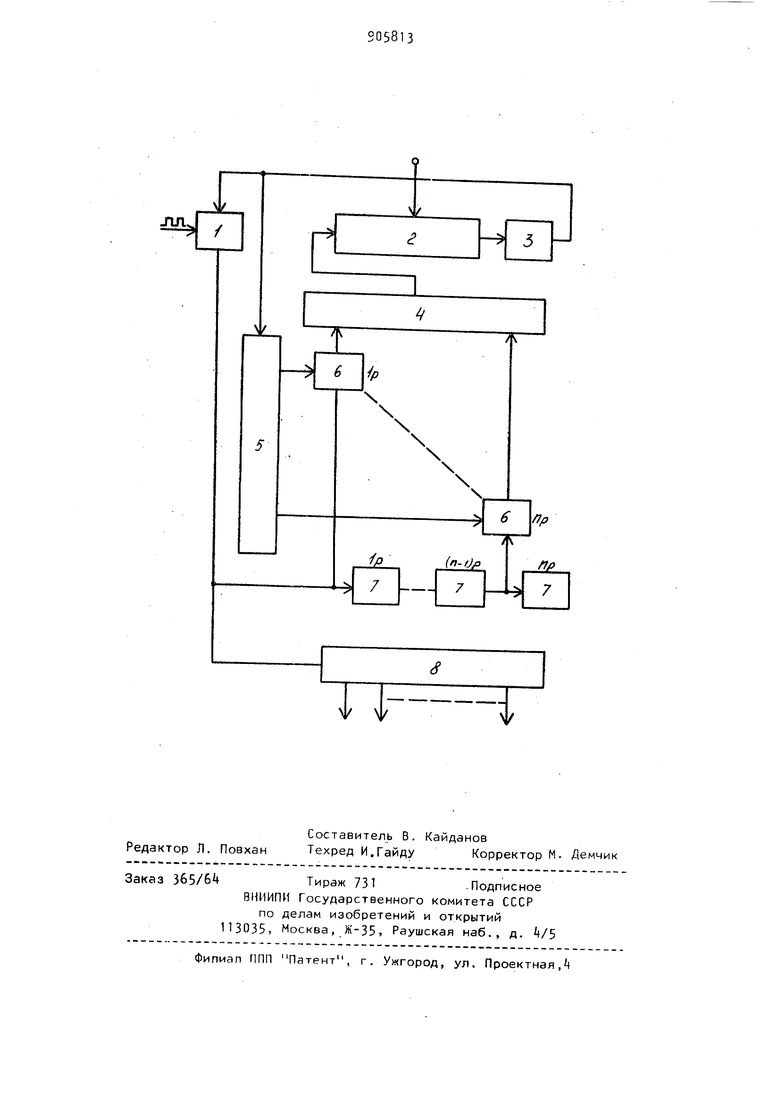

Наиболее близким по технической сущности к предлагаемому является дешифратор, содержащий двоичный счетчик, сдвиговый регистр,первый , второй и третий элементы И, триггер, группу из п регистров (п - число десятичных разрядов в представлении номера дешифруемой команды),группу из п двоичных счетчиков, группу элементов И, входной распределитель импульсов, элемент И конца дешифрации, первый вход первого элемента И является входом устройства, выход, сдвигового регистра является выходом устройства, второй вход первого элемента И соединен с выходом триггера, выход первого элемента И соединен со входом триггера, первый вход второго элемента И соединен со входом устройства, выход второго элемента И с первым входом третьего элемента И, второй вход которого соединен с выходом элемента И конца дешифратора, входы которого соединены с выходами соответствующих элементов И группы, первые входы которых соединены с выходами соответствующих регистров группы, а вторые входы с выходами соответствующих двоичных счетчиков группы, входы регистров группы соединены с соответствующими п выходами входного распределителя импульсов, (п+1)-й выход которого соединен со вторым входом второго элемента И, вход входного распределителя импульсов соединен с выходом первого элемента И, выход третьего элемента И соединен со входом сдвигового регистра и со вхо3дом первого двоичного счетчика груп пы, вход i-ro двоичного счетчика группы (,3,...,п) соединен с выходом (i-l)-ro двоичного счетчика группы. В двоичный счетчик записывается п-разрядное дешифрсзванное двоичное число последовательно, поразрядно, начиная со старшего разряда Импульсная последовательность со входа через первый и второй элементы И поступает на счетный вход двои ного счетчика и через распределител импульсов на регистры группы. Когда входной распределитель импульсов за полнит все 11 регистров группы, начиная с 11 до 1 , открывается третий элемент И, и импульсная последовательность со входа дешифратора поступает на вход счетчиков группы. При последовательном заполнении счетчиков группы балансируются соответствующие элементы И группы, и когда они сбалансируются, на выход элемента И конца дешифрации сформируется сигнал управления, закрывающий третий элемент И. Положение импульса в этот момент в сдвиговом регистре соответствует номеру переданной командь i2. Недостатком такого дешифратора является наличие группы из п регист ров, где дешифруемое число поразряд но запоминается на время от начала цикла дешифрации до момента,когда открывается третий элемент И, и импульсная последовательность посту пает на вход счетчиков группы и одновременно в сдвиговый регистр. При этом время дешифрации равно сумме времени заполнения группы из п регистров и времени заполнения счетчи ков группы. Целью изобретения является упрощение и повышение быстродействия дешифратора. Поставленная цель достигается тем, что дешифратор, содержащий эле мент )-i, счетчик, триггер, первый сд говый регистр, группу из п последовательно соединенных счетчиков, группу из п элементов И, вь1ход элемента И соединен с входом первого счетчика группы и входом первого сдвигового регистра, вйход счетчика соединен с входом триггера, выходы разрядов первого сдвигового регистр являются выходами дешифратора,дополнительно содержит элемент ИЛИ 34 и второй сдвиговый регистр,причем первый вход элемента И подключен к шине тактовой частоты дешис ратора. а второй вход подключен к выходу триггера и входу второго сдвигового регистра, первые входы элементов И группы подключены к входам счетчиков группы соответственно, выходы разрядов второго сдвигового регистра соединены со вторыми входами эле ментов И группы соответственно, выходы которых соединены с выходами элемента к1ЛИ, выход которого соединен со счетным входом счетчика, входы разрядов которого подключены к входам записи информации дешифратора. На чертеже представлена блоксхема дешифратора. Схема содержит элемент И 1, счетчик 2, триггер 3, элемент ИЛИ 4, сдвиговый регистр 5, группу элементов И 6, группу счетчиков 7 и сдвиговый регистр 8. Устройство работает следующим образом. В счетчик 2 записывается л-разрядное дешифрируемое число последовательно, поразрядно, наминая со старшего разряда. В исходном состоянии элемент И 1 открыт,на выходе п сдвигового регистра 5 разрешающая 1 и последний элемент И 6 группы открыт. Импульсная последовательность со входа через элемент И 1 поступает на вход первого из группь счетчиков 7, одновременно на вход сдвигового регистра 8. Начинает перемещаться 1 на выходах сдвигового регистра 8, и заполняется счетчик 7 группы. В момент записи первого импульса в п-ый счетчик 7 группы через последний (п-ый) элемент И 6 группы и элемент ИЛИ i этот импульс поступает в счегчик 2. В момент записи следующего импульса в п-ый счетчик 7 группы через ту же цепочку: 11-ый элемент И 6 группы и элемент ИЛИ , - импульс снова заносится в счетчик 2.8 момент переполнения счетчика 2 с него поступает импульс на триггер 3) который запрещает прохождение импульсов через элемент И 1 и вызывает сдвиг, разрешающий 1 сдвиговом регистре 5. Затем в счетчик 2 записывается число разряда меньшего на единицу. Аналог:-1чно вышеизложенному через открытый элемент И 6 группы и элемент ИЛИ 4 импульсы с выхо5да (п-2)-го счетчика 7 группы поступают на входы сметчика 2. В момент его переполнения триггер 3 закрывает элемент И 1 и вызывает очередной сдвиг 1 в сдвиговом регистре 5При записи в счетчик 2 последнег младшего разряда дешифруемого числа импульсная последовательность с вых да элемента И 1 поступает на вход первого счетчика 7 группы, сдвигового регистра 8 и через первый элемент К 6 группы и элемент ИЛИ А в счетчик 2. При переполнении счетчика 2 триггер 3 закрывает элемент 1 и устанавливает регистр 5 в исход ное состояние. Положение импульса 8 этот момент в сдвиговом регистре 8 соответствует номеру переданной команды. По сравнению с известным дешифра тором в предлагаемом отсутствуют два элемента И и группа п регистров Входной распределитель импульсов и элемент И конца дешифрации известно го дешифратора, сдвиговый регистр 5 и элемент ИЛИ k в предлагаемом дешифраторе по числу применяемых при их построении элементов одинаковы. В образце дешифратора по схеме известного для дешифрации двухразрядных десятичных чисел с общим числом команд 99 применено 26 микро схем. А в предлагаемом дешифраторе на то же число команд применено только k микросхем. Такая разница объясняется не только отсутствием 2-х регистров группы, но и значительным уменьшением числа элементов К группы. Так в известном дешиф раторе для каждого счетчика группы необходимо четыре (по числу разрядо счетчика) элемента И, для двух счетчиков - всего 8. Тогда как для предлагаемого дешифратора необходиМО только 2-элемента И. Кроме того, время дешифрации пре лагаемого дешифратора меньше, чем у известного на величину времени от 3 начала цикла дешифрации до момента, когда в сдвиговый регистр начинает поступать импульсная последовательность, т.е. на время поразрядной записи дешифрированного числа в группу из п регистров. Формула изобретения Дешифратор, содержащий элемент И, счетчик, триггер, первый сдвиговый регистр, группу из г последовательно соединенных счетчиков, группу из п элементов И, выход элемента И соединен с входом первого счетчика группы и входом первого сдвигового регистра, выход счетчика соединен с входом триггера, выходы разрядов первого сдвигового регистра являются выходами дешифратора, отличающийся тем, что, с целью упрощения и повышения быстродействия, дешифратор содержит элемент 1|ПИ и второй сдвиговый регистр, примем первый вход элемента И подключен к шине тактовой частоты дешифратора, а второй вход подключен к выходу триггера и входу второго сдвигового регистра, первые входы элементов И группы подключены к входам счетчиков группы соответственно, выходы разрядов второго сдвигового регистра соединены со вторыми входами элементов И группы соответственно, выходы которых соединены с входами элемента ИЛИ,выход которого соединен со счетным входом счетчика, входы разрядов которого подключены к входам записи информации дешифратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Г , кл. Г, 06 Г 5/02,.. 2.Авторское свидетельство СССР f; , кл. G 06 Г 5/02, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1977 |

|

SU744547A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1554153A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Устройство для ввода информации | 1982 |

|

SU1068927A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Авторы

Даты

1982-02-15—Публикация

1980-04-30—Подача