ного сигнала соединен с выходом элемента НЕ, а его информационный вход подключен к выходу регистра абсолютного значения приращения спорного сигнала, вход разрешения записи которого соединен с входом элемента НЕ и с выходом элемента И блока управления сменой кода опорного сигнала, а вход записи - с выходом делителя частоты, вход делителя частоты подключен к выходу параллельно-Последовательного сумматора блока формирования опорного сигнала, ко входу регист ра начального значения опорного сигнала и входу первого регистра блока вычисления шага квантования, установочные входы первого суммирующего счетчика и второго регистра которого

подсоединены к выходу переключателя, вход коммутатора, подключен к генератору импульсов, а его четьфе выхода подсоединены соответственно к счетному входу параллельно-последовательного сумматора блока формирования опорного сигнала, счетному входу реверсивного счетчика аналого-цифрового преобразователя, счетному входу реверсивного счетчика блока управления сменой кода опорного сигнала и к счетному входу первого суммирующего. счетчика блока вычисления шага квантования, выход регистра начального значения опорного сигнала соединен с установочным входом параллельно-последовательного сумматора блока формирования опорного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Устройство для линеаризации функций | 1979 |

|

SU864307A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2078302C1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ ПРЕОБРАЗОВАТЕЛЕЙ, содержащее аналого-цифровой преобразователь, состоящий из последовательно соединенных элемента сравнения, реверсивного счетчика и цифро-аналогового преобразователя, вход которого является цифровым выходом устройства, переключатель, входы которого являются входами ввода граничных числовых значений эталонов измеряемых величин устройства, а выход соединен с установочным входом реверсивного счетчика аналогоцифрового преобразователя, генератор импульсов, блок формирования опорного сигнала, состоящий из последовательно включённых параллельно-последовательного сумматора и цифро-аналогового преобразователя, подключенного выходом к аналоговому информационному входу цифро-аналогового . преобразователя аналого-цифрового преобразователя, и блок управления сменой кода опорного сигнала, состоящий- из последовательно включенных реверсивного счетчика, дешифратора и элемента И, подсоединенного выходом ко входу сброса реверсивного счетчика, другой вход элемента сравнения аналого-цифрового преобразователя является аналоговым информационным входом устройства, а его выход подключен ко входам реверса счета параллельно-последовательного сумматора блока формирования опорного сигнала и реверсивного счетчика блока управления сменой кода опорного сигнала, отличающееся тем, что, с целью упрощения устройства, оно содержит коммутатор, регистр начального значения опорного сигнала, де(Л литель частоты, регистр абсолютного значения приращения опорного сигнала, с: элемент НЕ.и блок вычисления шага квантования, состоящий из первого в регистра, первого элемента сравнения, подсоединенного двумя входами соответственно ко входу и выходу первого регистра, первого суммирующего счетчика, второго регистра, вт орого элемента сравнений, подсоединена ного входами соответственно сю к выходам первого суммирукяцего счетчика и второго регистра, элемента И, два входа которого подключены соответственно к выходам первого и второго элементов сравнения, и второго суммирующего счетчика, счетный вход которого соединен с выходом элемен-. та И, а выход подключен к управляющему входу дешифратора блока управления сменой кода опорного сигнала, вход разрешения параллельного суммирования параллельно-последовательного сумматора блока формирования опор

Изобретение относится к вычислительной и преобразовательной технике и может быть использовано для вычисления и коррекции функций линеаризации выходных характеристик изме рительных преобразователей, i

Известны способы и устройства аппроксимации с последующим воспроизведением функциональных зависимостей в основу которых положена теория ; приближения функций ClJ- Эти способы и устройства могут быть эффективно использованы для коррекции выходных характеристик измерительных преобразователей лишь в том случае, если имеется возможность воспроизведения ряда эталонов измеряемой физической величины на входе измерительного преобразователя при вычислении его корректирующей функции, что значительно ограничивает возможность их применения, особенно при необходимости многократных коррекций функций линеаризации выходных характеристик измерительных преобразователей в процессе их эксплуатации.

Наиболее близким по тех1Йвдеской сущности к предлагаемому изобретению является устройство, содержащее измерительный преобразователь, вход Которого через переключающий клапан соединен с входами ввода эталонов измеряемой величины, выход измерительного преобразователя соединен с аналоговым информационным входом аналого-цифрового преобразователя, вход установки цифровых значений эталонов которого соединен через , переключатель с соответствующими входами устройства, цифровой и счетный выходы аналого-цифрового преобразователя соединены с блоком памяти блоком формирования опорного сигнала с блоком разрешения записи, выход которого соединен с управляющим входом блока памяти, выход блока памяти соединен с входом параллельной записи блока формирования опорного сигнала, аналоговый выход которого соединен с входом ввода опорнсГго сигнала аналого-цифрового преобразователя. В этом устройстве корректирующее воздействие на выходную характеристику измерительного преобразователя осуществляют посредством изменения коэффициента передачи аналого-цифрового преобразователя (опорного сигнала) 2.

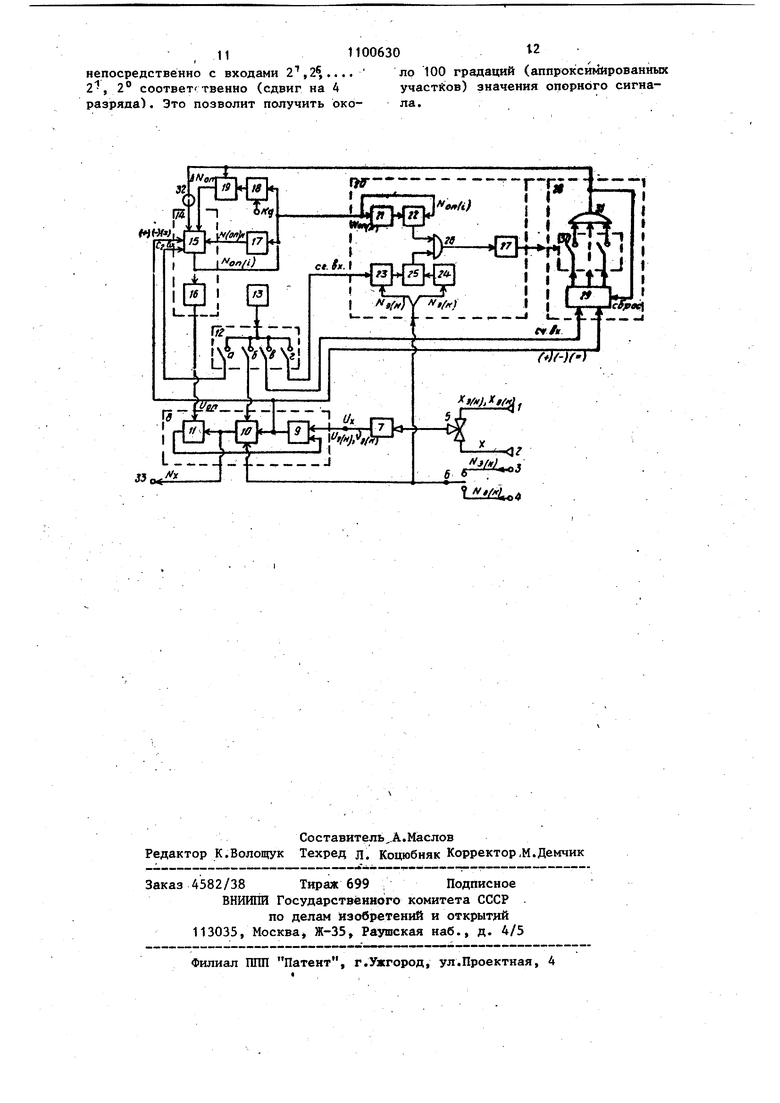

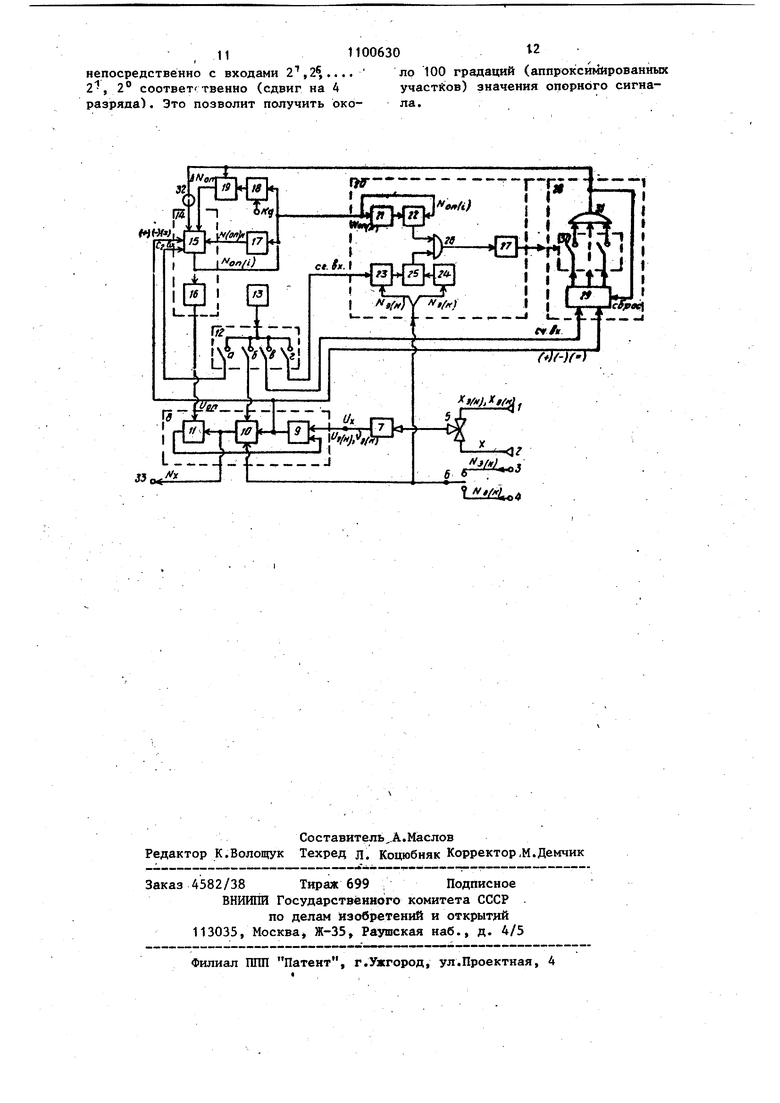

В этом случае вычисление алгоритма, определяющего корректирующую функцию, сопряжено с необходимостью предварительного воспроизведения на входе измерительного преобразователя ряда эталонов измеряемой величины. Кроме того, для хранения корректирующей функции необходим значительный объем памяти.. Цель изобретения - упрошение устройства путем сокращения требуемого объема памяти. Поставленная цель достигается тем что устройство для коррекции характеристик измерительньк преобразователей, содержащее аналого-цифровой преобразователь, состоящий из последовательно соединенных элемента сравнения, реверсивного счетчика и цифро-аналогового преобразователя, вход которого является цифровым выхо дом устройства, переключатель, входы которого являются входами ввода граничных числовых значений эталонов измеряемых величин устройства, а выход соединен с установочным входом реверсивного счетчика аналого-цифрового преобразователя, генератор импульсов, блок формирования опорного сигнала, состоящий из последовательно включенных параллельно-последовательного сумматора и цифро-аналогово го преобразователя, подключенного выходом к аналоговому информационному входу цифро-аналогового преобразователя аналого-цифрового преобразователя, и блок управления сменой кода опорного сигнала, состоящий из последовательно включенных реверсивного счетчика, дешифратора и элемента И, подсоединенного выходом ко входу сброса реверсивного счетчика, другой вход элемента сравнения анало го-дифрового преобразователя является аналоговым информационным входом устройства, а его выход подключен ко входам реверса счета параллельно-последовательного сумматора блока формирования опорного сигнала . и реверсивного счетчика блока управления сменой кода опорного сигнала, содержит коммутатор, регистр начального значения опорного сигнала, делитель частоты, регистр абсолютного значения приращения опорного сигнала, элемент НЕ и блок вычисления шага квантования, состоящий из первого регистра, первого элемента срав нения, подсоединенного двумя входами соответственно ко входу и выходу первого регистра, первого суммирующ го счетчика, второго регистра, втор го элемента сравнения, подсоединённого двумя входами соответственно к выходам первого суммирующего счет чика и второго регистра, элемента И, два входа Которого подключены соответственно к выходам первого и второго элементов сравнения, и второго суммирующего счетчика, счетный вход которого соединен с выходом элемента И, а выход подключен к управляющему входу дешифратора блока управления сменой кода опорного сигнала, вход разрешения параллельного суммирования паралл ельно-последователького сумматора блока формирования опорного сигнала соединен с выходом элемента НЕ, а его информационный вход подключен к выходу регистра абсолютного значения приращения опорного сигнала, вход разрешения записи которого соединен с входом элемента НЕ и с выходом элемента И блока управления сменой кода опорного сигнала, а вход записи - с выходом делителя частоты, вход делителя частоты подключен к выходу параллельнопоследовательного сумматора блока формирования опорного сигнала, ко входу регистра начального значения опорного сигнала и входу первого регистра блока вычисления шага квантования, установочные входы первого суммирующего счетчика и второго регистра которого подсоединены к выходу переключателя, вход коммутатора подключен к генератору импульсЬв, а его четыре выхода подсоединены соответственно к счетному .входу параллельно-последовательного сумматора блока формирования опорного сигнала, счетному входу реверсивного счетчика аналого-цифрового преобразователя, счетному входу реверсивного счетчика блока управления сменой кода опорного сигнала и к счетному входу первого суммирующего счетчика блока вычисления щага квантования, выход регистра начального значения опорного сигнала соединен с установочным входом параллельнопоследовательного сумматора блока формирования опорного сигнала. На чертежеЪриведена блок-схема, устройства. Устройство и относящиеся к нему блоки содержат входы 1 - 4 ввода эталонов , X j( измеряемой величины X и числовых значений эталонов , N-j, переключатель (переключающий клапан) 5, переключатель 6, измерительный преобразователь 7, 51 аналого-цифровой преобразователь 8, элемент сравнения 9, реверсивный счетчик 10, цифро-аналоговый преобразователь 11, коммутатор 12, генератор импульсов 13, блок 14 формирования опорного сигнала, параллельнопоследовательный сумматор 15, цифроаналоговый преобразователь 16, регистр 17 начального значения опорного сигнала, делитель частоты 18, регистр 19 абсолютного значения приращения опорного сигнала, блок 20 вычисления шага квантования, первый регистр 21, первый элемент сравнения 22, первый суммирующий счетчик 23, второй регистр 24, второй элемент сравнения 25, элемент И 26, второй суммирующий счетчик 27, блок 28 управления сменой кода опорного сигнала, реверсивный счет- чик 29, дешифратор 30, элемент И 31, элемент НЕ 32, выход устройства 33. На чертеже и в тексте имеются следующие обозначения; (-) (-)() входы управления реверсом и останова счета; )(«| измеряемая величина и ее эталоны, соответствую щие граничным значения диапазона измерения; аналоговые и циф (Н)(К| (Н| Э(К) ровые значения измеряемой и эталонных величин:приращение опорОГ7 (П к ного сигнала при переходе с -го на (t +1)-й дискретный уровень; коэффициент деK,const А ления текущего значения опорного сигнала; (HL const количество дисANyкретных уровней (шагов квантования) опорного сигнала; значения постоян dNv const ного шага кванто вания по измеряе мой величине; (K,t1) -N . Non(M) Кд on(Ht t 0 «-Кд+Кт м -ы %n(k| ОП(И) V АN3((H) первый Входами являются и второй входы 1 и .2 ввода эталонов , Хз(к) , соответствующих граничным значений диапазона измерения и ввода измеряемой величины X, третий и четвертый входы 3 и 4 ввода числовых значений Njj, , N3(10 эталонов Х,., Xji, соответственно. Первый и второй входы 1 и 2 через переключающий клапан, а третий и четвертый входы 3 и 4 через переключатель 6 соединены соответственно с входом измерительного преобразователя 7 и с входом установки граничных значений диапазона измерения аналого-цифрового преобразователя 8, аналоговый информационный вход которого соединен с выходом измерительного преобразователя 7. В аналого-цифровой преобразователь 8 включены последовательно соединенные аналоговый элемент сравнения 9, один вход которого является аналоговым информационным- входом устройства и соединен с выходом измерительного преобразователя 7 , реверсивный счетчик 10 и цифро-аналоговый преобразователь 11, выход которого соединен с вторым входом аналогового элемента сравнения 9, Счетный вход аналого-цифрового преобразователя 8, счетный вход счетчика 10 соединены через коммутатор 12 с генератором импульсов 14, а вход ввода опорного сигнала с аналоговым выходом блока 14 формирования опорного сигнала, включающего в себя последовательно параллельно-последовательный соединенные сумматор 15 и цифро-анало- говый преобразователь 16. Цифровой выход блока 14 соединен через регистр 17 начального значения опорного сигнала Nj со своим входом установки , а также через делитель частоты 18 и регистр 19 абсолютного значения л N ofi приращеНИН опорного сигнала соединен с входом параллельного суммирования. Кроме того, цифрово й выход блока 14 (выход сумматора 15) соединен с входом ввода конечного и текущего значений Njjn, Npn,jonopHoro сигнала блока 20 вычисления шага квантования ЛЫ. В блок 20 включены: первый регистр 21 конечного значения Nonj,, опорного сигнала, выход которого со динен с одним v OROM первого цифрового элемента сравнения 22, второй вход цифрового элемента сравнения 2 и вход регистра 21 соединены с первым входом ввода конечного и текуще го значений оп{к Non(i) блока 20; первый суммирующий счетчик 23 и вто рой регистр 24 конечного эначения диапазона измерения, выходы которых соединены с входами второго цифрового элемента сравнения 25, а входы ввода граничных значений Nj/,. Nj.i диапазона измерения счетчика 23 и второго регистра 24 (третий вход 6(лока) соединены переключателем 6; первого и второго циф ровых элементов сравнения 22 и 25 через элемент И 26 соединены с входами второго суммирующего счетчика для управления перебором значений шага квантования, вькод которого соединен с соответствующим входом блока 28 управления сменой кода опо ного сигнала. В блок 28 включены последовательно соединенные реверсивный, счетчик 29, дешифратор 30, представляющий собой набор управляемых ключей, и элемент И 31, выход которого соединен с выходом бло ка 28 и с входом Сброс реверсивного счетчика 29. Выход элемента И 31 блока 28 управления сменой кода опорного сигнала соединен с вх дом разрешения записи регистра 19 абсолютного значения приращения параллельного, суммирования блока 14 Формирования опорного сигнала. Полу ченное числовое значение N опорного сигнала Ujniui аналого-цифрового преобразователя 8, при котором он находится в равновесии при введенном значении кода в его счетчик 10, запоминают в регистре 1 Через переключатель 6 с выхода 4 в счетчик 10 аналого-цифрового преобразователя 8 и в регистр 24 блока 20 вводят числовое значение Nj,. эталона, соответствукядегр концу диапазона измерения; в измерительный преобразователь 7 с выхода 1 через переключающий клапан 5 вводят соответствующий концу диапазона измерения эталон Х.. измеряемой величины X. Аналогично описанному определяют конечное значение. N j. опорного сигнала и запоминают его в регистре 21 блока 20 вычисления шага квантования. Затем определяют такое постоянное значение iNj.raara квантования (сос тояние связей в дешифраторе 30), при котором изменение кода в счетчике 10 аналого-цифрового преобразователя 8 на величину ANj( сопровождалось бы изменением опорного сигнала в соответствии-с выражением (2). Задаются постоянным относительным приращением опорного сигнала: 4N , е.щил, ол(отн| N т.е постоянным коэффициентом деления K const текущего цифрового значения NQ|.,rjjопорного сигнала, формируемого на выходе сумматора 15; устанавливают значение Кд в делителе частоты 18 ..(для упрощения вычислений коэффициент деления К выбирак т ратным системе счисления, например, 2...,.тогда делитель частоты 18 и регистр 19 можно заменить одним сдвиговым регистром). В сумматор 15 из регистра 17 вводят начальное значение Nj,опорного сигнала; в дешифраторе 30 с помощью с пммирующегр счетчика 27 устанавливают связи между выходами реверсивного счетчика 29 и входами элемента И 31 блока-28 таким образом, чтобы на выходе элемента И 31 формировался управлякяций сигнал при заполнении реверсивного счетчика 29 до начального минимального значения x(min) (диапазоном возможных значений ЛН(, -ДМ(„у, задаются ориентировочно); замыкают ключи 12в, 12г, при этом счетные импульсы поступают в счетчик 23 блока 20 и в счетчик 29 блока 28. Значения кодов в счетчиках 23 и 29 последовательно нарастают от N до от до Njjr.j. соответственно. Всякий раз при достижении в счетчике 29 кода значения ,. на. выходе элемента И 31 формируется сигнал,, сбрасьшающйй показания счетчика 29. Этот же сигнал с выхода блока 28 управления сменой кода опорного сигнала даст разрешение на запись в регистр 19 значения 4N , которое после исчезновения управляющего сигнала перепишется (просуммируется) в сумматор 15, т.е. на выходе инвертора 32 появится соответствующий сигнал разрешения суммирования «огг(II on(И) (1) При вторичном заполнении реверсивного . счетчика 29 до значения /iNx(miti) вновь формируется управляющий сигнал на выходе элемента И 31, в результате чего в регистр 19 записывается новое значение п(2) к o opos после исчез новения управляющего сигнала с выхода блока 28 и восстановления егй на выходе элемента НЕ 32 просуммируется в сумматоре 15 Nof,, оп,,+ (2| Я- Одновременно текущие значения , поступают на второй вход первого элемента сравнения 22 где их сравнивают с конечным значением Ngjj,|. , хранимым в регистре- 21, Неодновремейное достижение в сумматоре 15 конечного значения Ng ,| и в счетчике 23 конечного зна чения N ,. свидетельствует о том, что первое выбранное значение xtiTiin} х(1) удовлетворяют усл виям (1,2), в результате выходным сигналом суммирующего счетчика 27 в блоке 2 устанавливают новое зна чение aNj(/2) сумматоре 15 и в счетчике 23 вновь устанавливают начальное значение NQ,,., ,), после чего аналогично формирзтот N -N (Н)(К| проверяя . ,.., ..., , 9(Н| (М на соответствие значение Ли,12|И т. Наконец, при каком-то значении dN одновременно в. сумматоре 15 и в сч чике 23 сформируются конечные ОП(К) Э(К) значения N в результате одновременного появления на вькода узлов сравнения 22 и 25 сигналов, на выходе элемента И 26 сформирует ся сигнал, прекращающий процесс управления перебором в сумми рующем счетчике 27 значений х(1) коммутационные связи в дешифраторе 30 фиксируются. Далее в сумматоре 15 блока 14 формирования опорного сигнала и счетчике 10 аналого-цифрового преобразователя 8 устанавливают на чальные значения .и соответственно. С выхода 2 через переключающий клапан 5 на вход измерительного преобразователя 7 подают измеряемую физическуй величи,ну X. Замыкают ключи 12 и 12, . аналого-цифровой преобразователь пе реводится в режим следящего уравновещивания. При разбалансе сигналов на входах элемента сравнения 9 счет чики 10 и 29 заполняются -счетными импульсами, причем, с каждой вновь поступающей или считанной пачкой импульсов счетчик 29 обнуляется, в результате чего в соответствии с выражениями (1,2), изменяется значение опорного сигнала в диапа ° бгцнГ «п кг .Таким образом, в зависимости от .значения измеряемой величины X .автоматически устанавливается необходимый коэффициент аналого-цифрового преобразования, учитывающий нелинейность измерительного преобразователя. Предложенное устройство обеспечивает определение функции коррекции выходной характеристики измерительного преобразователя по двум эталонам, что применительно, например, к газоаналитическим системам (это позволяет в 3-4 раза сократить расход дорогостоящих поверочных газовых смесей); простоту вычисления И последующего воспроизведения корректирующей функции: алгоритм формирования опорного сигнала, реализованный в устройстве, позволяет выполнять линеаризацию выходных характеристик измерительных преобразователей , X как с линейно изменяющимся коэффициентом передачи Kj, так и с коэффициентом передачи, изменяющимся по закону, близкому к экспоненциальному, что особенно существенно для подавляющего больщинства датчиков анализа и состава вещества, в частности, для газоанализаторов . Предлагаемое устройство является простым, так как функции блока памяти вьшолняют дещифра- тор 30, представляющий собой п ключей (по числу разрядов счетчика 29, ns;2- 2), и делитель 18 с регистром 19. Для диапазона изменения опорного сигнала, например, оп((кГ2°-2. .диапазона измеряемой величины -2 , с учетом рекомендуемого значения /iNpj,,Q. 1-5% и выбрав одно из значений ; 2 ; 2, получим, соответстенно 210; 100; 5; 10; т.е., например, для , ДНл1,0 остаточно ограничиться 4-разрядным воичньм счетчиком 29, а выходы 2, i .... 2 , 2 сумматора 15, минуя делитель частоты 18, соединить

111100630 2

непосредственно с входами 2,2,....- по 100 градаций (аппроксимированных 2, 2° соответственно (сдвиг на А участков) значения опорного сигнаразряда). Это позволит получить око- ла.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексеев Г.И.Воспроизведение функций средствами цифро-аналоговой вычислительной техники | |||

| Минск, 1976, с | |||

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для линеаризации функций | 1979 |

|

SU864307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1984-06-30—Публикация

1982-07-02—Подача