(54) ЛОГАРИФМИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU930650A2 |

| Аналого-цифровой преобразователь | 1979 |

|

SU879770A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Многоканальный логарифмическийАНАлОгО-цифРОВОй пРЕОбРАзОВАТЕль | 1979 |

|

SU824229A1 |

| Аппаратура акустического каротажа нефтяных и газовых скважин | 1980 |

|

SU898369A1 |

| Аналого-цифровой амплитудный детектор | 1990 |

|

SU1742985A1 |

Изобретение относится к области автоматики и вычислительной техНИКИ и может быть использовано для вычисления логариф1 в1ческих Функций в различных аналого-цифровых уст ройствах обработки измерительной информации . Известно аналого-цифровое логариф мирующее устройство, содержащее Йлок , сравнения, блок выделения модуля с регулирующей зоной нечувствительност нуль-орган, преобразователь напряжение-частота, блок нелинейного цифроаналогового преобразователя в реверсивный счетчик l. Известно также логарифмирующее ус ройство, содержащее регистр памяти, блок вычисления характеристики, регистр сдвига, доиифратор и регистр результата С2. Общим недостатком известных устройств - низкая точность логарифмического преобразования, Наиболее близким к предлагаемому по технической сущности является лог рифмирующее устройство, содержащее регистр Пс№1яти, основной счетчик, элемент ИЛИ, дешифратор, подключен ный выходами к входам блока априорной памяти, и блок вычисления харак теристики, вход которого соединен с инфОЕ 4ационным входом регистра сдвига, а выход - с управляющим входом регистра сдвига и с первым входом регистра результата, подключенного вторым входом к выходу блока априорной памяти, причем основной соединен цифровым выходом с входами дешифратора, входами установки кода - с цифровым выходом регистра сдвига, а счетным входом - с выходом элемента ИЛИ, подключенного вхоДс1ми к выходам группы элементов И, соединенных первыми входами с выходом блока вычисления характеристики а вторыми входами. - с входг ш блока вычисления характеристики и с выходеили регистра памяти, информационный вход которого соединен с цифровым входом устройства и с информационным входом регистра сдвига fs. Недостаток устройства - низкая точность логарифмического преобраэо вания, которую можно повысить тофко эа счет значительного увеличения аппаратурных затрат (путем увеличения объела блока априорной памяти и дешифратора). Цель изобретения - повышение точности преобразования.

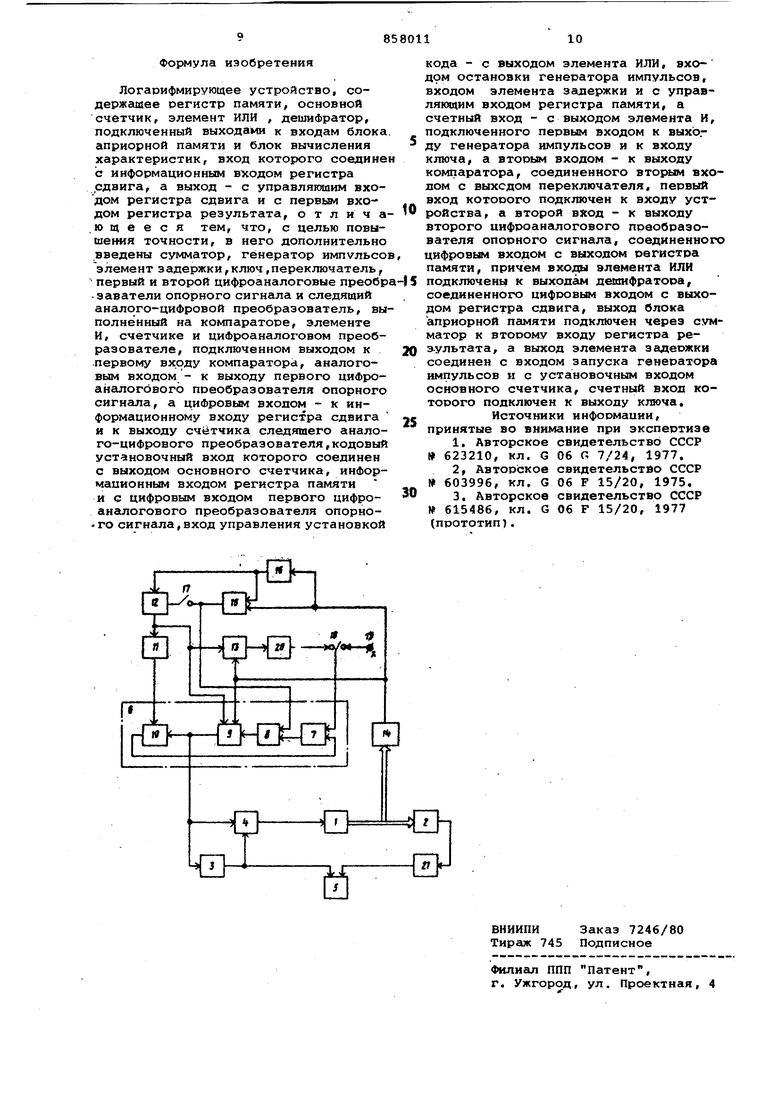

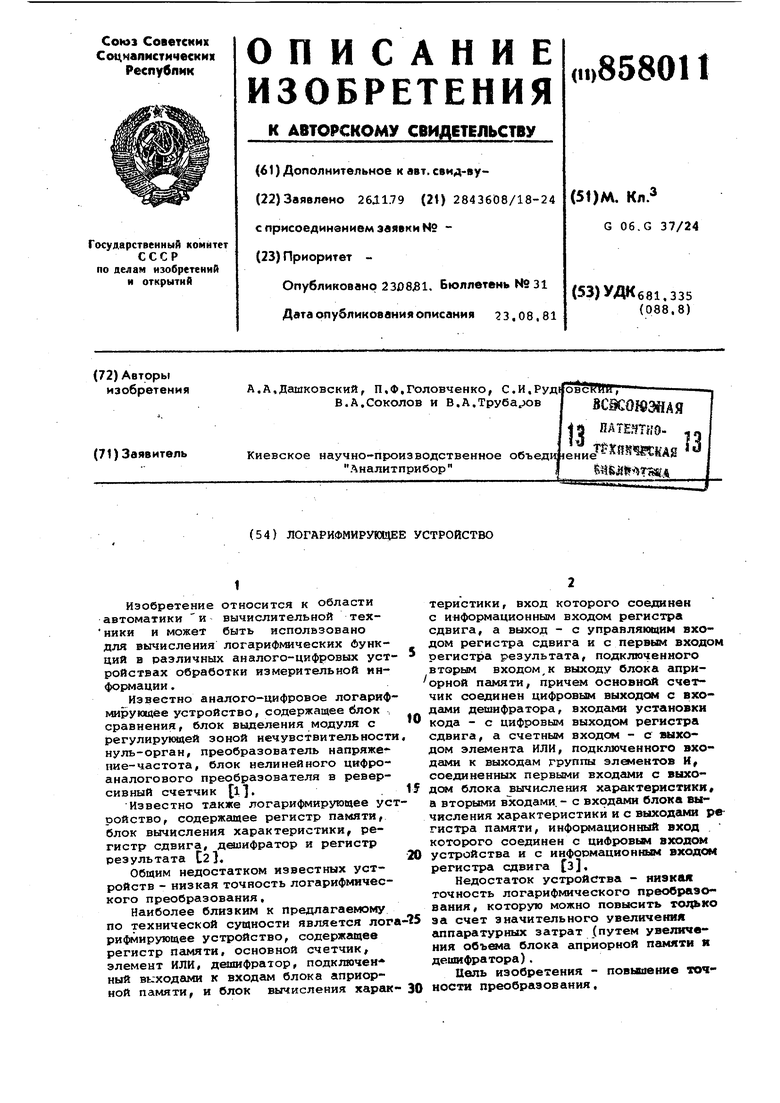

С ЭТОЙ целью в логарифмирующее устройство, содержателе регистр памяти, основной счетчик, элемент ИЛИ, дешифратор, подключенный выходами к входам блока априорной памяти, и блок вычисления характеристики, вход которого соединен с информационным входом регистра сдвига, а выход с управляющим входом регистра сдвига и с первым входом регистра результата, дополнительно введены сумматор, гене ратор импульсов, элемент задержки, ключ, переключатель, первый и второй цыфроаналоговые преобразователи опорного сигнала и следящий аналого-цифровой преобразователь, выполненный на компараторе, элементе И, счетчике и цифроаналоговом преобразователе, подключенном выходом к первому входу компаратора,аналоговыгл входом к выходу первого цифроаналогового преобразователя опорного сигнала, а цифровьпу входом - к информационному входу регистра сдвига и к выходу счетчика следящего аналого-цифрового преобразователя, кодовый установочный вход которого соединен с выходом основного счетчика, информационным входом регистра памяти и с цифровым входом первого цифроаналогового преобразователя опорного сигнала, вход управления установкой кода - с выходом элемента ИЛИ, входом остановки генератора импульсов, входом элемента задержки и с управлянидим входом регистра памяти, а счетньй вход - с выходом элемента И,подключенным первым входом к выходу генератора импульсов и к входу ключа, а вторым входом - к выходу компаратора, соединенного вторым входом с выходом переключателя, первый вход которого подключен к входу устройства, а второй вход - к выходу втор гo цифроана логового преобразователя опорного сигнала, соединенного цифровым входом с выходом регистра памяти, причем входы элемента ИЛИ подключены к выходам дешифратора, соединенного цифровым входом с выходом регистра сдвига, выход блока априорной памяти подключен через сумматор к второму входу регистра результата, а выход . элемента задержки соединен с входом запуска генератора импульсов и с установочным входом основного счетчика, счетный вход которого подключен к выходу ключа.

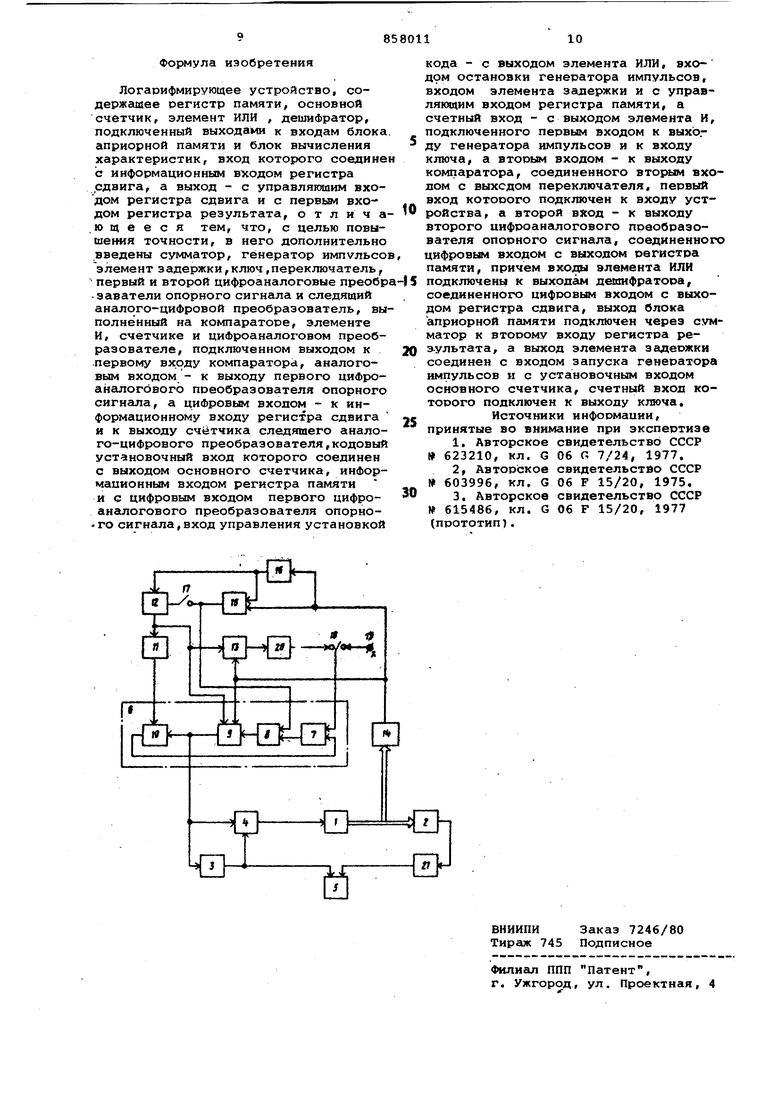

На чертеже изображена блок-схема логарифмирующего устройства, содержащего дешифратор 1, подключенный выходами у входам блока 2 априорной памяти, блок 3 вычисления характеристики, вход которого соединен с информационным- входом регистра 4 сдвига, а выход - с управляющим входом регистра 4 сдвига и с первым входом регистра 5.результата, следящий аналого-цифровой преобразователь

6,выполненный на компараторе 7, элементе И 8, счетчике 9 и цифроанало говом преобразователе 10, Преобразователь 10 подключен выходом к первому входу компаратора 7, аналоговым входом - к выходу первого цифроанзлогового преобразователя 11 опорного сигнала, а цифровым входом - к информационному входу регистра 4 сдвига и к выходу счетчика 9, Счетчик 9 соединен кодовым установочным входом

: выходом основного счетчика 12, информационным входом регистра 13 памяти и с цифровым входом первого преобразователя 11, входом управления , установкой кода - с выходом элемента ИЛИ 14, входом остановки генератора 15 импульсов, входом элемента 16 задержки и с управляющим входом регистра 13 памяти, а счетный вход - с выходом элемента И 8. Элемент И 8 подключен первым входом к выходу генератора 15 и к входу ключа 17, а вторым входом - к выходу компаратора

п выходов, соответствующих значениям входных чиселМ |Л2),(),,.. которые соединены с входами- блока 2 таким образом, что каждому из них соответствует ячейка памяти значений мантисс М ,М ,.,.М логарифмов

чисел eciefaU 2V-, («. соответственно.

Для пояснения работы устройства использ-уются следующие обозначения и расчетные выражения:

XrUbiN,соответственно значения аналоговых величин входного сигнала и опорного сигнала и их цифровых эквивалентов}

М соответственно емг WOK кости счетчиков 9 и 12 и регистра 137

0 t, соответственно нао.р чальный опорный сигнал и его значения на первом,...и р-ом этапах аналого-цифрового преобразования.

дискретность аналогоцифрового преобразования на i-OM этапе вычисления.

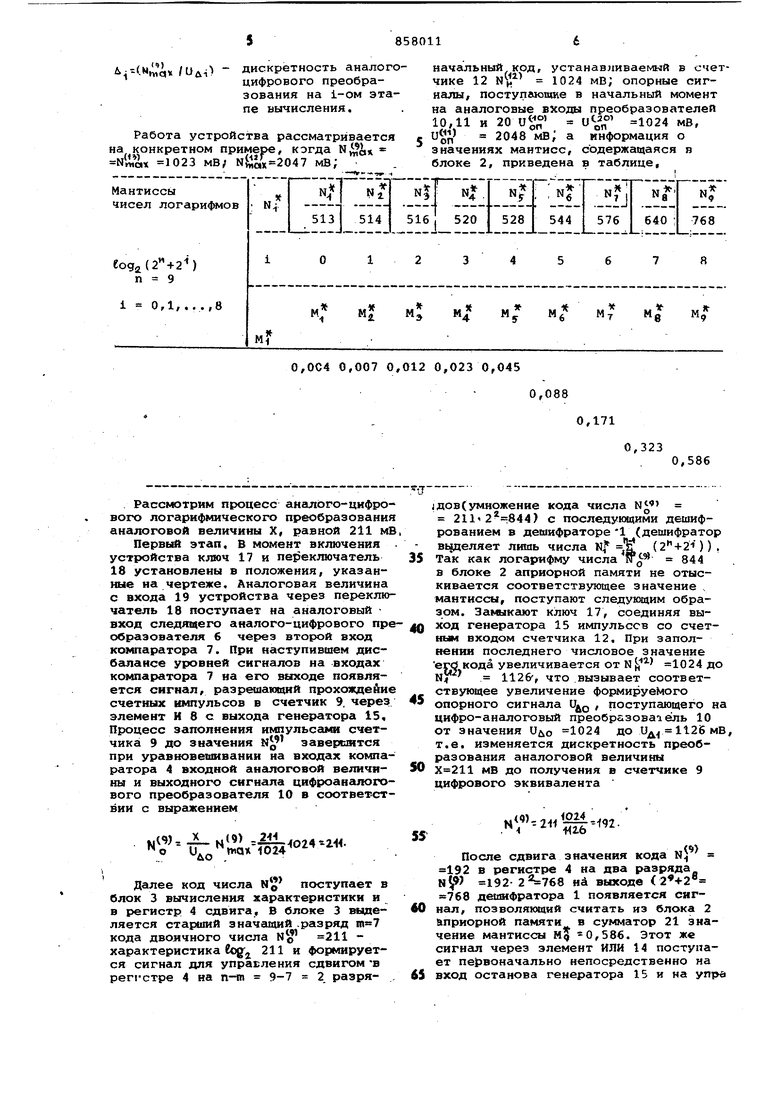

Работа устройства рассматривается на конкретном примере, когда N NU,2tx 1023 MB/ мВ; еод2(2 + 2) п 9 i 0,1,...,8 М М Mj

0,ОС4 0,007 0,012 0,023 0,045 Рассмотрим процесс аналого-цифрового логарифмического преобразования аналоговой величины X, равной 211 мВ Первый этап, В момент включения устройства ключ 17 и переключатель 18 установлены в положения, указанные на чертеже. Аналоговая величина с входа 19 устройства через переклю чатель 18 поступает на аналоговый вход следящего аналого-цифрового пре образователя в через второй вход компаратора 7. При наступившем дисбалансе уровней сигналов на входах компаратора 7 на его выходе появляется сигнал, разрешающий прохождение счетных импульсов в счетчик 9, через элемент Ибо выхода генератора 15, Процесс заполнения импульсами счетчика 9 до значения Ht завершится при уравновешивании на входах компаратора 4 входной аналоговой величины и выходного сигнала цифроаналогового преобразователя 10 в соответствии с вырг1жением .j(4), JL- .. о U. 1024 Далее код числа N поступает в блок 3 вычисления характеристики и в 1 егистр 4 сдвига, В блоке 3 выделяется старший значеиций .разряд т-7 211 кода двоичного числа Ng характеристика бод 211 и формируется сигнал для управления сдвигом в репстре 4 на n-m 9-7 2. разряначальный код, устанавливаемый в счечике 12 N)I 1024 мВ; опорные сигналы, поступающие в начальный момент

на аналоговые входы преобразователей |С1о иС201

10,11 и 20

„„ -1024 МВ, 2048 мВ; а информация о значениях мантисс, содержащаяся в блоке 2, приведена в таблице.

0,323

0,586 М М. М My Мд Мр дов(умножение кода числа N ) с последующими дешифрованием в дешифраторе1 (дешифратор выделяет лишь числа N ё ()), Так как логарифму числа Я 844 в блоке 2 априорной памяти не отыскивается соответствующее значение мантиссы, поступают следующим образом. Замыкают ключ 17, соединяя выход генератора 15 импульсов со счетным входом счетчика 12. При заполнении последнего числовое значение его кода увеличивается от 1024 до N 1126, что вызывает соответствующее увеличение формируемого опорного сигнала , поступающего на цифро-аналоговый преобразовачель 10 от значения 1024 до ид 1126мВ, т.е, изменяется дискретность преобразования аналоговой величины мВ до получения в счетчике 9 цифрового эквивалента .).,.. tOii- aj . -- игь После сдвига значения кода щ 192 в регистре 4 на два разряда 192 на выходе (2«+2 768 деимфратора 1 появляется сигнал, позволяющий считать из блока 2 Ё1приорной памяти в сумматор 21 значение мантиссы Н 0,586. Этот же сигнеш через элемент ИЛИ 14 поступает первоначально непосредственно на вход останова генератора 15 и на упра управляющие входы счетчика 9 и регис ра 13, в результате -lero генерирова ние импульсов с выхода генератора 15 приостанавливается, а уменьшенное в два раза значение кода М;,- f переписывается из счетчика 12 в счетчик 9 и в регистр 13, на выходе которого появляется сигнал S Далее, пройдя через элеьвент 16 задержки, сигнал поступает на вход запуска генератора 15, возобновив на его выходе генерирование импульса,и на установочный вход счетчика 12, восстановив на выходе преобразователя 11 начальное значение О4о 1024мВ. Заканчивается первкгй этап работы уст ройства, на котором определено перво приближенное значение цифрового эквивалента Логарифма аналоговой величины --eog-(l92. Ji|),m He,0g t126 -to§ i024 7, 536 .Для дальнейшего уточнения искомог результата необходимо вычислить мантиссу логарифма Cog 1126. Второй этап. Переключатель 18 пер1еводится в левое крайнее положение соединяя второй вход компаратора 7 с выходом преобразователя 20. На все дальнейших этапах работы перек яочатель 18 остается в левом крайнем положении, 17 замкнут. С началом второго этапа вновь происходит заполнение счетчика 12, HaosniiaH тем самым равновесие аналого-цифрового преобразователя б, для поддержания равновесия счетчик 9 по сигналу с компаратора 7 переводится в режим. вычитания. При уменьшении кода в 001-in ...,.., ..г., f /Л . .. счетчике 9 до значения Ы 544 на выходе дешифратора 1 появляется сиг нал, извещакщий о том, что в блоке априорной памяти хранится значение мантиссы ,088 логарифма Числа . Этот же сигнал через элемен ИДИ 14 приостанавливает генерирован импульсов генератором 15 и разрешае перезапись в счетчик 9 и регистр 13 с выхода счетчика 12 уменьшенное в два раза значение кода , опред ляемое из условия равновесия аналог цифрового преобразователя б, как Д9). uiSKKj 4l.. ЯЬгм2048--ЮМ 2О4в- 944 , Т.е. в счетчик 9 и в регистр 13 записываются новые значения кода, равные 530. Одновременно значение мантиссы М 0,088 считывается в сумматор 21 и суммируется с ранее полученн1лм значением{ Mj М9 +Мб 0,586+0,088 уточненный результат второго этапа. Через воемя, необходимое для считывания кода из счетчика 12 и уточнения результата в сумматоре 21, сигнал с выхода элемента 16 задержки вновь включает генератор 15 ИМПУЛЬСОВ и устанавливает в счетчике 12 начальное значение кода . Третий этап. Аналогично определяется мантисса логарифма числового эквивалента аналоговой величины utbix 530 мВ, преобразуемой в цифровой эквивалент до значения N а 528, логарифму которого в блоке 2 априорной памяти соответствует значение ма мантиссы Mff 0,045. Уточненный результат третьего- этапа М - + ,586+0,088+0,045 получен при показаниях счетчика 12 ..(12) 530-2048-1024 m 2048-523 . т.е. Объектом логарифмирования на четвертом этапе является значение . Логарифму этого значения без дополнительных преобразовательных операций в блоке 2 априорной памяти отыскивается значение мантиссы Mf 0,004. Окончательный результат вычисления заканчивается на четвертом этапе: Eoga. 211 7, 000+0,586+0,088+0, 045+ +0,,723.Таким образом, на каждом этапе процесс аналого-цифрового логарифмического преобразования аналогд ой величина с переменной автоматически перестраиваемой дискретностью преобразования при использовании определенного массива априорной памяти о значениях мантисс логарифмов цифровых эквивалентов преобразуемых аналоговых величин, подобен отысканию та-дкого сомножителя К| для логарифмируемого значения X, логарифму произведения которых в блоке априорной памяти отыскивается значение мантиссы м| , затем аналогично вычисляется логарифм сомножителя К и т.д. Рассмотренное устройство, по сравнению с известньм, позволяет повысить точность преобразования без существенных затрат, так как достижение одинаковой точности вычисления логарифмов в прототипе обеспечивается хранением в блоке 2 априорной памяти 2 значений мантисс и использованием дешифраторов 1 на 2 выходов, а в рассмотренном устройстве хранением в блоке 2 априорной памяти п значений мантисс Формула изобретения Логарифмирующее устройство, содержашее регистр памяти, основной счетчик, элемент ИЛИ , дешифратор, подключенный выходами к входам блока априорной памяти и блок вычисления характеристик, вход которого соедине с информационным входом регистра сдвига, а выход - с управляющим входом регистра сдвига и с первьвл входом регистра результата, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него дополнительно введены сумматор, генератор импульсо элемент задержки,ключ,переключатель, первый и второй цифроа налоговые преобр эаватели опорного сигнала и следящий аналого-цифровой преобразователь, вы полненный на компараторе, элементе И, счетчике и цифроаналоговом преобразователе, подключенном выходом к .первому входу компаратора, аналоговым входом - к выходу первого цифроаналогового преобразователя опорного сигнала, а цифровым входом - к информационному входу регистра сдвига и к выходу счётчика следящего аналого-цифрового преобразователя,кодовый установочный вход которого соединен с выходом основного счетчика, информационным входом регистра памяти и с цифровым входом первого цифроаналогового преобразователя опорно-го сигнала,вход управления установкой кода - с выходом элемента ИЛИ, вхоД9М остановки генератора импульсов, входом элемента задержки и с управлякяцим входом регистра памяти, а счетный вход - с выходом элемента И, подключенного первым входом к выхЬ.ду генератора импульсов и к входу ключа, а втооым входом - к выходу компаратора, соединенного вторым входом с выходом переключателя, первый вход KOTODoro подключен к входу устройства, а второй вход - к выходу второго цифроаналогового преобразователя опорного сигнала, соединенного цифровым входом с выходом регистра памяти, причем входы элемента ИЛИ подключены к выходам дешифратора, соединенного цифровым входом с выходом регистра сдвига, выход блока априорной памяти подключен через сумматор к ВТОРОМУ входу регистра рез.ультата, а выход элемента задержки соединен с входом запуска генератора импульсов и с установочным входом основного счетчика, счетный вход КОТОРОГО подключен к выходу ключа, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР I 623210, кл. G 06 Г, 7/24, 1977. 2f Авторское свидетельство СССР 603996, кл. G 06 F 15/20, 1975. 3. Авторское свидетельство СССР 615486, кл. G 06 F 15/20, 1977 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-11-26—Подача