(54) МАЖОРИТАРНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное устройство | 1980 |

|

SU898633A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для исправления ошибокВ КОРРЕКТиРующиХ КОдАХ | 1979 |

|

SU796848A1 |

| Устройство встроенного саморемонта памяти с резервными элементами | 2017 |

|

RU2667786C1 |

| Оперативное запоминающее устройство с исправлением ошибок | 1988 |

|

SU1674269A1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Устройство для исправления ошибок в блоках памяти | 1981 |

|

SU1070605A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1984 |

|

SU1246380A1 |

I

Изобретение относится к вычислительной технике и может быть использовано для создания высоконадежных устройств с мажоритарным резервированием.

Известно устройство для исправления одиночных ошибок, которое содержит S-входовой элемент ИЛИ, п двухвходовых элементов ИЛИ, п двухвходовых элементов И и nS-входовых элементов И, причем выход каждого двухвходового элемента И соединен с одним соответствующим входом двухвходового элемента ИЛИ, другой вход которого соединен с выходом соответствующего S-входового элемента И, а выходы двухвходовых элементов ИЛИ являются выходами устройства tl 1.

Недостатком этого устройства является невозможность его применения для исправления трех ошибок.

Наиболее близким по технической сущности к изобретению является

мажоритарное устройство, содержащее. 35 элементов 4 И, выходы которых соединены со входами элемента 35 ИЛИ, входы - с семью входами устройства , а выход элемента ИЛИ является выходом устройства 2.

Недостатком таких мажоритарных устройств для исправлениятрех ошибок является большое оборудование при организации S независимых вы10ходов защищаемого устройства, что Лриводит к его удорожанию и понижает надежность его работы.

Цель изобретения - упрощение и повышение надежности устройства,в

15 частности при организации S независимых выходов устройства с исправлением трех ошибок.

Поставленная цель достигается тем, что мажоритарное устройство,

20 содержащее элементы И и ИЛИ, содержит три входных группы из пяти элементов 2 ИЛИ, выходы четвертого и пятого из которых соединены с

39

входами элемента 2 И, и одну группу из шести элементов 2 ИЛИ, выходы первого и второго из которых соединены с входами первого элемента 2 И выходы пятого и шестого - с входами второго элемента 2 И и по числу выходов устройства выходные группы из четырех элементов 4 И, выходы которых в каждой выходной группе соединены через элемент k ИЛИ с соответствующим выходом устройства, а входы - с выходами соответствующей входной группы, входы элементов 2 ИЛ входных групп соединены с соответствующими парами из семи входов устройства.

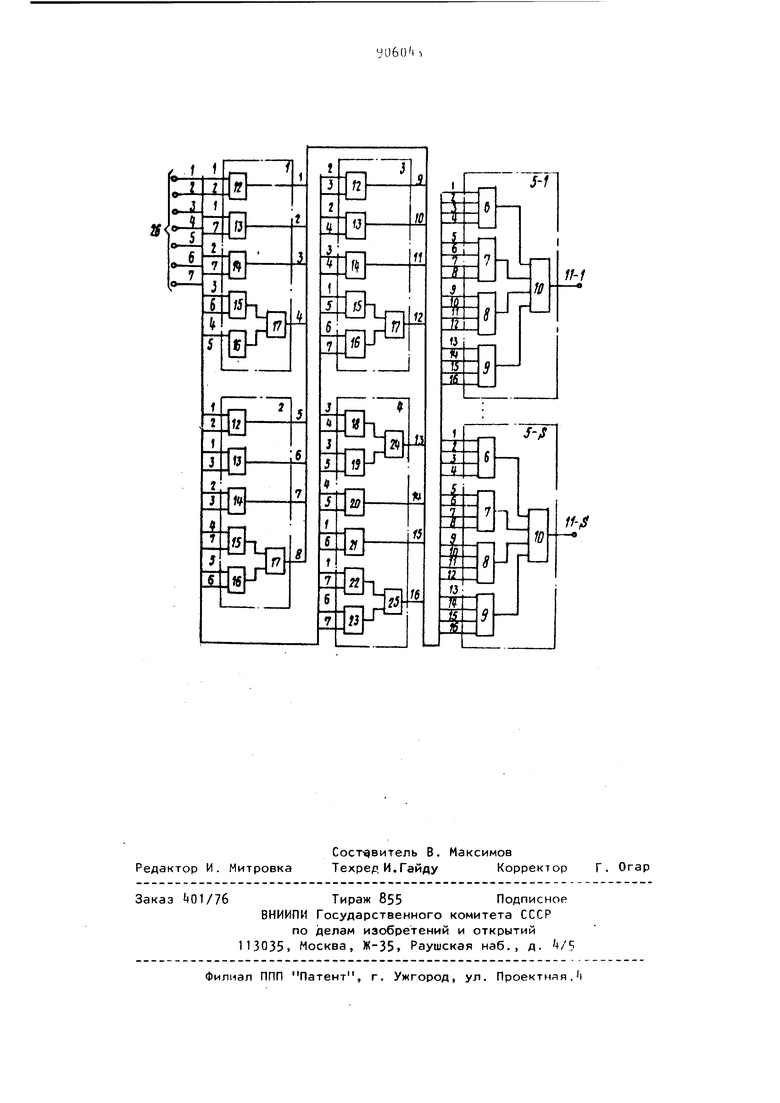

На чертеже представлена функциональная блок-схема мажоритарного устройства для исправления трех ошибок .

Мажоритарное устройство содержит входные группы 1- элементов и S выходные группы каждая из которых состоит из элементов k И 6-9, элемента ИЛИ 10, выходы 11 - 1,...,11-S которых являются выходами устройства, входные группы 1-3 состоят из элементов 2 ИЛИ 12-16 и элемента 2 И 17, а группа - из элем-ентов 2 ИЛИ 18-23 и элементов 2 И и 25, определенным образом соединенных с элементами ИЛИ, которые соединены со входами 2б устройства.

Устройство работает следующим образом.

На входах устройства имеются три ошибки типа , исправное значение входов и выходов групп . Тогда в соответствии с принципом построения устройства среди входных групп 1- находится хотя бы одна, все выходы которой равны 1 и следовательно мажоритарная функция устройства равна 1 на всех S выходах 11-1 - 11-S. Аналогично ,если за исправное значение выходов групп l-t принимают О, то при любых трех ошибках на входах устройства по крайней мере один выход в каждой группе равен О и на всех S выходах устройства 11-1 - 11-S исправные значения (О). Если оказываются неисправными любые три и менее элементов в трех и менее входных группах I-,

34

то выходы устройства остаются исправными. Если же в трех и менее элементах выходных групп происходят ошибки, то они исправлены посл дующими мажоритарными устройствами .

Таким образом, построение мажоритарного устройства для исправления трех ошибок в виде двух ярусов: .один - входные группье элементов и другой - S выходных групп, позволяет существенно сократить оборудование и повысить надежность работы устройства при организации S независимых исправных выходов защищаемого устройства. При этом, чем выше S, тем существеннее выигрыш.

Формула изобретения

Мажоритарное устройство, содержащее элементы И и ИЛИ, отличающееся тем, что, с целью упрощния и расширения функциональных возможностей устройства, оно содержит три входных группы из пяти элементов 2 ИЛИ, выходы четвертого и пятого из которых соединены с входами элемента 2 И, и одну группу из шести элементов 2 ИЛИ, выходы первого и второго из которых соединены с входами первого элемента 2 И, выходы пятого и шестого - со входами второго элемента 2 И и по числу выходов устройства выходные группы из четырех элементов 4 И, выходы которых в каждой выходной группе соединены через элемент ; ИЛИ с соответствующим выходом устройства, а входы - с выходами соответствующей входной группы, входы элементов 2 ИЛИ входных групп соединены с соответствующими парами из семи входов устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-02-15—Публикация

1980-05-14—Подача