Область техники

Настоящее изобретение в целом относится к области вычислительной техники, а именно к системам на кристалле, содержащим внутреннюю память с резервными элементами и встроенные блоки самотестирования.

Уровень техники

Известно устройство встроенного саморемонта, содержащее генераторы конфигурации резервных элементов, регистры хранения адресов поврежденных элементов и регистры хранения конфигурации резервных элементов (Патент на изобретение US 5577050 А, кл. G01R 31/28, опубл. 19.11.1996 г.).

Недостатком описанного устройства является наличие персонального генератора конфигурации резервных элементов для каждого ремонтируемого блока памяти. Это приводит к увеличению занимаемой устройством площади кристалла. Также к недостаткам устройства можно отнести проведение последовательного тестирования каждого восстанавливаемого массива памяти, что выражается в росте времени выполнения операции саморемонта. Отсутствует проверка наличия ошибок в резервных элементах, что снижает надежность проведенного ремонта и оставляет возможность отремонтированной памяти быть неисправной. Отсутствуют флаги и выходные сигналы исправности резервных элементов, что затрудняет последующие операции саморемонта.

Также известно устройство встроенного саморемонта памяти, содержащее блок управляющей логики, счетчики поврежденных элементов, регистры хранения адресов поврежденных элементов и регистры хранения конфигурации резервных элементов (Заявка на изобретение US 20090319839 А1, кл. G11C 29/04, G06F 11/07 опубл. 24.12.2009 г.).

Недостатком этого устройства является отсутствие функции проверки резервных элементов для блоков памяти с исправными основными элементами, что не предоставляет информации пользователю о возможности использования резервных элементов в будущем. Флаг неисправности резервного элемента выставляется только при ошибке самотестирования после операции ремонта.

Наиболее близким по технической сути и достигаемому результату является устройство встроенного саморемонта памяти с резервными элементами, содержащее блок управляющей логики, автомат состояний, генератор конфигурации резервных элементов, счетчик поврежденных элементов, регистры флагов исправности резервных элементов, регистры хранения адресов поврежденных элементов, регистр для хранения конфигурации резервных элементов (Патент на изобретение US 6691264 В2, кл. G11C 29/00, опубл. 10.02.2004 г.).

Недостатком этого устройства является проведение операции самотестирования не только для основных элементов, но и для резервных, что увеличивает время проведения операции и занимаемую устройством площадь на кристалле. Расширенная матрица памяти тестируется как при первой операции самотестирования, так и при второй. Это приводит как к увеличению времени самотестирования, так и к увеличению места, занимаемого устройством встроенного самотестирования на кристалле.

Данное устройство не обладает набором счетчиков, необходимых для работы с несколькими блоками памяти, что приводит к необходимости вводить персональное устройство для ремонта каждого блока и к увеличению занимаемой устройством площади кристалла. Также отсутствует интерфейс управления для доступа внешнего управляющего устройства к регистрам конфигурации резервных элементов, регистрам диагностики и регистрам, хранящим флаги исправности резервных элементов. Это приводит к невозможности работы в программном режиме, т.е. произвести замену поврежденных основных элементов резервными в ручном режиме.

Сущность изобретения

Устройство встроенного саморемонта памяти с резервными элементами, содержащее блок управляющей логики (БУЛ), генератор конфигурации резервных элементов (ГКРЭ), автомат состояний (АС), выходной сигнал статуса операции саморемонта (CP) БУЛ поступает на выход статуса операции CP устройства, выходной сигнал разрешения записи в регистры диагностики (РД) АС поступает на вход разрешения записи в РД ГКРЭ, выходной сигнал разрешения записи в регистры конфигурации резервных элементов (РКРЭ) АС поступает на вход разрешения записи в РКРЭ ГКРЭ, отличается наличием входного сигнала старта операции CP в аппаратном режиме, поступающего на вход старта операции CP в аппаратном режиме АС, входного сигнала старта операции CP в программном режиме, поступающего на вход старта операции CP в программном режиме АС, входного сигнала окончания операции СТ, поступающего на вход окончания операции СТ AC, k входных шин диагностики (ШД), соединенных с соответствующими входами ШД ГКРЭ, k выходных шин конфигурации резервных элементов (ШКРЭ) ГКРЭ, выходного сигнала исправности резервных элементов (ИРЭ) ГКРЭ, поступающего на вход ИРЭ БУЛ, выходного сигнала окончания операции CP АС, входной шины записи данных интерфейса управления (ИУ), соединенной с входной шиной записи данных ИУ ГКРЭ, входной шиной адреса ИУ, соединенной с входной шиной адреса ИУ ГКРЭ и входной шиной адреса ИУ БУЛ, входного сигнала разрешения записи ИУ, поступающего на вход разрешения записи ИУ ГКРЭ и вход разрешения записи ИУ БУЛ, выходной шиной чтения данных ИУ, соединенной с выходной шиной чтения данных ИУ ГКРЭ, выходного сигнала счетчика операций СТ АС, поступающего на вход счетчика операций СТ ГКРЭ, выходного сигнала разрешения записи в РКРЭ АС, поступающего на вход разрешения записи в РКРЭ БУЛ, выходного сигнала статуса операции СТ ГКРЭ, поступающего на вход статуса операции СТ БУЛ, выходного сигнала флага проверки резервных элементов (ФПРЭ) ГКРЭ, поступающего на вход ФПРЭ БУЛ, выходного из сигнала флага исправности резервных элементов (ФИРЭ) ГКРЭ, поступающего на вход ФИРЭ БУЛ, выходного сигнала счетчика обработанных блоков (СОБ) БУЛ, поступающего на вход СОБ АС и вход СОБ ГКРЭ.

За счет использования такой конструкции устройства саморемонта инициируется параллельное тестирование блоков памяти, что позволяет уменьшить занимаемую устройством площадь кристалла и время, затрачиваемое на проведение операции саморемонта.

Анализ всех ошибок происходит после завершения первого тестирования единственным генератором конфигурации резервных элементов, использующимся последовательно для принятия решения о конфигурации резервных элементов каждого блока памяти. Устройство инициирует второе тестирование после предложенной конфигурации резервных элементов для исключения ситуации наличия ошибок в резервных элементах и повторное тестирование для блоков с исправными основными элементами для проверки корректной работы резервных элементов ввиду возможности их дальнейшего использования, что позволяет повысить надежность проводимой операции саморемонта.

Устройство имеет счетчики, позволяющие ему работать с любым количеством блоков памяти.

За счет предоставления информации об исправности резервных элементов для возможного ремонта в процессе эксплуатации обеспечивается возможность использования резервных элементов памяти в процессе работы микросхемы.

Технический результат от использования данного изобретения состоит в уменьшении занимаемой устройством площади кристалла, уменьшении времени, затрачиваемого на проведение операции саморемонта, повышении надежности проводимой операции саморемонта и обеспечении возможности использования резервных элементов памяти в процессе работы микросхемы.

В частном варианте выполнения устройства ГКРЭ содержит k блоков по n двухвходовых элементов ИЛИ, где k - количество блоков памяти, с которыми работает устройство, a n - разрядность информационного слова, хранящееся в каждом блоке памяти, k РД уменьшенной разрядности, первого мультиплексора, шифратора КРЭ, второго мультиплексора, первого двухвходового элемента ИЛИ, первого и второго демультиплексоров, k регистров для хранения конфигурации резервных элементов (РКРЭ), третьего мультиплексора, n-входового элемента И, первого инвертора, четвертого мультиплексора, второго двухвходового элемента ИЛИ, первого двухвходового элемента И, третьего и четвертого демультиплексоров, k регистров флагов проверки резервных элементов (РФПРЭ), пятого мультиплексора, второго двухвходового элемента И, шестого мультиплексора, третьего двухвходового элемента ИЛИ, третьего двухвходового элемента И, пятого и шестого демультиплексоров, k регистров флагов исправности резервных элементов (РФИРЭ) уменьшенной разрядности, седьмого мультиплексора, причем каждый из k блоков по n двухвходовых элементов ИЛИ соединен с соответствующей входной ШД и выходом соответствующей ячейки РД; на каждый из k РД поступают сигналы с соответствующих выходов блоков по n двухвходовых элементов ИЛИ и сигнал разрешения записи в РД; вход первого мультиплексора соединен с k выходами из k РД, на управляющий вход первого мультиплексора поступает сигнал СОБ, а его выходы соединены с выходной шиной чтения данных ИУ; вход шифратора КРЭ соединен с выходом первого мультиплексора, выходом счетчика операций СТ, выходом пятого мультиплексора; вход второго мультиплексора соединен с выходом шифратора КРЭ, шиной записи данных ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ; вход первого демультиплексора соединен с выходом второго мультиплексора, а на управляющий вход поступает сигнал СОБ; на вход первого двухвходового элемента ИЛИ поступает сигнал разрешения записи в РКРЭ и сигнал разрешения записи по ИУ; вход второго демультиплексора соединен с выходом первого двухвходового элемента ИЛИ, а на управляющий вход поступает сигнал СОБ; входы каждого из k РКРЭ соединены с соответствующими выходами первого и второго демультиплексоров, а их выходы соединены с k выходными ШКРЭ; входы третьего мультиплексора соединены с k выходами из РКРЭ, а на управляющий вход поступает сигнал СОБ; входы первого n-входового элемента И соединены с выходами первого мультиплексора, а его выход является выходом статуса операции СТ ГКРЭ; вход четвертого мультиплексора соединен с выходом первого n-входового элемента И, шиной записи данных ИУ, а на управляющих вход поступает сигнал разрешения записи ИУ; вход третьего демультиплексора соединен с выходом четвертого мультиплексора, а на управляющий вход поступает сигнал СОБ; второй двухвходовый элемент ИЛИ принимает на вход входной сигнал разрешения записи в РКРЭ и сигнал разрешения записи ИУ; первый инвертор принимает на вход входной сигнал счетчика операций СТ; вход первого двухвходового элемента И соединен с выходом второго двухвходового элемента ИЛИ и выходом первого инвертора; вход четвертого демультиплексора соединен с выходом первого двухвходового элемента ИЛИ, а на управляющий вход поступает сигнал СОБ; входы каждого из k РФПРЭ соединены с соответствующими выходами третьего и четвертого демультиплексоров; вход пятого мультиплексора соединен с k выходами РФПРЭ, на управляющий вход поступает сигнал СОБ, а его выход соединен с выходной шиной чтения данных ИУ; вход второго двухвходового элемента И соединен с выходом первого n-входового элемента И и выходом пятого мультиплексора; вход шестого мультиплексора соединен с выходом второго двухвходового элемента И, со входной шиной записи данных ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ; вход пятого демультиплексора соединен с выходом шестого мультиплексора, а на управляющий вход поступает сигнал СОБ; третий двухвходовый элемент ИЛИ принимает на вход входной сигнал разрешения записи в РКРЭ и сигнал разрешения записи ИУ; на входы третьего двухвходового элемента И поступает сигнал с выхода третьего двухвходового элемента ИЛИ и сигнал счетчика операций СТ; вход шестого демультиплексора соединен с выходом третьего двухвходового элемента И, а на управляющий вход поступает сигнал разрешения записи ИУ; вход каждого из k РФИРЭ соединен с соответствующими выходами пятого и шестого демультиплексоров; вход седьмого мультиплексора соединен с k выходами РФИРЭ, на управляющий вход поступает сигнал СОБ, а выход соединен с шиной чтения данных ИУ.

В еще одном частном варианте изобретения БУЛ содержит первый двухвходовый элемент ИЛИ, счетчик исправных блоков, первый компаратор, счетчик блоков с исправными резервными элементами, второй компаратор, СОБ, первый мультиплексор, причем первый двухвходовый элемент ИЛИ принимает на вход входной сигнал ФПРЭ и входной сигнал разрешения записи в РКРЭ; вход счетчика исправных блоков соединен с выходом первого двухвходового элемента ИЛИ; вход первого компаратора соединен с выходом счетчика исправных блоков, выходным сигналом первого компаратора является сигнал статуса операции CP; счетчик исправных резервных элементов принимает на вход входной сигнал ФИРЭ; вход второго компаратора соединен с выходом счетчика исправных резервных элементов, выходным сигналом второго компаратора является сигнал ИРЭ; СОБ принимает на вход входной сигнал разрешения записи в РКРЭ; вход первого мультиплексора соединен с выходом СОБ, с входной шиной адреса ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ.

Краткое описание чертежей

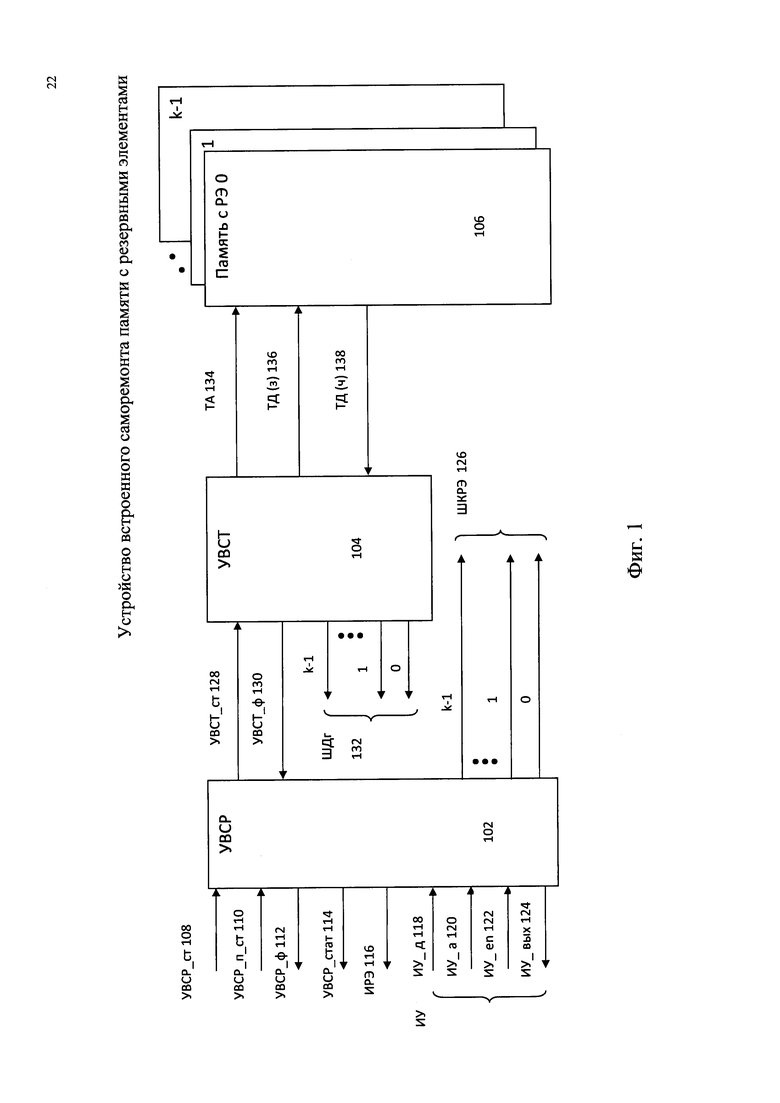

Фиг. 1 показывает схему, в которой может использоваться предлагаемое устройство. 102 - устройство встроенного саморемонта памяти с резервными элементами, 104 - устройство встроенного самотестирования, 106 - k блоков памяти с резервными элементами, 108 - сигнал старта операции саморемонта в аппаратном режиме, 110 - сигнал старта операции саморемонта в программном режиме, 112 - сигнал окончания операции саморемонта, 114 - сигнал статуса операции саморемонта, 116 - сигнал исправности резервных элементов, 118 - шина записи данных интерфейса управления, 120 - шина адреса интерфейса управления, 122 - сигнал разрешения записи интерфейсу управления, 124 - шина чтения данных интерфейса управления, 126 шины конфигурации резервных элементов, 128 - сигнал старта операции самотестирования, 130 сигнал окончания операции самотестирования, 132 - шины диагностики, 134 - шина тестового адреса, 136 - шина записи тестовых данных, 138 - шина чтения тестовых данных.

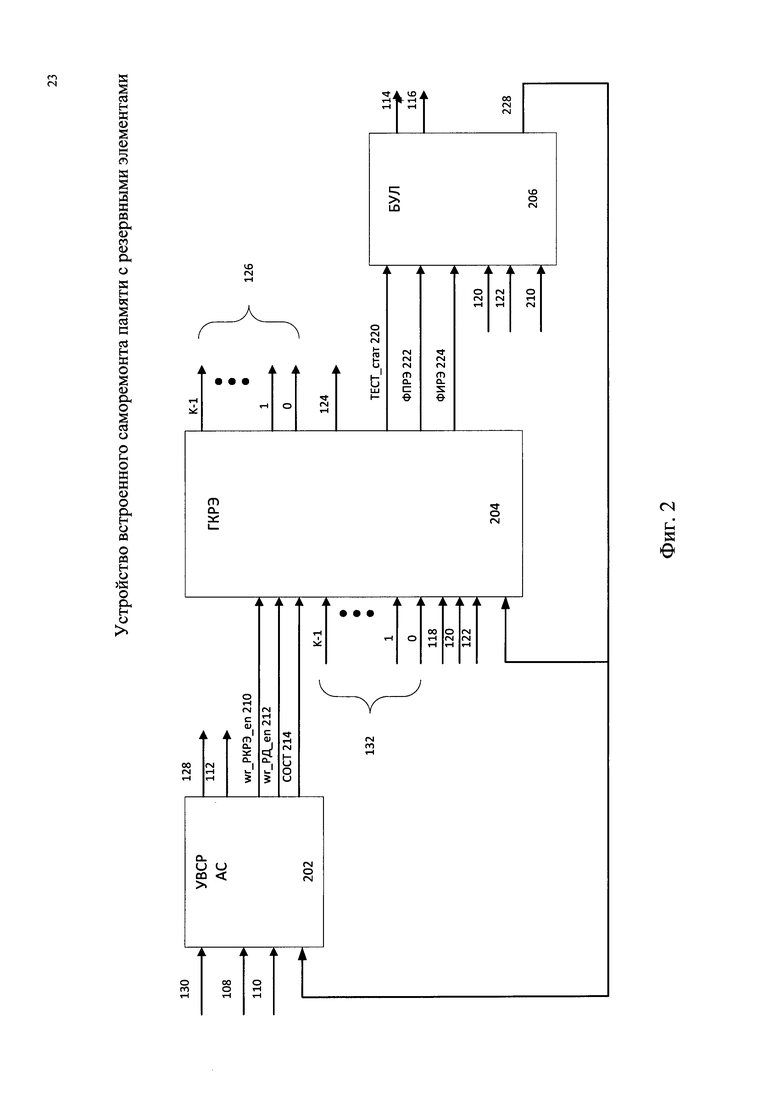

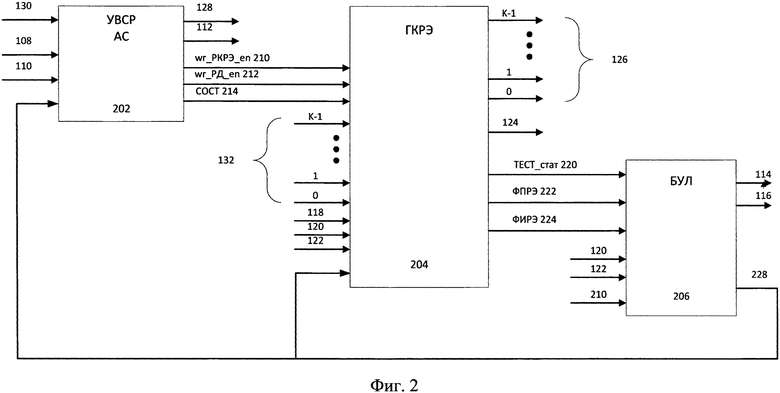

Фиг. 2 показывает структуру предлагаемого устройства, на которой 202 - автомат состояний, 204 - генератор конфигурации резервных элементов, 206 - блок управляющей логики, 210 - сигнал разрешения записи в регистры конфигурации резервных элементов, 212 - сигнал разрешения записи в регистры диагностики, 214 - сигнал счетчика операций самотестирования, 220 - статус операции самотестирования, 222 - сигнал флага проверки резервных элементов, 224 - сигнал флага исправности резервных элементов, 228 - сигнал счетчика обработанных блоков.

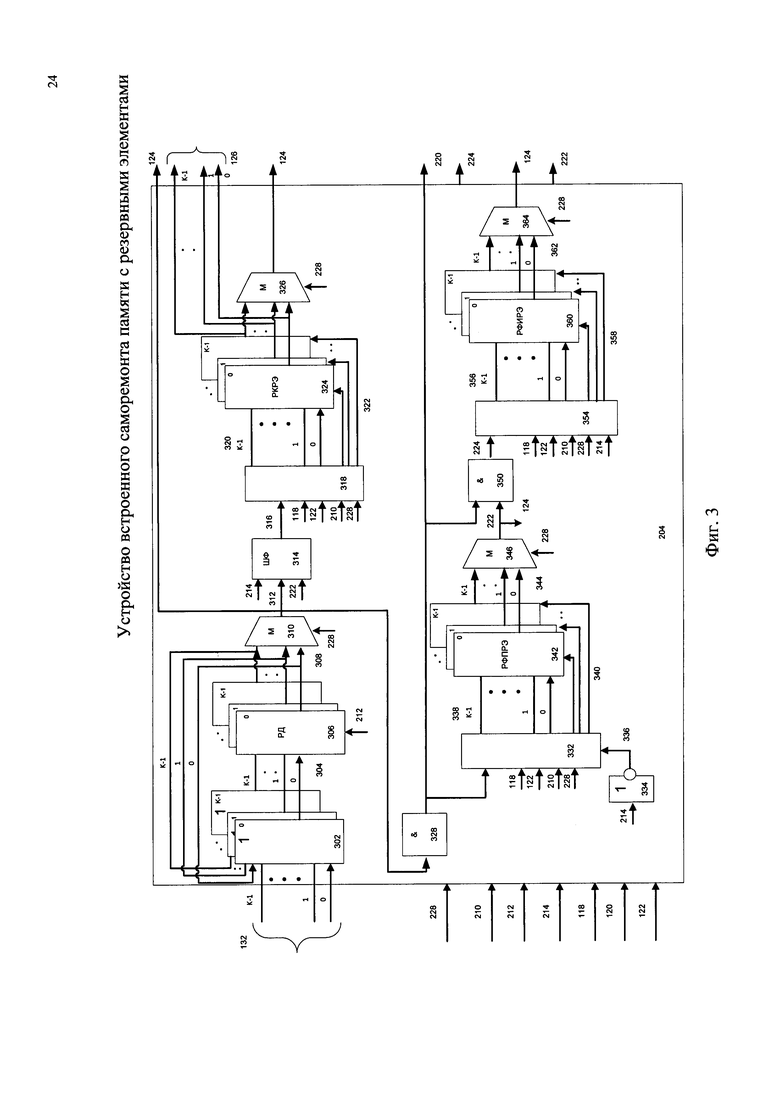

Фиг. 3 показывает схему генератора конфигурации резервных элементов, на которой 302 - k блоков по n двухвходовых элементов ИЛИ, 304 - k выходных шин из блоков по n двухвходовых элементов ИЛИ, 306 - k регистров диагностики, 308 - k выходных шин регистров диагностики, 310 - первый мультиплексор, 312 - выходная шина диагностики, 314 - шифратор конфигурации резервных элементов, 316 - выходная шина шифратора резервных элементов, 318 - схема мультиплексирования шин записи в регистры конфигурации резервных элементов, 320 - k выходных шин из первого демультиплексора, 322 - k выходных шин из второго демультиплексора, 324 - k регистров конфигурации резервных элементов, 326 - третий мультиплексор, 328 - первый n-входовый элемент И, 332 - схема мультиплексирования сигналов записи в регистры флагов проверки резервных элементов, 334 - первый инвертор, 336 - выход первого инвертора, 338 - k выходных сигналов из третьего демультиплексора, 340 - k выходных сигналов из четвертого демультиплексора, 342 - k регистров флагов проверки резервных элементов, 344 - k выходов из регистров флагов проверки резервных элементов, 346 - пятый мультиплексор, 350 - второй двухвходовый элемент И, 354 (аналогично 332) - схема мультиплексирования сигналов записи в регистры флагов исправности резервных элементов, 356 - k выходных сигналов из пятого демультиплексора, 358 - k выходных сигналов из шестого демультиплексора, 360 - k регистров флагов исправности резервных элементов, 362 - k выходных сигналов из регистров флагов исправности резервных элементов, 364 - седьмой мультиплексор.

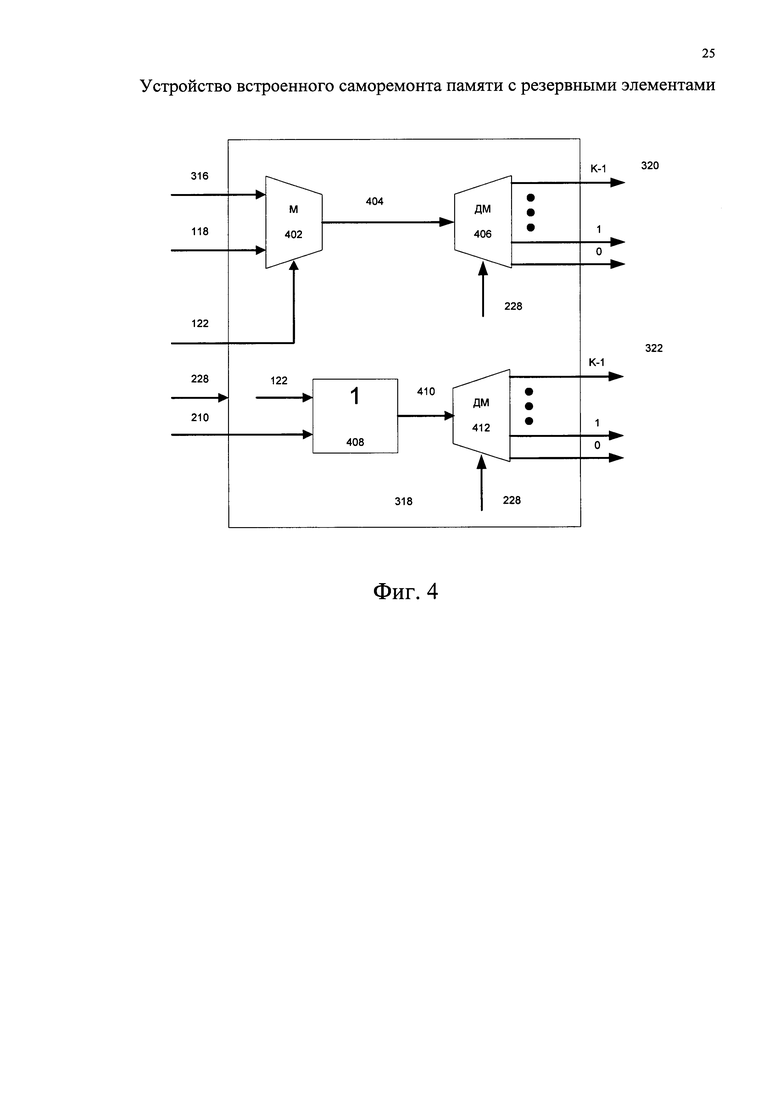

Фиг. 4 показывает схему мультиплексирования шин записи в регистры конфигурации резервных элементов, на которой 402 - второй мультиплексор, 404 - выходная шина второго мультиплексора, 406 - первый демультиплексор, 408 - первый двухвходовый элемент ИЛИ, 410 - выходной сигнал из первого двухвходового элемента ИЛИ, 412 - второй демультиплексор.

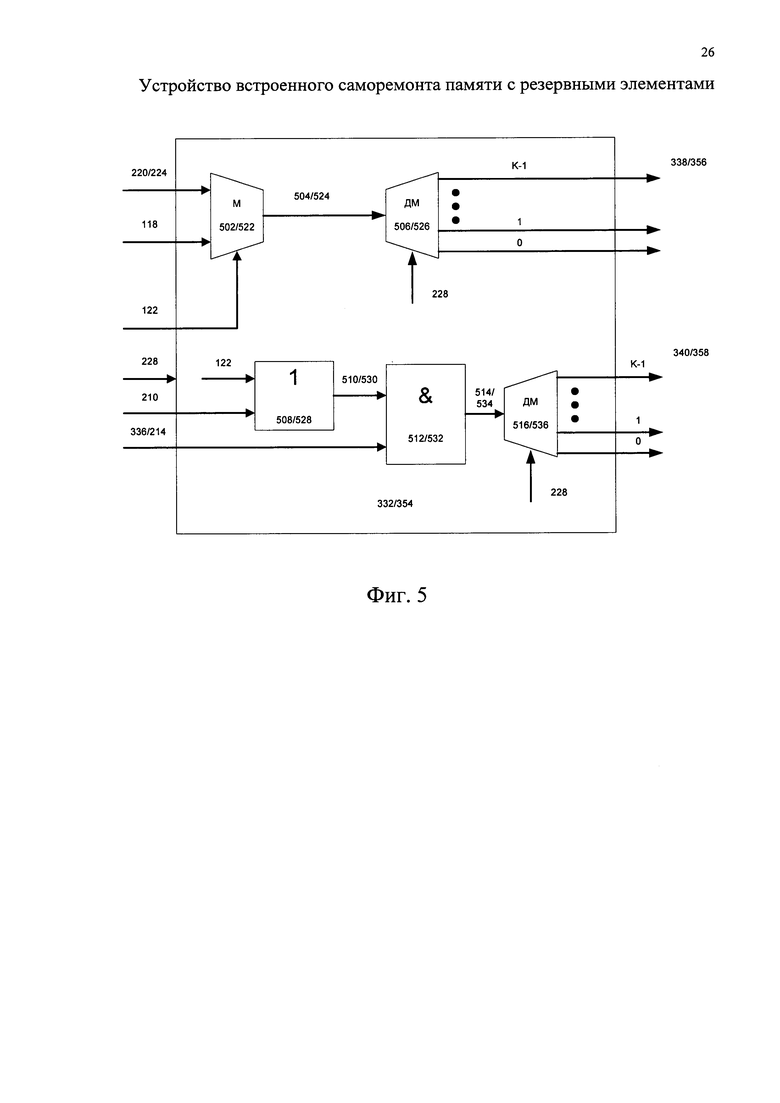

Фиг. 5 показывает схему мультиплексирования сигналов записи в регистры флагов проверки резервных элементов/регистры флагов исправности резервных элементов, на которой 502/522 - четвертый/шестой мультиплексор, 504/524 - выход четвертого/шестого мультиплексора, 506/526 - третий/пятый демультиплексор, 508/528 - второй/третий двухвходовый элемент ИЛИ, 510/530 - выход второго/третьего двухвходового элемента ИЛИ, 512/532 - первый/третий двухвходовый элемент И, 514/534 - выход первого/третьего двухвходового элемента И, 516/536 - четвертый/шестой демультиплексор.

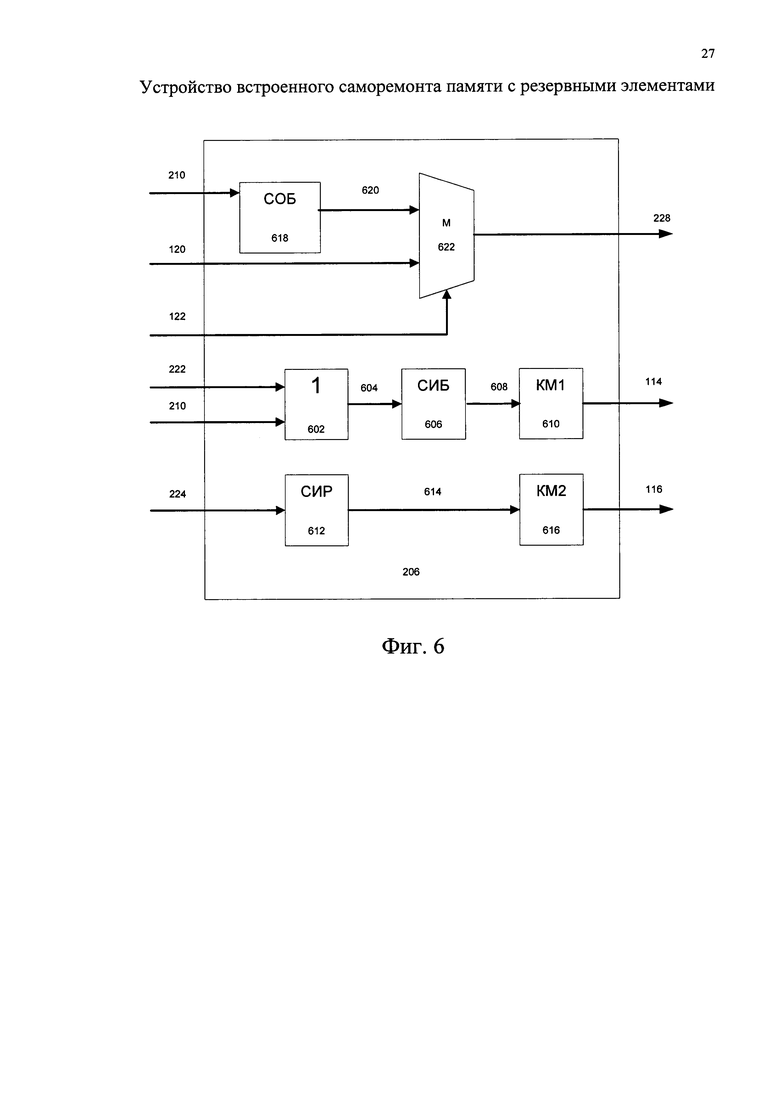

Фиг. 6 показывает схему блока управляющей логики, на которой 602 - первый двухвходовый элемент ИЛИ, 604 выход первого двухвходового элемента ИЛИ, 606 - счетчик исправных блоков, 608 - выход счетчика исправных блоков, 610 - первый компаратор, 612 - счетчик исправных резервных элементов, 614 - выход счетчика исправных резервных элементов, 616 - второй компаратор, 618 - счетчик обработанных блоков, 620 - выход счетчика обработанных блоков, 622 - первый мультиплексор.

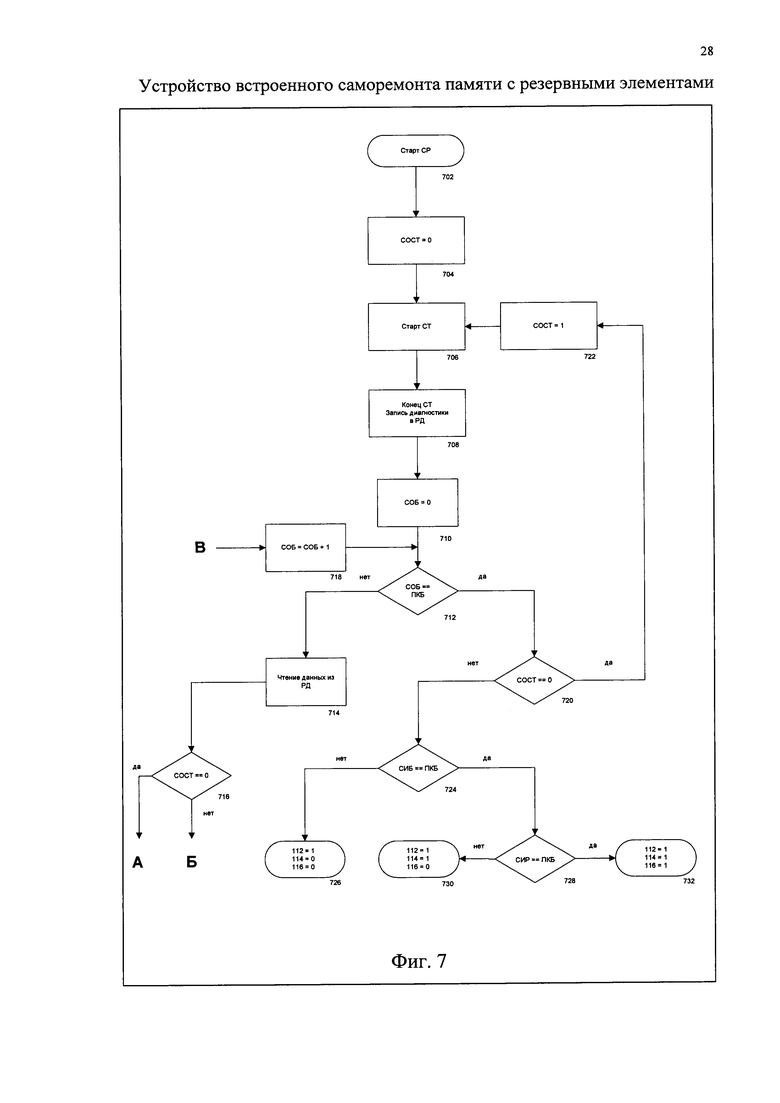

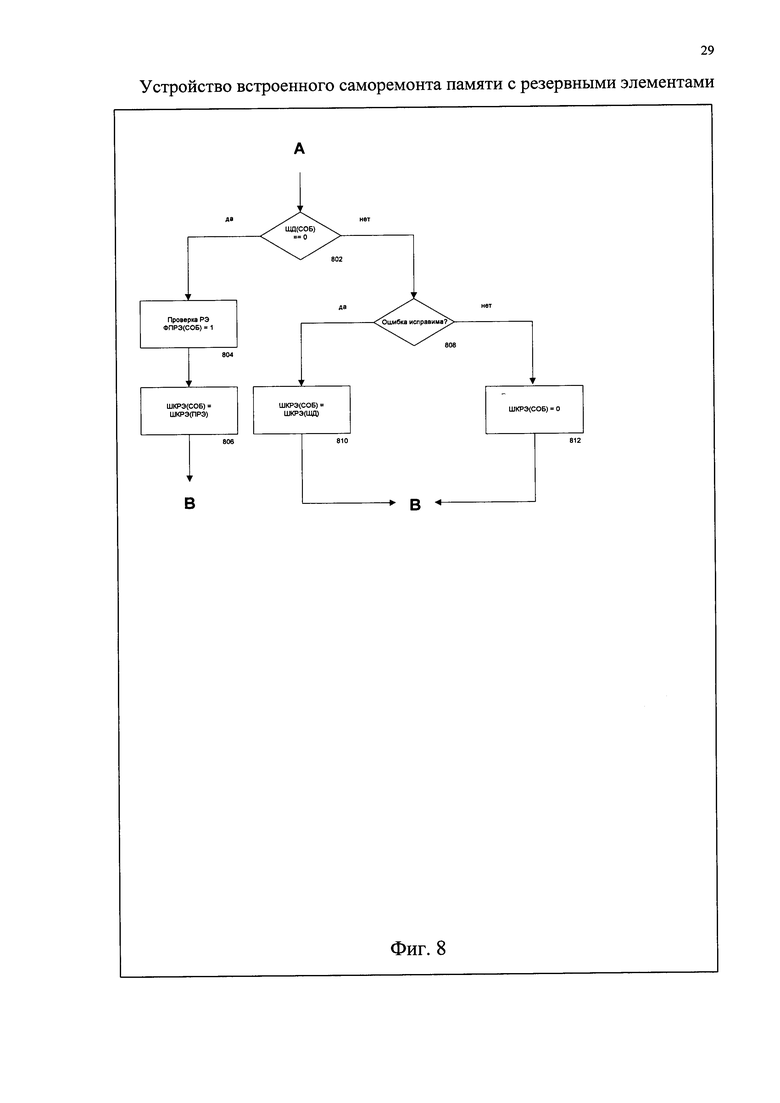

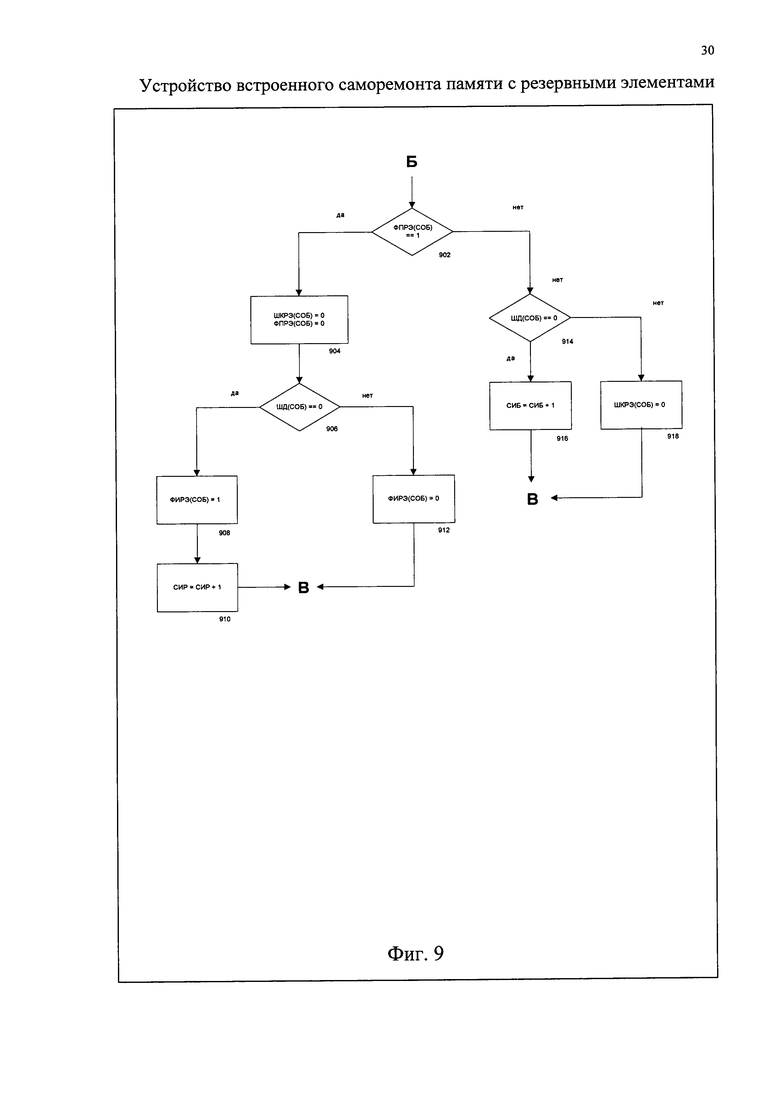

Фиг. 7-9 - показывают алгоритм работы УВСР.

Подробное описание изобретения

Схема, в составе которой может быть использовано данное устройство, изображена на фиг. 1. Она содержит устройство встроенного саморемонта памяти с резервными элементами 102, устройство встроенного самотестирования памяти 104 и блок памяти с резервными элементами 106.

Описываемое устройство встроенного саморемонта памяти способно работать в двух режимах: в программном или аппаратном. Первый режим работы, аппаратный, будет инициироваться с помощью входного сигнала старта операции саморемонта 108. В этом случае ремонт будет проведен аппаратно. Второй режим работы - программный - инициируется входным сигналом 110. Будет проведена одна операция самотестирования, после который будет выставлен выходной сигнал окончания операции саморемонта 112, он же будет активирован и в случае завершения работы в аппаратном режиме. По результату операции саморемонта в аппаратном режиме будут выставлены в логическую единицу сигналы статуса операции саморемонта 114, в случае, если для каждого блока памяти удалось найти корректную конфигурацию резервных элементов, и исправности резервных элементов тестируемых блоков 116, в случае, если все резервные элементы блоков свободны и исправны. Также устройство саморемонта содержит интерфейс управления для программного доступа к внутренним регистрам устройства саморемонта памяти при работе в программном режиме. В состав интерфейса управления входят: 118 - шина записи данных интерфейса управления, 120 - шина адреса интерфейса управления, 122 - вход разрешения записи по интерфейсу управления, 124 - шина чтения данных интерфейса управления.

При работе в программном режиме с его помощью можно считать информацию диагностики операции самотестирования, а затем записать новую конфигурацию резервных элементов и опционально флаги исправности резервных элементов. Устройство соединено k шинами конфигурации резервных элементов 126 с k блоками памяти с резервными элементами. Выход устройства старта операции самотестирования соединен с входом устройства встроенного самотестирования 104 старта операции самотестирования 128, входом завершения операции самотестирования 130, а также k шинами диагностики 132. Устройство встроенного самотестирования 104 соединено с блоками памяти 106 шиной тестового адреса 134, шиной записи тестовых данных 136 и шиной чтения тестовых данных 138.

Описание состава устройства изображено на фиг. 2-6. На фиг. 2 показаны составные части устройства. Оно состоит из автомата состояний 202, генератора конфигурации резервных элементов 204, блока управляющей логики 206. Входными для автомата состояний являются сигналы 108 и 110, выходным является сигнал 130. Выходными для автомата состояния и входными для генератора конфигурации резервных элементов являются сигналы разрешения записи в регистры конфигурации резервных элементов 210, разрешения записи в регистры диагностики 212, счетчика операций самотестирования. Входными для генератора конфигурации резервных элементов являются также k шин диагностики 132 и интерфейс управления: 118, 120, 122. Выходными из генератора конфигурации резервных элементов являются k шин конфигурации резервных элементов 126, шина чтения данных интерфейса управления 124. Выходными для генератора конфигурации резервных элементов являются и входными для блока управляющей логики являются сигнал статуса операции самотестирования 220, флаг проверки резервных элементов 222, флаг исправности резервных элементов 224. Входными для блока управляющей логики также являются сигналы 120 и 122 интерфейса управления и сигнал 210. Выходными для блока управляющей логики являются сигналы 114 и 116, а также счетчик обработанных блоков 228.

На фиг. 3-5 описан состав генератора конфигурации резервных элементов. K блоков по n двухвходовых элементов ИЛИ 302 имеют соответствующие k выходов 304 и соединены с соответствующими k регистрами диагностики 306. В k блоков по n двухвходовых элементов ИЛИ 302 входят соответственно шины 132 и выходы регистров диагностики 308. Мультиплексор 310 принимает на вход k шин 308 и 228 в качестве управляющего сигнала. Первый мультиплексор 310 имеет k входов и выходов, являющихся n-разрядными шинами. Выходы мультиплексора 312 соединены с выходной шиной чтения интерфейса управления и шифратором 314. Также на шифратор поступают сигналы 214 и 222. Выход шифратора 316 соединен с мультиплексором 402, на который также приходит сигнал 118. Выход мультиплексора 404 соединен с демультиплексором 406, который принимает сигнал 228 в качестве управляющего. Двухвходовый элемент ИЛИ 408 принимает на вход сигналы 122 и 210. Выход 410 соединен с демультиплексором 412. Выходами демультиплексора 406 являются k шин 320, а выходами демультиплексора 412 является k сигналов 322. K регистров 324 принимают на вход соответствующие шины 320 и сигналы 322. Выходами k регистров являются шины 126, которые поступают также на мультиплексор 326. Он принимает сигнал 228 в качестве управляющего. Выход мультиплексора соединен с выходом 124. N-входовый элемент И 328 принимает на вход шину 312. Выходом n-входового элемента И является сигнал 220. Также выход 220 соединен со входом мультиплексора 502 вместе с шиной 118. Выход мультиплексора 504 соединен с демультиплексором 506. Двухвходовый элемент ИЛИ 508 принимает на вход сигналы 122 и 210. Выходы 510 и 336 соединены со входом двухвходового элемента И 512. Выход 514 соединен со входом демультиплексора 516. K выходов 338 и 340 соединены со входами регистров 342. K выходов регистров 344 соединены со входами мультиплексора 346, управляющий вход которого соединен с выходом 228. Выход из мультиплексора 222, соединен с шиной 124. Двухвходовый элемент И 350 принимает на вход сигналы 220 и 222. На вход мультиплексору 522 поступают сигналы 224 и 118. Выход 524 соединен с входом демультиплексора 526. На вход двухвходового элемента ИЛИ 528 поступают сигналы 122 и 210. Выход 530 соединен с входом двухвходового элемента И 532 вместе с 214. Выход 534 соединен с входом демультиплексора 536. K выходов 356 и 358 соединены соответственно с входами регистров 360. K выходов регистров 362 соединены с входами мультиплексора 364, управляющий вход которого соединен с выходом 228. Выход мультиплексора соединен с 124.

На фиг. 6 описан состав блока управляющей логики. Двухвходовый элемент ИЛИ 602 принимает на вход сигналы 210 и 222. Его выход 604 соединен со входом счетчика исправных блоков 606. Выход счетчика 608 соединен со входом компаратора 610. Его выходом является 114. Счетчик резервных элементов 612 принимает на вход сигнал 224, а его выход 614 соединен со входом компаратора 616. Его выходом является 116. Счетчик обработанных блоков принимает на вход сигнал 210, а его выход соединен с мультиплексором 622, который также принимает сигнал 122 в качестве управляющего. Выходом мультиплексора является 228.

Аппаратная операция саморемонта для каждого блока памяти проводится с помощью алгоритма, изображенного на фиг. 7, 8, и 9.

После инициирования операции саморемонта 702, обнуления счетчика операций самотестирования 704, запуска самотестирования 706, окончания самотестирования и записи результатов самотестирования в регистры диагностики 708 счетчик обработанных блоков равен нулю 710.

Автомат состояний сравнивает количество обработанных блоков с полным количеством блоков 712. Если обработаны результаты самотестирования не всех блоков, то происходит чтение результатов самотестирования для следующего блока памяти из соответствующего регистра диагностики 714. Далее происходит проверка значения счетчика операций самотестирования 716. Если завершилась первая операция самотестирования (счетчик операций самотестирования равен 0), то произойдет переход А, в противном случае - Б. Если анализируются данные первой операции самотестирования, то запись данных в регистры конфигурации резервных элементов и проверки резервных элементов будут осуществляться по переходу А в соответствии с фиг. 8. Будет проверена шина диагностики соответствующего блока памяти 802. Если все разряды шины диагностики равны нулю, это означает, что при тестировании основных элементов памяти ошибок не обнаружено. Тогда будет выставлен флаг проверки резервных элементов 804, а регистр конфигурации резервных элементов будет сконфигурирован шифратором для работы с резервными элементами 806 для проверки их работоспособности. Если шина диагностики содержит информацию об ошибках, то шифратор определит, исправима ли она 808. Если ошибка исправима, то соответствующий регистр конфигурации резервных элементов будет сконфигурирован для замены поврежденных основных элементов 810. В противном случае соответствующий регистр конфигурации резервных элементов останется неизмененным 812. После шагов 806, 810 и 812 будет осуществлен переход в соответствии с В к 718. Счетчик обработанных блоков будет увеличен на 1.

Если анализируются данные повторной операции самотестирования (СОСТ = = 1), то запись данных в регистры конфигурации резервных элементов, проверки резервных элементов и исправности резервных элементов будут осуществляться по переходу Б в соответствии с фиг. 9. Будет проверен флаг проверки резервных элементов 902. Если он равен единице, то это означает, что основные элементы в этом блоке памяти исправны. Флаг проверки резервных элементов будет сброшен в ноль также как и шина конфигурации резервных элементов 904. Будет проверена шина диагностики соответствующего блока памяти 906. Если все разряды шины диагностики равны нулю, это означает, что при тестировании памяти с резервными элементами ошибок не обнаружено. Тогда будет выставлен флаг исправности резервных элементов 908, а счетчик исправных элементов будет увеличен на единицу 910. Если на шине диагностики присутствуют единицы, это означает, что память имеет неисправные резервные элементы. В этом случае флаг исправности резервных элементов останется равным единице 912. Если для соответствующего блока памяти флаг проверки резервных элементов не был выставлен, это означает, что для блока основных элементов были обнаружены ошибки в ходе первой операции самотестирования. Будет проверена шина диагностики соответствующего блока памяти 914. Если ошибок не обнаружено, то блок признается успешно исправленным и счетчик исправных блоков увеличивается на единицу 916. В противном случае соответствующая шина конфигурации резервных элементов будет обнулена 918. После шагов 910, 912, 916 и 918 будет осуществлен переход в соответствии с В к 718.

Когда обработаны данные диагностики всех блоков памяти 712, то выполняется проверка счетчика операции самотестирования. Если проведена лишь одна операция самотестирования, то счетчик операций самотестирования становится равным единице 722 и происходит инициирование второй операции самотестирования.

Если была проведена обработка данных после второй операции самотестирования, то будет проверен счетчик исправных блоков 724. Если количество исправных блоков равно полному количеству блоков, то будет проверен счетчик исправных резервных элементов. Если он равен полному количеству блоков, то выставляются в единицу сигналы окончания операции саморемонта 112, статуса операции саморемонта 114 и исправности резервных элементов 116. Если счетчик исправных резервных элементов не равен полному количеству блоков, то выставляются в единицу сигналы окончания операции саморемонта 112 и статуса операции саморемонта 114, а сигнал исправности резервных элементов 116 остается равным 0. Если количество исправных блоков не равно полному количеству блоков, то выставляется в единицу сигнал окончания операции саморемонта 112, а сигналы статуса операции саморемонта 114 и сигнал исправности резервных элементов 116 остаются равными 0.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления булевых дифференциалов | 1980 |

|

SU940166A1 |

| Адаптивное к экстренным ситуациям устройство передачи телеметрической информации | 2017 |

|

RU2654169C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| СПОСОБ ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ И УСТРОЙСТВО ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ | 2014 |

|

RU2592465C2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Изобретение относится к области вычислительной техники, а именно к системам на кристалле, содержащим внутреннюю память с резервными элементами и встроенные блоки самотестирования. Технический результат заключается в обеспечении возможности использования резервных элементов памяти в процессе работы микросхемы путем снабжения устройства выходным сигналом исправности резервных элементов. Устройство встроенного саморемонта памяти с резервными элементами включает автомат состояний, блок управляющей логики и генератор конфигурации резервных элементов. 2 з.п. ф-лы, 9 ил.

1. Устройство встроенного саморемонта памяти с резервными элементами, содержащее блок управляющей логики (БУЛ), генератор конфигурации резервных элементов (ГКРЭ), автомат состояний (АС), выходной сигнал статуса операции саморемонта (CP) БУЛ поступает на выход статуса операции CP устройства, выходной сигнал разрешения записи в регистры диагностики (РД) АС поступает на вход разрешения записи в РД ГКРЭ, выходной сигнал разрешения записи в регистры конфигурации резервных элементов (РКРЭ) АС поступает на вход разрешения записи в РКРЭ ГКРЭ, отличающееся наличием входного сигнала старта операции CP в аппаратном режиме, поступающего на вход старта операции CP в аппаратном режиме АС, входного сигнала старта операции CP в программном режиме, поступающего на вход старта операции CP в программном режиме АС, входного сигнала окончания операции СТ, поступающего на вход окончания операции СТ AC, k входных шин диагностики (ШД), соединенных с соответствующими входами ШД ГКРЭ, k выходных шин конфигурации резервных элементов (ШКРЭ) ГКРЭ, выходного сигнала исправности резервных элементов (ИРЭ) ГКРЭ, поступающего на вход ИРЭ БУЛ, выходного сигнала окончания операции CP АС, входной шины записи данных интерфейса управления (ИУ), соединенной с входной шиной записи данных ИУ ГКРЭ, входной шиной адреса ИУ, соединенной с входной шиной адреса ИУ ГКРЭ и входной шиной адреса ИУ БУЛ, входного сигнала разрешения записи ИУ, поступающего на вход разрешения записи ИУ ГКРЭ и вход разрешения записи ИУ БУЛ, выходной шиной чтения данных ИУ, соединенной с выходной шиной чтения данных ИУ ГКРЭ, выходного сигнала счетчика операций СТ АС, поступающего на вход счетчика операций СТ ГКРЭ, выходного сигнала разрешения записи в РКРЭ АС, поступающего на вход разрешения записи в РКРЭ БУЛ, выходного сигнала статуса операции СТ ГКРЭ, поступающего на вход статуса операции СТ БУЛ, выходного сигнала флага проверки резервных элементов (ФПРЭ) ГКРЭ, поступающего на вход ФПРЭ БУЛ, выходного сигнала флага исправности резервных элементов (ФИРЭ) ГКРЭ, поступающего на вход ФИРЭ БУЛ, выходного сигнала счетчика обработанных блоков (СОБ) БУЛ, поступающего на вход СОБ АС и вход СОБ ГКРЭ.

2. Устройство встроенного саморемонта памяти с резервными элементами по п. 1, отличающееся тем, что ГКРЭ содержит k блоков по n двухвходовых элементов ИЛИ, где k - количество блоков памяти, с которыми работает устройство, а n - разрядность информационного слова, хранящегося в каждом блоке памяти, k РД уменьшенной разрядности, первый мультиплексор, шифратор КРЭ, второй мультиплексор, первый двухвходовый элемент ИЛИ, первый и второй демультиплексоры, k регистров для хранения конфигурации резервных элементов (РКРЭ), третий мультиплексор, n-входовый элемент И, первый инвертор, четвертый мультиплексор, второй двухвходовый элемент ИЛИ, первый двухвходовый элемент И, третий и четвертый демультиплексоры, k регистров флагов проверки резервных элементов (РФПРЭ), пятый мультиплексор, второй двухвходовый элемент И, шестой мультиплексор, третий двухвходовый элемент ИЛИ, третий двухвходовый элемент И, пятый и шестой демультиплексоры, k регистров флагов исправности резервных элементов (РФИРЭ) уменьшенной разрядности, седьмой мультиплексор, причем каждый из k блоков по n двухвходовых элементов ИЛИ соединен с соответствующей входной ШД и выходом соответствующей ячейки РД; на каждый из k РД поступают сигналы с соответствующих выходов блоков по n двухвходовых элементов ИЛИ и сигнал разрешения записи в РД; вход первого мультиплексора соединен с k выходами из k РД, на управляющий вход первого мультиплексора поступает сигнал СОБ, а его выходы соединены с выходной шиной чтения данных ИУ; вход шифратора КРЭ соединен с выходом первого мультиплексора, выходом счетчика операций СТ, выходом пятого мультиплексора; вход второго мультиплексора соединен с выходом шифратора КРЭ, шиной записи данных ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ; вход первого демультиплексора соединен с выходом второго мультиплексора, а на управляющий вход поступает сигнал СОБ; на вход первого двухвходового элемента ИЛИ поступает сигнал разрешения записи в РКРЭ и сигнал разрешения записи по ИУ; вход второго демультиплексора соединен с выходом первого двухвходового элемента ИЛИ, а на управляющий вход поступает сигнал СОБ; входы каждого из k РКРЭ соединены с соответствующими выходами первого и второго демультиплексоров, а их выходы соединены с k выходными ШКРЭ; входы третьего мультиплексора соединены с k выходами из РКРЭ, а на управляющий вход поступает сигнал СОБ; входы первого n-входового элемента И соединены с выходами первого мультиплексора, а его выход является выходом статуса операции СТ ГКРЭ; вход четвертого мультиплексора соединен с выходом первого n-входового элемента И, шиной записи данных ИУ, а на управляющих вход поступает сигнал разрешения записи ИУ; вход третьего демультиплексора соединен с выходом четвертого мультиплексора, а на управляющий вход поступает сигнал СОБ; второй двухвходовый элемент ИЛИ принимает на вход входной сигнал разрешения записи в РКРЭ и сигнал разрешения записи ИУ; первый инвертор принимает на вход входной сигнал счетчика операций СТ; вход первого двухвходового элемента И соединен с выходом второго двухвходового элемента ИЛИ и выходом первого инвертора; вход четвертого демультиплексора соединен с выходом первого двухвходового элемента ИЛИ, а на управляющий вход поступает сигнал СОБ; входы каждого из k РФПРЭ соединены с соответствующими выходами третьего и четвертого демультиплексоров; вход пятого мультиплексора соединен с k выходами РФПРЭ, на управляющий вход поступает сигнал СОБ, а его выход соединен с выходной шиной чтения данных ИУ; вход второго двухвходового элемента И соединен с выходом первого n-входового элемента И и выходом пятого мультиплексора; вход шестого мультиплексора соединен с выходом второго двухвходового элемента И, со входной шиной записи данных ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ; вход пятого демультиплексора соединен с выходом шестого мультиплексора, а на управляющий вход поступает сигнал СОБ; третий двухвходовый элемент ИЛИ принимает на вход входной сигнал разрешения записи в РКРЭ и сигнал разрешения записи ИУ; на входы третьего двухвходового элемента И поступает сигнал с выхода третьего двухвходового элемента ИЛИ и сигнал счетчика операций СТ; вход шестого демультиплексора соединен с выходом третьего двухвходового элемента И, а на управляющий вход поступает сигнал разрешения записи ИУ; вход каждого из k РФИРЭ соединен с соответствующими выходами пятого и шестого демультиплексоров; вход седьмого мультиплексора соединен с k выходами РФИРЭ, на управляющий вход поступает сигнал СОБ, а выход соединен с шиной чтения данных ИУ.

3. Устройство встроенного саморемонта памяти с резервными элементами по п. 1, отличающееся тем, что БУЛ содержит первый двухвходовый элемент ИЛИ, счетчик исправных блоков, первый компаратор, счетчик блоков с исправными резервными элементами, второй компаратор, СОБ, первый мультиплексор, причем первый двухвходовый элемент ИЛИ принимает на вход входной сигнал ФПРЭ и входной сигнал разрешения записи в РКРЭ; вход счетчика исправных блоков соединен с выходом первого двухвходового элемента ИЛИ; вход первого компаратора соединен с выходом счетчика исправных блоков, выходным сигналом первого компаратора является сигнал статуса операции CP; счетчик исправных резервных элементов принимает на вход входной сигнал ФИРЭ; вход второго компаратора соединен с выходом счетчика исправных резервных элементов, выходным сигналом второго компаратора является сигнал ИРЭ; СОБ принимает на вход входной сигнал разрешения записи в РКРЭ; вход первого мультиплексора соединен с выходом СОБ, с входной шиной адреса ИУ, а на управляющий вход поступает сигнал разрешения записи ИУ.

| ЩИГОРЕВ Л.А | |||

| "Организация саморемонта блоков статической оперативной памяти с резервными элементами" | |||

| Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС) | |||

| Сборник трудов / под общ | |||

| ред | |||

| академика РАН А.Л | |||

| Стемпковского, Москва: ИППМ РАН, 2016, Часть III, стр | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| US 7913125 B2, 22.03.2011 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| US 7949908 B2, 24.05.2011 | |||

| US 6691264 B2, 10.02.2004. | |||

Авторы

Даты

2018-09-24—Публикация

2017-11-28—Подача