I

Изобретение относится к корреляционным измерителям скорости и может быть использовано при разработке и эксплуаташш измерителей скорости.

Известны конструкции корреляционнь Х измерителей скорости, основу которых составляют, генератор, вибраторы-излучатели, вибраторы приемники, регистры сдвига, логическое устройство, реверсивный счетчик, управляемый делитель частоты, генераторо тактовых импульсов, счетчик пройденного пути 111 .

Известен также корреляционный измеритель скорости, содержащий генератор, соединенный с вибратором-излучателем, два вибратора-приемника, выходы которых подключены соответственно к первому и второму усилителю-ограничителю, многоразрядный регистр сдвига, прямой выход которого соединен со входом первого одноразрядного регистра, сдвига, первое логическое устройство, состоящее из четырех триггеров и четырех трехвходовых схем И, первые входы которых подключены к выходу генератора тактовых импульсов, вторые входы - к выходам соответствующих триггеров, а третьи входы - к выходу первого усилителя-ограничителя, выходы первой и второй схем И соединены со входами первой схемы ИЛИ, а третьей и четвертой схем И - со входами второй схемы ИЛИ, выходы схем ИЛИ подключены ко входам реверсивного счетчика, выходы

10 которого соединены с управляющими уходами управляемого делителя частоты, тактовый вход которого подключен к выходу генератора тактовых импул(лов, а выход - к счетчику пройденного пути

15 и к тактовым входам регистров сдвига 2.

Однако известная конструкция корреляционного измерителя скорости имеет ощибки в определении скорости, обусловленные декорреляцией сигналов при качке объекта и больщих углах дрейфа.

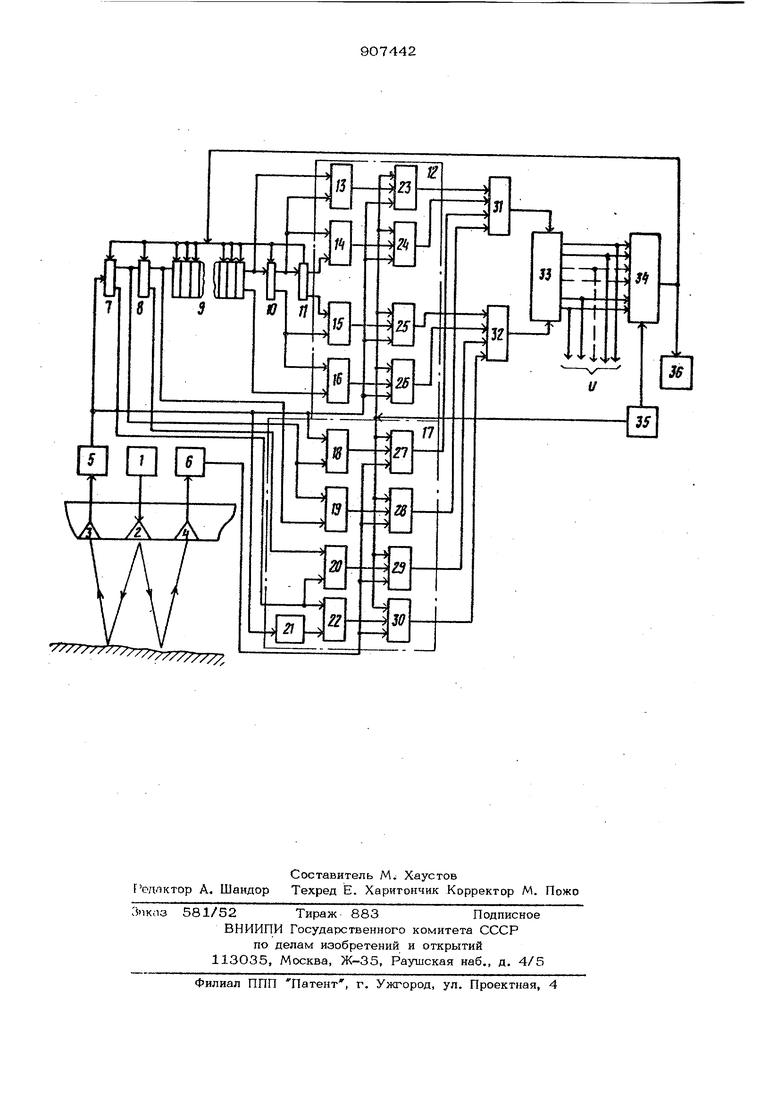

Цель изобретения - повьпление точности и устойчивости работы за счет определения в-ременной задержки 39лов по коэффициенту автокорреляции огибающей сигнала одного из приемников, равного значению коэффиш1ента взаимной корреляции огибающих сигналов двух приемников. Указанная цель достигается тем, что измеритель снабжен тремя одноразрядны регистрами сдвига и вторым логическим устройством, состоящим из схемы НЕ, четырех триггеров и четырех трехвхо10ВЫХ схем И, первые входы которых соединены с выходом генератора тактовых импульсов, вторые входы - с выходами соответствующих триггеров, а трет входы - с выходом второго усилителяограничителя, выходы первой и второй схем И подключены ко входам первой схемы ИЛИ, а третий и четвертый - ко входам второй схемы ИЛИ, выход первого усилителя-ограничителя соединен со входом второго одноразрядного регистра сдвига, инверсный выход которого подключен к первым входам третьего и четвертого триггеров второго логического устройства, а прямой выход - к первым25 входам первого и второго триггеров второго логического устройства и ко входу третьего одноразрядного регистра сдвига, инверсный выход которого соединен со вторым входом третьего триггера второго лопгческого устройства, а прямой выход-с вторым входом второго триггера второго лог1гческого устройства и со входом многоразрядного регистра сдвига, инверсный выход которого подключен к первому входу четвертого триггера первого логического устройства, а прямой выход - к первому входу первого триггера первого логического устройства, второй вход которого соединен с прямым выходом первого одноразрядного регистра сдвига, со входом четвертого одноразрядного регистра сдвига и с первым входом второго триггера первого логического устройства, второй вход которого подключен к прямому выходу четвертого одноразрядного регистра сдвига, инверсный выход которого соединен с первым входом третьего триггера, первого логического устройства, второй вход которого подключен к инверсному выходу первого одноразрядного регистра сдвига и ко второму входу четвертого триггера первого логического устройства,- выход первого усилителя огра Н1гчителя соединен со вторым входом первого триггера, а через схему НЕ - со вторым входом четвертого триггера второго логического устройства, при этом тактовые входы введенных регистров 2 подключены к выходу управляемого делителя частоты. На чертеже изображена схема корреляционного измерителя скорости. Устройство содержит генератор 1, вибратор-излучатель 2, вход которого подключен к выходу генератора 1, два вибратора-приемника 3 и 4, два усилителя-ограничителя 5 и 6, входы которых подключены к выходам вибраторов-приемников 3 и 4, одноразрядный регистр сдвига 7, один вход которого подключен к выходу усилителя-ограничителя 5, одноразрядный оегистр сдвига 8, к одному входу которого подключен прямой выход одноразрядного регистра сдвига 7, многоразрядный регистр сдвига 9, к одному входу которого подключен прямой выход одноразрядного регистра 8, одноразрядный регистр сдвига 10, к одному входу которого подключен прямой выход многоразрядного регистра сдвига 9, одноразрядный регистр сдвига 11, к одному входу которого подключен прямой выход одноразрядного регистра сдвига 1О, первое логическое устройство 12, содержащее триггер 13, ко входам которого подключены прямые выходы многоразрядного и одноразрядного регистров сдвига 9 и 1О, триггер 14, ко входам которого подключены прямые выходы одноразрядных регистров сдвига 10 и 11, триггер 15, ко входам которого подключены инверсные выходы одноразрядных регистров сдвига 1О и 11, триггер 16, ко входам которого подключены инверсные выходы многоразрядного и одноразрядного регистров сдвига 9 и 10, второе логическое устройство 17, содержащее триггер 18, ко входам которого подключены выход усилитеЛя-ограничителя 5 и прямой выход одноразрядного регистра сдвига 7, триггер 19, ко входам которого подключены прямые выходы одноразрядных регистров сдвига 7 и 8, триггер 20, ко входам которого подключены инверсные выходы одноразрядных регистров сдвига 7 и 8, схему НЕ 21, вход которого подключен к выходу усилителя-ограничителя 5; триггер 22, ко входам которого подключены инверсный выход одноразрядного регистра 7 и выход схемы НЕ, схемы И 23 - 26, относящиеся к первому логическому устройству, к одним входам которых подключены выходы триггеров 13 - 16 к другим входам - выход усилителя-ограничителя 5, схемы И 27 - 30, относящиеся ко второму логическому устройству, к одним входам которых под-

ключены выходы триггеров 18-22 к другим входам - выход усилитрпя-ограничитепя 6, схему объединения ИЛИ 31, ко входам которой подключены выходы схем И 23, 24, 27, 28, схему ИЛИ 32 объединения, ко входам которой подклк чены выходы схем И 25, 26, 29, 30, реверсивный счетчик 33 импульсов, ко ьходам которого подключены выходы рхем объединения 31, 32, управляемый |делитёль 34 частоты, к одним входам (Которого подключены выходы реверсивi:ioro счетчика 33 импульсов, а выход управляемого делителя частоты.подключе к другим входам одноразрядных регистров Сдвига 7, 8, 10, 11 и многоразрядного регистра сдвига 9, генератор 35 тактовы импульсов, выход которого подключен к другому входу управляемого дели теля частоты и к третьим входам схем И 2328, счетчик 36 пройденного пути, вход которого подключен к выходу управляемого делителя 34 частоты.

Предлагаемая работает следующим образом.

Генератор 1 вырабатывает электрический гармонический сигнал, который подается на вибратор-излучатель 2, где преобразуется в акустический сигнал и излучается вниз. Отраженный от дна

акустический сигнал принимается вибраторами-приемниками 3, 4, где преобразуетс в электрические сигналы X(-t) , (-t-t t j, которые подаются на усилители-ограничители 5 и 6. Усилители-ограничители 5 и 6 преобразуют огибающие электрически сигналов в сигнум-сигналы SiOjn X(t) и SlQ;n + C). Сигнум-сигнал с выхода усилителя-ограничителя 5 поступает на регистры сдвига 7 - 11 где этот сигнал квантуется по времени с частотой импульсов управляемого делителя частоты 34 и задерживается в каждом регистре сдвига на время, определяемое разрядностью регистров сдвига 7 - 11 и частотой следования импульсов управляемого делителя частоты 34. Триггеры 13, 14, 18, 19 запускаются передними фронтами сигнум-сигнала с прямых выходов регистров 9 и 10 сдвига, усилителя-ограничителя 5 и одноразрядного регистра 7 сдвига, а сбрасываются передними фронтами сигнум-сигнала с прямых выходов регистра сдвига 10, 11, 7, 8.

Триггеры 15, 16, 2О, 22 запускаютС(Я передними фронтами сигнум-сигнала с инверсных выходов регистров сдвига 10, 9, 7 и с выхода схемы НЕ 21,

а сбрасываются передними фронтами сигнум-сигнала с инверсных выходов регистров сдвига 11, 10, 8, 7. Количество и длительность импульсов с выхода триггеров определяется спектро частот сигнум-сигнала, разрядностью регистров и частотой следования импулЕзСов управляемого делителя частоты Импульсы с выхода триггеров 13, 14, 15, 16, 18, 19, 20, 22 поступают на первые входы схем совпадения И 23 30, на вторые входы которьгх подаются импульсы с выхода генератора .35 тактвых импульсов. На третьи входы схем И 23 - 26 поступают сигнум-сигналы с выхода усилителя-ограничителя 5, а на третьи входы схем И 27-30 сигнум-сигналы с выхода усилителя-ограничителя 6. Импульсы с выходов схем И 23, 24, 27, 28 поступают на входы схемы ИЛИ 31 объединения, с выхода которой импульсы поступают на суммирующий вход реверсивного счетчика 33 I импульсов. Импульсы с выходов схем И 25, 26, 29, 30 поступают на входы iсхемы ИЛИ 32 объединения, с выхода которой импульсы поступают ни вычитающий вход реверсивного счетчика 33 импульсов. Текущее состояние разрядов реверсивного счетчика 33 импульсов является мерой скорости движения объета и определяет коэффициент деления управляемого делителя 34 частоты, на второй вход которого подаются импульс с генератора 35 тактовых импульсов.

При равенстве величины задержки сигнум-ст нала в регистрах сдвига временной задер:жки, при которой функции автокорреляции сигнум-cin Hajja с выхода усилителя-ограничителя 5 равн величине функции взаимной корреляции сигнум-сигнала с выходов усилителейограничителей 6 и 5, количество импульс выходов 1.хем ИЛИ 31 и 32 будет равн состояние реверсивного счетчика изменяться не будет и частота следования импульсов с выхода управляемого делителя частоты не будет изменяться.

Если величина задерхжи сигнум-сигнала в регистрах сдвига не равна временной задержке, при которой величина функции автокорреляции cin nyM-сигиала с выхода усилителя-ограшгчителя 5 равн величине функции взаимной корреляции сигнум-сигнала с выходов усилителей ограничителей 5, 6, количество импульсов с выходов схем ИЛИ 31, 32 не будет равно, состояние реверсивного счетчика будет изменяться, что при7,9 ведет Е изменению коэффициента деле-ПИЯ управляемого делителя 34 частоты, 1ЕЗменится частота тактовых импульсов н разница в количестве им тульсов с выхода схем ИЛИ 31, 32 исчезнет Мгновенное состояние разрядов реверсивного счетчика 33 импульсов позволяет получить информаш5го о скорости, а количес1ъ импульсов с выхода управляемого делителя 34 частоты, посчитанное счетчиком 36 пройденного пути - о пройденном пут Применение такой схемы построения корреляш{онного измерителя скорости поз воляет за счет ввода второго логического устройства и трех oднopaзpядньLX регистр сдвига повысить точность и устойчивост работы. Формула и 3 о б р е т 9 н и я Коррехшш5онный измеритель скорости, содержащий генератор, соединенный с вибратором-излучателем, два вибратораприемника, выходы которых подключены соответственно к перво и второму усилител1о ограничителю, многоразряд- ift.m регистр , прямой выход кото™ iporo соединен со входом первого одноразрядного регистра сдвига, первое логическое устройство, состоящее из четырех триггеров и четырех трехвходовых схем И, первые входы которых подклю™ че}гы к выходу генератора талстовых пульсов, вторые входы - к выходаг. соответствующих триггеров, а третьи входы к выходу первого усилнтепяогра 1ичитепя, выходы первой и второй сх®л И соединены со входами первой cxetvtM ИЛИ. а третьей и четвертой, схем И - со входами второй схемы ИЛИ выходы схем ИЛИ подключены ко входам реверсивного счетчика, выходы которого соединены с управляющими входами уп 1завляемого делителя частоты, тактовый вход которого подключен к выходу генератора тактовых импульсов, а выход - к счетчику нровденного тгути и к тактовым вхо/хам регистров сдвет а, о т л и ч а ю щ и и с я тем, что, с целью повышения точности 3i :устойчивости работы, измеритель снабжен тремя одноразрядными peincTpaMii сдвига и вторым лог гаеским устройством, состоящим из схемы. ME, четырех трш/теров 5 четырех трехвхо- дойых схем И, перрие входы которых соединены с вы.ходск1 г-ене)атора такто- БЫХ импульсов, ВТОрЫО - С ВЫХО-дами соответствующих трш-Г ров, а третр,и входы - с выходом второго усилителяограничителя, выходы первой и второй схем И подключены ко входам первой схемы ИЛИ, а третий и четвертый - ко входам второй схемы ИЛИ, выход первого усилителя-ограничителя соединен со входом второго одноразрядного регистра сдвига, иттерсный выход которого подключен к первым входам третьего и четвертого триггеров второго логического устройства, а прямой выход - к первым входам первого и второго триггеров второго логического устройства и ко входу третьего одноразрядного регистра сдБзп: а, инверсный выход которого соединен со вторым входам третьего триггера второго логического устройства, а прямой выход - со вторым входом второго триг гера второго лог ического устройства и со входом многоразрядного регистра сдвига, инверсный выход которого подключен к первому входу четвертого тригрега первого логического устройства, а прямой выход - к первому входу первого тр птера первого логического устройства, второй вход которого соединен с прямым выходом первого одноразрядного регистра сдвгп а, со входом четвер- TOio одноразрядного регистра сдвига и с первым входом второго триггера первого логического устройства, второй вход которого подключен к прямому выходу четвертого одноразрядного регистра сдвига, инверсный выход которого соединен с первым входом третьего триггера первого логического устройства, второй .вход которого подключен к инверсному выходу первого одноразряд1 ого регистра сдвша и ко второму входу четвертого тригг-гера первого логического устройства, выход первого усилителя-ограничителя соединен со вторым входом первого триггера, а через схему НЕ - со вторым входом четвертого тр , второго логического устройства, при этом тактовые входы введенных регистров подключены к выходу управляемого делителя частоты. Источники информащ™, финятые во шшмапие npi: экспертизе 1,. Авторское свидетельство CXifJP № 466453, кп. G О1 Р 3/64, . 2, Патент ФРГ М 2345106, кл, а О1 F 3/64, опублик. 1 П7Г (ilpOTOTHu).

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционный измеритель скорости | 1980 |

|

SU907441A1 |

| Корреляционный измеритель скорости | 1982 |

|

SU1070482A1 |

| Корреляционный измеритель скорости | 1984 |

|

SU1275294A1 |

| Корреляционный измеритель скорости | 1984 |

|

SU1163271A1 |

| Корреляционный измеритель скорости | 1982 |

|

SU1040418A1 |

| Корреляционный измеритель скорости проскальзывания | 1983 |

|

SU1083119A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Измеритель элементов матрицы спектральной плотности мощности двух сигналов | 1989 |

|

SU1661667A2 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Корреляционный измеритель скорости | 1979 |

|

SU890251A1 |

Авторы

Даты

1982-02-23—Публикация

1980-07-11—Подача