совпадения отпирается, на счетчик 19 /поступают сигналы и отслеживается скорость движения объекта. При срыве режима слежения за положением максимума взаимной корреля1ц-1онной функции входных сигналов сигналы с вьосода схемы 15 совпадения будут вычитаться из содержимого счетчика 19. Как только его содержимое станет равным заданному минимальному двоичному числу, соответствующему .минимальной частоте следования тактовых импульсов на выходе делителя 2 частоты, на выходе дешифратора 26 появится сигнал, запускающий формирователь 20, и в счетчике 19 будет число, соответствующее максимально измеряемой скорости. 1 ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционный измеритель скорости | 1982 |

|

SU1070482A1 |

| Корреляционный измеритель скорости | 1980 |

|

SU907442A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Корреляционный измеритель скорости | 1986 |

|

SU1357847A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

Изобретение относится к приборостроению и позволяет уменьшить погрешности и повысить устойчивость работы измерителя при больших ускорениях подвижного объекта. При появлении рассогласования такой величины, что сигналы с выхода формирователя 17 будут совпадать с сигналами с выхода схемы 25 объединения, на выходе схемы 16 совпадения появится сигнал, записываемый в триггере 18. Схема 14 W СП ГчЭ СО 4

Изобретение относится к приборостроению и может быть использовано для построения измерителей скоростей подвюкных объектов.

Цель изобретения - уменьшение погрешности и повышение устойчивости работы измерителя при больших ускорениях подвижного объекта.

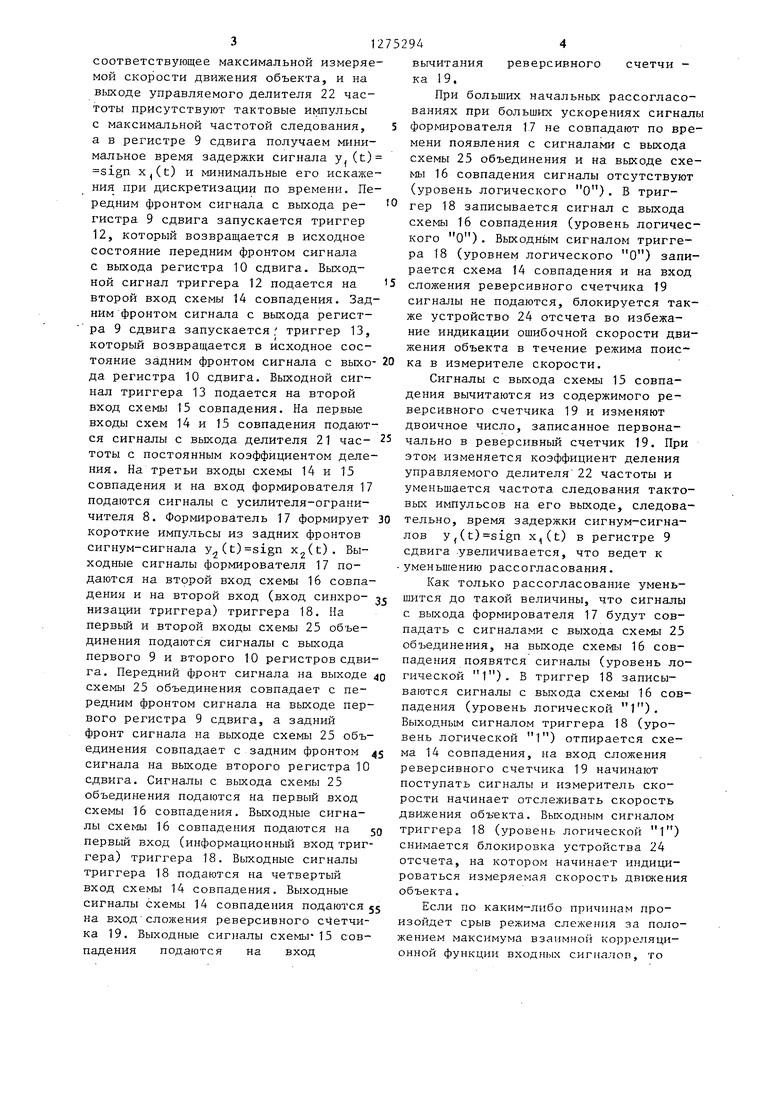

На чертеже представлена блок-схема корреляционного измерителя скорости.

Измеритель содержит генератор 1, выход которого подключен к вибраторуизлучателю 2, два вибратора-приемника 3 и 4, выходы которых подключены к усилителям 5 и 6 с амплитудным детектированием, соединенным с усилителями-ограничителями 7 и 8, регистр 9 сдвига, подключенный к усилителюограничителю 7 первого канала, регистр 10 сдвига3 подключенный к первому регистру 9 сдвига, решающее логическое устройство 11 j содержаш,ее два триггера 12 и 13, подключенные к выходам первого 9 и второго 10 регистров сдвига, и две схемы 14 и 15 совпадения, подключенные к двум триггерам 12 и 13 и усштителю-ограничителю 8 второго канала, схему 16 совпадения, подключенную к выходам схемы 25 объединения и формирователя 17, последний подключен к усилителю-ограничителю 8 второго канала; триггер 18, .входы которого подключены к схеме 16 совпадения и формирователю 17, а выход - к входам cxBMFji 14 совпадения и устройства 24 отсчета; реверсивный счетчик 19, подключенный к выходам схем 14 и 15 совпадения и выходу формирователя 20, делитель 21 частоты с постоянным коэффициентом деления, вход которого подключен к управляемому делителю 22 частоты, а выход к входам схем 14 и 15 совпадения, управляемый делитель 22 частоты, входы которого подклв чены к выходам реверсивного счетчика 19 и генератора 23 тактовых импульсов, устройство 24 отсчета, подключенное к выходам управляемого делителя 22 частоты и триггера 18j схемз 25 объединения, входы которой подключены к выходам первого 9 и второго 10 регистров сдвига, а выход подключен к входу схемы 16 совпадения; дешифратор 26, входы которого подключены к выходам реверсивного счетчика 19, а выход к входу формирователя 20.

Электрический гармонический сигнал с генератора 1 подается на вибраторизлучатель 2, где он преобразуется в акустический сигнал, который излучается вертикально вниз и отражается от дна. Отраженный сигнал принимается двумя вибраторами-приемниками 3 и 4, где акустический сигнал преобразуется в электрический и усиливается затем усилителяг-ш 5 и 6 с амплитудным детектированием. С выходов этих усилителей сигналы поступают на усилители-ограничители 7 и 8. С выхода усилителя-ограничителя 7 сигнумсигнал y,(t)sign x(t) подается на вход регистра 9 сдвига, число разрядов которого больше числа разрядов регистра 10 сдвига. С выхода усихгителя-ограничителя 8 сигнум-сигнал ) sign x(t) подается на входы схем 14 и 15совпадения и на вход формирователя 17. При включении питания измерителя скорости формирователь 20 записывает в каскадь реверсивного счетчика 19 максимальное двоичное число.

соответствующее максимальной измеряемой скорости движения объекта, и на выходе управляемого делителя 22 частоты присутствуют тактовые импульсы с максимальной частотой следования, а в регистре 9 сдвига получаем минимальное время задержки сигнала у (t) sign хДс) и минимальные его искажения при дискретизации по времени. Передним фронтом сигнала с выхода регистра 9 сдвига запускается триггер 12, который возвращается в исходное состояние передним фронтом сигнала с выхода регистра 10 сдвига. Выходной сигнал триггера 12 подается на второй вход схемы 14 совпадения. Задним фронтом сигнала с выхода регистра 9 сдвига запускается. триггер 13, которьш возвращается в исходное состояние задним фронтом сигнала с выхода регистра 10 сдвига. Выходной сигнал триггера 13 подается на второй вход схемы 15 совпадения. На первые входы схем 14 и 15 совпадения подаются сигналы с выхода делителя 21 частоты с постоянным коэффициентом деления. На третьи входы схемы 14 и 15 совпадения и на вход формирователя 17 подаются сигналы с усилителя-ограничителя 8. Формирователь 17 формирует короткие импульсы из задних фронтов сигнум-сигнала у (t)sign x(t). Выходные сигналы формирователя 17 подаются на второй вход схемы 16 совпадения и на второй вход (вход синхронизации триггера) триггера 18. На первый и второй входы схемы 25 объединения подаются сигналы с выхода первого 9 и второго 10 регистров сдви га. Передний фронт сигнала на выходе схемы 25 объединения совпадает с передним фронтом сигнала на выходе первого регистра 9 сдвига, а задний фронт сигнала на выходе схемы 25 объединения совпадает с задним фронтом сигнала на выходе второго регистра 10 сдвига. Сигналы с выхода схемы 25 объединения подаются на первый вход схемы 16 совпадения. Выходные сигналы схемы 16 совпадения подаются на первый вход (информационньш вход триг гера) триггера 18. Выходные сигналы триггера 18 подаются на четвертый вход схемы 14 совпадения. Выходные сигналы схемы 14 совпадения подаются на входсложения реверсивного счетчика 19. Выходные сигналы схемы-15 совпадения подаются на вход

вычитания реверсивного счетчи ка 19.

При больших начальных рассогласованиях при больш1-гх ускорениях сигналы формирователя 17 не совпадают по времени появления с сигналами с выхода схемы 25 объединения и на выходе схемы 16 совпадения сигналы отсутствуют (уровень логического О). В триггер 18 записывается сигнал с выхода схемы 16 совпадения (уровень логического О). Выходным сигналом триггера 18 (уровнем логического О) запирается схема 14 совпадения и на вход сложения реверсивного счетчика 19 сигналы не подаются, блокируется также устройство 24 отсчета во избежание индикации ошибочной скорости движения объекта в течение режима поиска в измерителе скорости.

Сигналы с выхода схемы 15 совпадения вычитаются из содержимого реверсивного счетчика 19 и изменяют двоичное число, записанное первоначально в реверсивный счетчик 19. При этом изменяется коэффициент деления управляемого делителя22 частоты и уменьшается частота следования тактовых импульсов на его выходе, следовательно, время задержки сигнум-сигнаов y,(t)sign x,(t) в регистре 9 сдвига .увеличивается, что ведет к уменьшению рассогласования.

Как только рассогласование уменьшится до такой величины, что сигналы с выхода формирователя 17 будут совпадать с сигналами с выхода схемы 25 объединения, на выходе схемы 16 совпадения появятся сигналы (уровень логической 1) В триггер 18 записываются сигналы с выхода схемы 16 совпадения (уровень логической 1). Выходным сигналом триггера 18 (уровень логической 1) отпирается схема 14 совпадения, на вход сложения реверсивного счетчика 19 начинают поступать сигналы и измеритель скорости начинает отслеживать скорость движения объекта. Вькодным сигналом триггера 18 (уровень логической 1) снимается блокировка устройства 24 отсчета, на котором начинает индицироваться измеряемая скорость движения объекта. Если по каким-либо причинам произойдет срыв режима слежения за положением максимума взаимно корреляционной функции входных сигг1алов, то 512 в триггер 18 вновь запишется сигнал с выхода схемы 16 совпадения (уровень логического О) и измеритель скорости перейдет в режим поиска. Сигналы с выхода схемы 15 совпадения вычтутся из содержимого реверсивного счетчика 19. Если не будет вновь найден максимум взаимной корреляционной функции входных сигналов, то как только содержимое реверсивного счетчика 19 станет равным заданному минимальному двоичному числу, сооткетствующему минимальной .частоте следования тактовых импульсов на выходе управляемого делителя 22 частоты, на выходе дешифратора 26 появится сигнал, которым запустится формирователь 20. Выходным сигналом формирователя 20 в каскады реверсивного счетчика 19 вновь запишется максимальное двоичное число, соответствующее максималь ной измеряемой скорости движения объ екта, и процесс поиска максимума взаимной корреляционной функции вход ных сигналов повторится с самого начала , Формула изобретения Корреляционный измеритель скорости, содержащий два приемника, выходы которых соединены с входами соответствующих усихп телей-ограгп чителей, выход первого из которых подключен к информационному входу первого регистра сдвига, выход которого соединен с информационным входом второго регистра сдвига и первыми входами первого и второго триггеров, вторые входы которых поддслючены к выходу второго регистра сдвига, выход перво го триггера соединен с вторьт входом первой схемы совпадения, .первый вход которой подключен к первому входу первой схемы совпаде15ия, а через делитель частоты с постояннылм коэффи4циентом деления - к управл.яемого делителя час/оты, трети; вход первой схем1)1 совпадения сое,.чнен с выходом второго усилителя-ограничителя и с третьим входом второй схемы совпадения, а выход - с суымиру.ющим входом реверсивного счетчика, вычитающий вход которого подключен к выходу второй схемы совпадения., второй вход которой соединен с зиходом второго триггера, вькод второго фop отpoвателя подключен к установочному .входу реверсивного С-.(етчика, гадроинформап,ионные которого соединены с информаг;иоиными входами управляемого делителя частоты, тактовый вход которого лодключек к выхо.ду генератора тактовых импульсов, а выход подключеп к первому .Бходу блока отсчета и к тактовым входам первого и второго регистров сдвига, вход первого формирователя подключен к выходу второго усилителя-ограничителя, а выход подключен к второму входу третьей схемы совпадения и к второму входу третьего триггера, первый вход которого подключен к выходу третьей схемы совпадения, о т л и ч а ю щ и и с я тем, что, с целью уменьшения погрешности и повышения устойчивости работы при больших ускорениях, в него дополнительно введены де11;.нфратор и схема объе.цинения, первый вход которой подключен к выходу первого регистра сдвига, второй вход подключен к выходу второго регистра сдвига, а вьЕсод - к первому входу третьей схемы совпадения, зход.ы деш.ифратора подключены к инфор;-гадионным зьЕ-содам реверсивного счетч)-1ка5 вькод дешифра тор а подключен к входу второго формирователя и вьпсод третьего триггера соединен с че вертым .входом первой схемы совпадения и с jrropbiM вхо- дом блока отсчета.

| ЭПОКСИДНАЯ КОМПОЗИЦИЯ | 2007 |

|

RU2345106C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-07—Публикация

1984-12-29—Подача