Изобретение относится к области автоматики и вычислительной техники, в частности к программному управлению технологическими объектами, алгоритм управления которых описывается с помощью временных булевых функций.

Цель изобретен.. - повышение быстродействия при вычислении булевых функций и сокращение аппаратурных затрат.

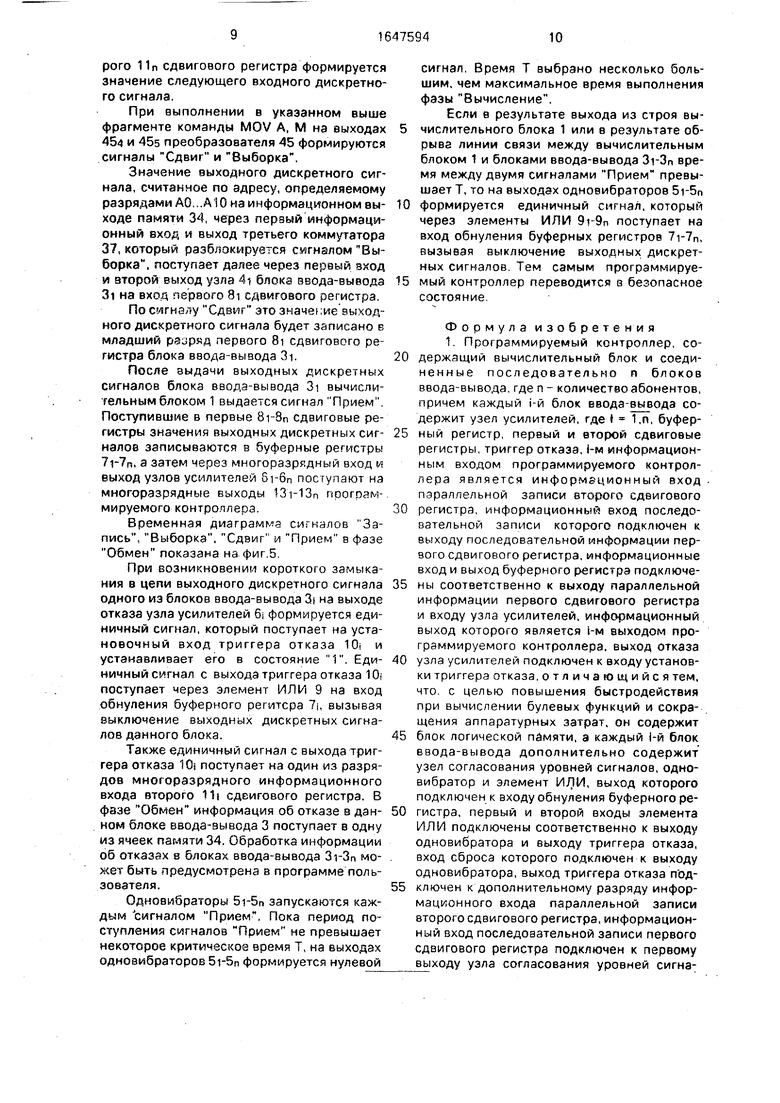

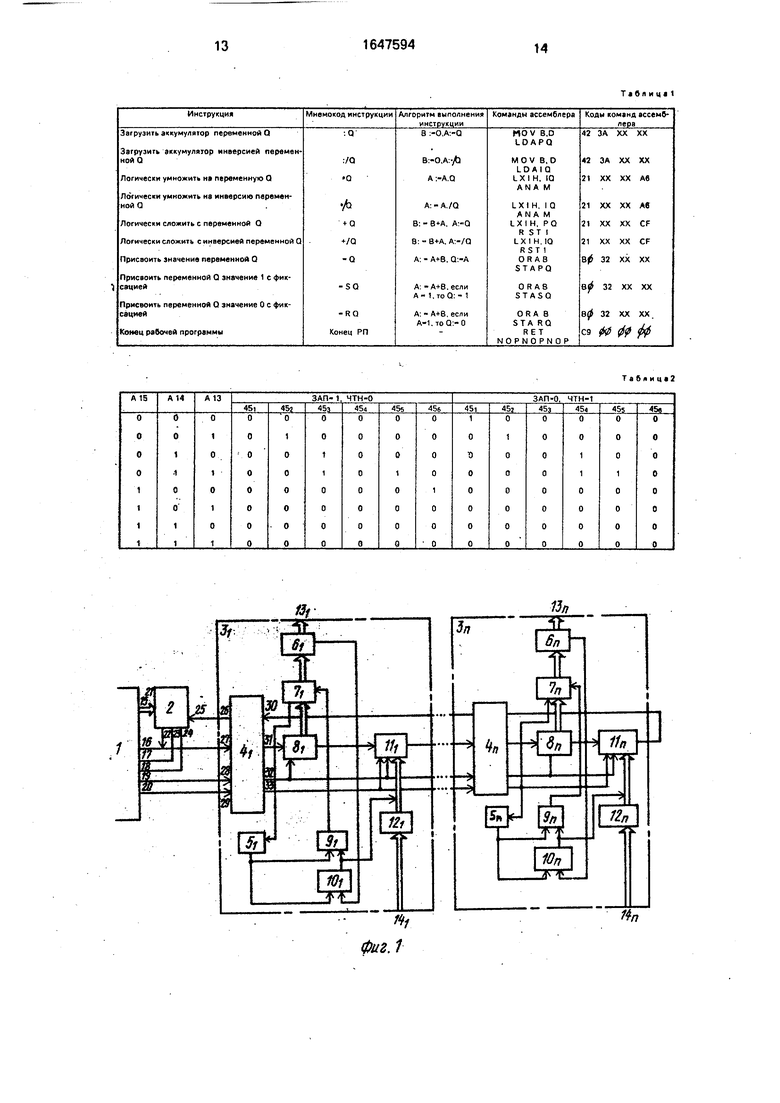

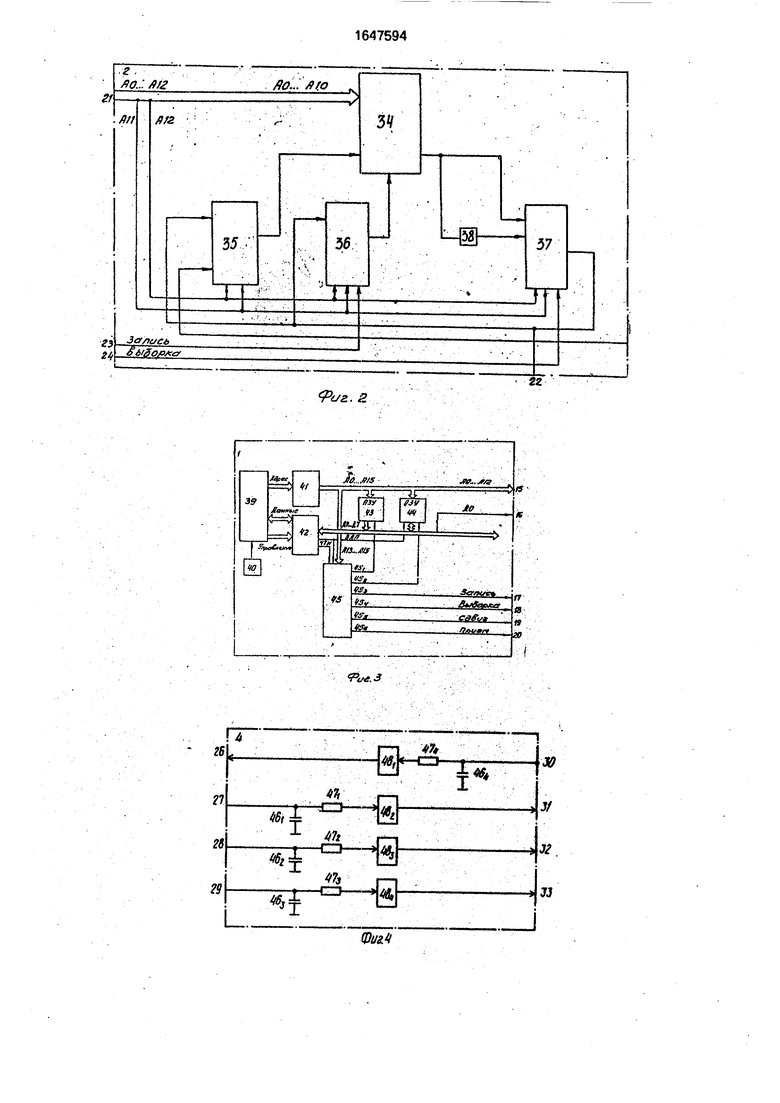

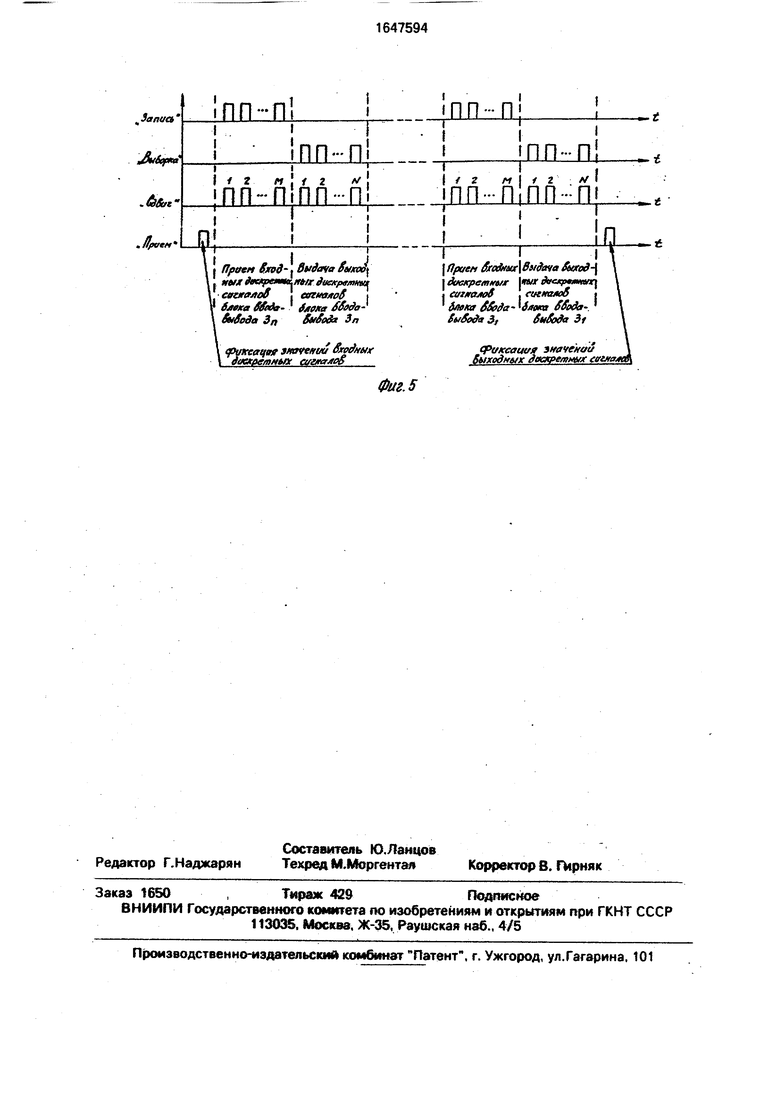

На фиг.1 представлена схема программируемого контроллера; на фиг.2 - схема блока логической памяти; на фиг.З, 4 - примеры выполнения соответственно вычислительного блока и узла согласования уровней сигналов; на фиг.5 - временная диаграмма фазы обмена.

Программируемый контроллер (фиг.1) содержит вычислительный блок 1, блок 2 логической памяти, блоки ввода-вывода 3i-3ri, узлы 4i-4n согласования уровней сигналов, одновибраторы 5i-5n, узлы усилителей 6i-6n, буферные регистры 7i-7n, первые сдвиговые регистры 8i-8n, элементы ИЛИ 9i-9n, триггеры отказа ЮН On, вторые сдвиговые регистры 11Н1п, кодовые преобразователи 12i-12n, выходы 13i-13n и информационные входы 14i-14n.

Вычислительный блок 1 имеет адресный выход 15, информационный вход-выход 16, выходы Запись 17, Выборка 18, Сдвиг 19 и Прием 20.

Блок 2 логической памяти имеет адресный вход 21, информационный вход-выход 22, вход Запись 23, вход Выборка 24 и информационный вход 25.

Каждый узел 4i согласования уровней сигналов ( 1,п) имеет выход 26, входы 27-30 и выходы 31-33.

Блок-логической памяти (фиг.2) содержит оперативную память 34, первый 35, втоО

VJ

СП

ю ь.

рой 36 и третий 37 коммутаторы, элемент НЕ 38.

Вычислительный блок (фиг.З) содержит вычислительный узел 39, генератор 40 тактовых импульсов, шинный формирователь 41, контроллер системной шины 42, постоянную память 43, оперативную память 44, кодовый преобразователь 45.

Узел согласования уровней сигналов (фиг.4) содержит конденсаторы 46i-464, резисторы 471-474 и триггеры Шмидта 48t- 484.

Устройство работает следующим образом.

Программа пользователя на входном языке программирования представляет собой систему уравнений, где аргументами служат входные переменные (входные дискретные сигналы), внутренние переменные, выходные переменные (выходные дискретные сигналы), а функциями - внутренние и выходные переменные.

В процессе трансляции программа пользователя преобразуется в последовательность одноразрядных логических инструкций, затем каждая такая инструкция представляется несколькими машинными командами вычислительного узла 39(мЛсро- процессора).

В качестве вычислительного узла 39 может быть выбран КР580ИК80А. Мнемонические названия машинных команд для определенности в дальнейшем даны на языке Ассемблер указанного микропроцессора.

8 табл. 1 приведены список одноразрядных логических инструкций (в дальнейшем инструкций), их мнемокоды, алгоритм выполнения каждой инструкции, последовательность машинных команд микропроцессора, кодирующих каждую инструкцию, и коды команд ассемблера.

Через XX XX обозначен физический ад- . рее ячейки памяти, где хранится соответствующая переменная.

Вычисление булевых функций производится с использованием 0-го разряда регистров А и В микропроцессора, в его регистре D хранится константа 0.

Через PQ, IQ, SQ, RQ обозначены адре- са блока 2 логической памяти 2, при обращении к которым соответственно выполняются

чтение и запись прямого значения переменной Q;

чтение инверсного значения переменной Q;

присвоение переменной Q значения 1, если значение 0-го разряда регистра А равно 1:

присвоение переменной Q значения О, если значение 0-го разряда регистра А равно 1.

В программе RST1 записана следующая последовательность машинных команд: RST1: ORA В

MOV В,А MOV А.М RET

Например, программа пользователя состоит из двух уравнений: Х1 + /Х2 -X3 Y1 /Х1 X3 + X2 Y2,

где через X и У обозначены некоторые вход- ные и выходные переменные устройства.

Программа кодируется следующей последовательностью машинных команд: CONTR MOV BD Инструкция : Х1

LDA РХ1

LXJH, 1X2Инструкция +/Х2

RST1

LXIH, РХЗИнструкция-ХЗ

ANAM

ORABИнструкция Y1

STA PY1

MOV B.DИнструкция: /Х1

LDA 1X1

LX1H, РХЗ Инструкция-ХЗ ANAM

LXfH. PX2 Инструкция + Х2

RST1 ORABИнструкция SY2

STA SY2

RETКонец рабочей

программы.

Каждый раз при вызове программы CONTR по значениям переменных Х1, Х2, ХЗ будут вычислены значения переменных Y1, Y2.

Программа пользователя хранится в памяти 43; переменные, над которыми выполняются одноразрядные логические инструкции, хранятся в памяти 34; данные, организованные побайтно, например теку- щие значения таймеров и счетчиков, рабочая и стековая области узла 39, хранятся в памяти 44.

Работа узла 39 синхронизируется гене- ратором 40. В каждом цикле чтения или записи с многоразрядного адресного выхода узла 39 через шинный формирователь 41 информация адреса поступает на многоразрядные входы памяти 43, памяти 44, входы преобразователя 45, памяти 34. С м ногораз- рядного управляющего выхода узла 39 информация управления поступает на одноименный вход контроллера системной шины 42, который вырабатывает сигналы

управления Чтение (ЧТН) и Запись (ЗАП). Эти сигналы вместе с информацией адреса поступают на входы преобразователя 45.

В качестве контроллера системной шины может быть выбран КР580ВК28.

На выходах преобразователя 45 формируются сигналы:

45 - выборка памяти 43;

45 - выборка памяти 44;

453-сигнал Запись ;

сигнал Выборка ;

сигнал Сдвиг ;

45е- сигнал Прием.

Функционирование преобразователя 45 описывается таблицей истинности (табл.2).

В дальнейшем под выражением - выдать сигнал Запись, Выборка, Сдвиг, Прием - будем понимать формирование единичного значения такого сигнала с дли- тельностью, определяемой длительностью сигналов управления ЧТН и ЗАП.

Для всех не указанных в табл. 2 комбинаций значений сигналов ЧТН и ЗАП значения выходных сигналов преобразователя 45 определены как О.

Работа программируемого контроллера в целом во времени складывания из двух циклически чередующихся фаз: Вычисление и Обмен.

В фазе Вычисление выполняется программа пользователя, при этом значения входных, выходных и внутренних переменных читаются и записываются в памяти 34.

В фазе Обмен вычисленные значения выходных переменных из памяти 34 передаются на многоразрядные выходы t3t-13n, a значения входных переменных обновляются путем передачи сигналов с многоразрядных входов 141-14п в память 34.

В фазе Вычисление ускорение вычислений одноразрядных логических операций достигается за счет избыточного использования адресного пространства узла 39. Обозначим через Si физический адрес, on- ределяемый разрядами адреса АО...А10, некоторой одноразрядной переменной Q в памяти 34.

При трансляции программы пользователя для такой переменной должны быть выполнены следующие подстановки:

PQ-Sj + 4$0H:

IQ Si + 4800H;

SQ - Si + 4800H;

RQ Sj + 5WH,

Выполнение узлом 39 команды чтения памяти по адресу PQ вызывает следующее:

На выходе 454 преобразователя 45 формируется единичное значение сигнала Выборка.

Сигналом Выборка по третьему управляющему входу разблокируется третий коммутатор 37.

На информационном выходе памяти 34 формируется определяемое разрядами адреса АО...А10 значение переменной Q, которая через первый информационный вход и выход третьего коммутатора 37 и через разряд DO второго и первого многоразрядных входов-выходов контроллера системной шины 42 поступает на информационный выход узла 39.

При выполнении узлом 39 команды чтения памяти по адресу Ю все происходит аналогично чтению по адресу PQ за исключением того, что на выход третьего коммута- тора 37 поступает инвертированное значение переменной Q с выхода элемента НЕ 38.

При выполнении узлом 39 команды записи в память по адресу PQ происходит следующее.

На выходе 45з преобразователя 45 формируется единичное значение сигнала Запись.

Сигналом Запись по третьему управляющему входу разблокируется второй коммутатор 36, и с его выхода единичный сигнал поступает на управляющий вход памяти 34.

Информация разряда DO многоразрядного информационного входа-выхода узла 39 через контроллер системной шины 42 поступает на первый информационный вход первого коммутатора 35, а с его выхода - на информационный вход памяти 34. где записывается по адресу, определяемому разрядами адреса АО...А10.

Выполнение узлом 39 команды записи в память по адресу SQ вызывает следующее.

На выходе 45з преобразователя 45 формируется единичное значение сигнала Запись.

Сигналом Запись по третьему управляющему входу разблокируется второй коммутатор 36, и на его выходе формируется единичный сигнал при условии,что на его первый информационный вход поступает единичная информация разряда DO многоразрядного информационного входа-выхода узла 39 через контроллер системной шины 42.

На информационный вход памяти 34 с выхода первого коммутатора 35 подается единичный сигнал.

Выполнение узлом 39 команды записи в память по адресу RQ происходит аналогично записи по адресу SO. за исключением того, что на информационный вход памяти 34 с выхода первого коммутатора 35 подается нулевой сигнал.

Выходные функции первого 35, второго 36 и третьего 37 коммутаторов описываются соответственно логическими выражениями: Инф.Г- /А11--/А12 +А11- /А12 + . All- A12(1)

Запись (/А11- /А12 + Инф.Г- АИ- /А12+ Инф.Г- /А11- А12 + А11 А12) (2) Выборка (Q/A11 /A12 + /QA11- /А1 + QA11 -А12). :(3)

Через Инф.Г и Инф.2 обозначены сигналы соответственно на первом информационном входе-выходе 22 и на втором информационном входе 25 блока 2 логической памяти; через Q - сигнал на информационном выходе памяти 34; через А11, А12 - сигналы 11-го и 12-го разрядов многоразрядного адресного входа блока 2 логической памяти.

Для определенности предположим, что разрядность многоразрядных выходов одинакова и равна N, а также разрядность многоразрядных входов 14t-14n одинакова и равна М.

Перед началом обмена вычислительный блок 1 выдает сигнал Прием для запоминания значений входных дискретных сигналов во вторых 111-1 tn сдвиговых регистрах.

Для этого узел 39 должен выполнить команду

STA,

При этом на выходе 45 преобразователя 45 формируется сигнал Прием, который

через четвертый вход и четвертый выход узлов 4i-4n поступает на входы параллельной записи вторых 111-11П сдвиговых регистров, вызывая запоминание текущих значений входных дискретных сигналов, поступающих с многоразрядных входов 14i-14n через преобразователи 12i- 12П на их многоразрядные входы.

В дальнейшем чередуются прием входных дискретных сигналов и выдача выходных дискретных сигналов для блоков ввода-вывода Зп, 3n-i...3i.

Чтение и запись информации о входных и выходных сигналах в память 34 осуществляется при выполнении узлом 39 команд

чтения и записи в память с базовым адресом 58/УЙ, который загружается в регистры H,L узла 39. и смещением Si, определяющим физический адрес переменной памяти 34.

Фрагмент программы обмена, обслуживающий один блок ввода-вывода 3i, приведен ниже;

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к программному управлению технологическим оборудованием, и может быть использовано в программируемых системах управления технологическими объектами, алгоритм управления которых описывается с помощью булевых функций. Цель изобретения - повышение быстродействия при вычислении булевых функций и сокращение аппаратурных затрат. Программируемый контроллер содержит вычислительный блок и соединенные последовательно блоки ввода-вывода. Для достижения цели в контроллер введен блок логической памяти, а каждый блок ввода-вывода дополнительно содержит узел согласования уровней сигналов, одно- вибратор и элемент ИЛИ. Блок логической памяти содержит первый, второй и третий коммутаторы, элемент НЕ. оперативную память. 2 з.п. ф-лы, 5 ил., 2 табл.

Повторить /М О V М, А Ъ

М раз

./NX H

MOVM.A /NXH

вторить раз

М О V М, А

/NX H АЛ О V А, М L/NX И

М О V А, М

/NXH

/

М О V А, М /NXH

При выполнении в таком фрагменте команды MOVM, А на выходах 45з и 45s преобразователя 45 формируются сигналы Сдвиг и Запись.

Значение входного дискретного сигнала с выхода последовательной информации второго 11п сдвигового регистра последнего блока ввода-вывода Зп поступает через со- ответствующие выход узлов 4i-4n и через второй информационный вход первого коммутатора 35 на информационный вход

М-я входная переменная

(М-1)-я входная переменная

1-я входная переменная N-я входная переменная

(М-1)-я выходная переменная

в

V

1-я выходная переменная

памяти 34. По сигналу запись происходит запоминание этой информации по адресу, определяемому разрядами АО...А10 многоразрядного адресного входа блока 2 логической памяти.

Сигнал Сдвиг через соответствующие выходы узлов 4i-4n поступает на тактовые входы первых 8i-8n и вторых 11И1П сдвиговых регистров, вызывая последовательный сдвиг информации. Тем самым на выходе последовательной информации втоporo 11n сдвигового регистра формируется значение следующего входного дискретного сигнала.

При выполнении в указанном выше фрагменте команды MOV A, M на выходах 454 и 45s преобразователя 45 формируются сигналы Сдвиг и Выборка.

Значение выходного дискретного сигнала, считанное по адресу, определяемому разрядами АО...А10 на информационном выходе памяти 34, через первый информационный вход и выход третьего коммутатора 37, который разблокируется сигналом Выборка, поступает далее через первый эход и второй выход узла 4i блока ввода-вывода 3i на вход первого 3i сдвигового регистра.

По сигналу Сдвиг это значение выходного дискретного сигнала будет записано в младший разряд первого 8i сдвигового регистра блока ввода-вывода 3i.

После выдачи выходных дискретных сигналов блока ввода-вывода 3i вычислительным блоком 1 выдается сигнал Прием. Поступившие в первые 8i-8n сдвиговые регистры значения выходных дискретных сигналов записываются в буферные регистры 7i-7n, а затем через многоразрядный вход и выход узлов усилителей 6i-6n поступают на многоразрядные выходы I3i-13n поограм- мируемого контроплера.

Временная диаграмма сигналов Запись. Выборка, Сдвиг и Прием в фазе Обмен показана на фиг.5.

При возникновении короткого замыкания в цепи выходного дискретного сигнала одного из блоков ввода-вывода 3t на выходе отказа узла усилителей 6i формируется единичный сигнал, который поступает на установочный вход триггера отказа Щ и устанавливает его в состояние 1. Единичный сигнал с выхода триггера отказа 10i поступает через элемент ИЛИ 9 на вход обнуления буферного регитсра 7i, вызывая выключение выходных дискретных сигналов данного блока.

Также единичный сигнал с выхода триггера отказа 10) поступает на один из разрядов многоразрядного информационного входа второго 111 сдвигового регистра. В фазе Обмен информация об отказе в данном блоке ввода-вывода 3 поступает в одну из ячеек памяти 34. Обработка информации об отказах в блоках ввода-вывода Зч-3п может быть предусмотрена в программе пользователя.

Одновибраторы 5i-5n запускаются каждым сигналом Прием. Пока период поступления сигналов Прием не превышает некоторое критическое время Т, на выходах одновибраторов 5i-5n формируется нулевой

сигнал. Время Т выбрано несколько большим, чем максимальное время выполнения фазы Вычисление.

Если в результате выхода из строя вычислительного блока 1 или в результате обрыва линии связи между вычислительным блоком 1 и блоками ввода-вывода 3i-3n время между двумя сигналами Прием превышает Т, то на выходах одновибраторов 5i-5n

формируется единичный сигнал, который через элементы ИЛИ 9i-9n поступает на вход обнуления буферных регистров 7i-7n, вызывая выключение выходных дискретных сигналов. Тем самым программируемый контроллер переводится в безопасное состояние

Формула изобретения

регистра, информационный вход последовательной записи которого подключен к выходу последовательной информации первого сдвигового регистра, информационные вход и выход буферного регистра подключены соответственно к выходу параллельной информации первого сдвигового регистра и входу узла усилителей, информационный выход которого является t-м выходом программируемого контроллера, выход отказа

узла усилителей подключен к входу установки триггера отказа, отличающийся тем, что с целью повышения быстродействия при вычислении булевых функций и сокращения аппаратурных затрат, он содержит

блок логической памяти, а каждый 1-й блок ввода-вывода дополнительно содержит узел согласования уровней сигналов, одно- вибратор и элемент ИЛИ, выход которого подключен к входу обнуления буферного регистра, первый и второй входы элемента ИЛИ подключены соответственно к выходу одновибратора и выходу триггера отказа, вход сброса которого подключен к выходу одновибратора, выход триггера отказа подключей к дополнительному разряду информационного входа параллельной записи второго сдвигового регистра, информационный вход последовательной записи первого сдвигового регистра подключен к первому выходу узла согласования уровней сигналов, тактовые входы первого и второго сдвиговых регистров подключены к второму выходу узла согласования уровней сигналов, вход записи буферного регистра, вход одно- вибратора и вход параллельной записи второго сдвигового регистра подключены к третьему выходу узла согласования уровней сигналов, адресный вход, входы сигналов Запись и Выборка блока логической памяти подключены к одноименным выходам вычислительного блока, информационный вход-выход вычислительного блока подключен к информационному входу-выходу блока логической памяти и к первому входу узла согласования уровней сигналов первого блока ввода-вывода, четвертый выход узла согласования уровней сигналов которого подключен к информационному входу блока логической памяти, выходы сигналов Сдвиг м Прием вычислительного блока подключены ко второму и третьему входам узла согласования уровней сигналов первого блока ввода-вывода, второй и третий входы узла согласования уровней сигналов (l+t)-ro блока ввода-вывода подключены соответственно к второму и третьему выходам узла согласования уровней сигналов i-ro блока ввода-вывода, четвертый выход и первый вход узла согласования уровней сигналов (f-H)ro блока ввода-вывода подключены соответственно к четвертому входу узла согласования уровней сигналов и к выходу последовательной информации второго сдвигового регистра 1-го блока ввода-вывода, выход последовательной информации второго сдвигового регистра n-го ввода-вывода подключен к четвертому входу узла согласования уровней сигналов п-го блока ввода-вывода.

информационному входу-выходу блока логической памяти, информационный вход которого подключен ко второму информационному входу первого коммутатора, первый

и второй управляющие входы первого, второго и третьего коммутаторов подключены к старшим разрядам адресного входа блока логической памяти, входы сигналов Запись и Выборка которого подключены соответственно к третьим управляющим входам второго и третьего коммутаторов, вход и выход элемента НЕ подключены соответственно к информационному выходу оперативной памяти и ко второму информационному входу третьего коммутатора.

шинный формирователь, постоянную и оперативную память и кодовый преобразователь, причем адресный выход вычислительного узла соединен с информационным входом шинного формирователя,

выход которого соединен с адресными входами постоянной и оперативной памяти, с первым входом кодового преобразователя и является адресным выходом блока, информационный вход-выход которого подключен

через шину данных к информационному входу-выходу контроллера системной шины, выходу постоянной памяти и информационному входу-выходу оперативной памяти, информационный вход-выход вычислительного узла соединен с информаци- онным входом-выходом контроллера системной шины, выход Запись которого соединен с входом Запись оперативной памяти и вторым входом кодового преобразователя, третий вход которого соединен с выходом Чтение контроллера системной шины, управляющие выходы вычислительного узла соединены с соответствующими управляющими входами контроллера системной шины, выход генератора тактовых импульсов соединен с тактовым входом вычислительного узла, первый и второй выходы кодового преобразователя соединены соответственно с входом Выборка постоянной памяти и входом Выборка оперативной памяти, с третьего по шестой выходы кодового преобразователя являются соответственно выходами Запись, Выборка, Сдвиг и Прием блока.

Таблица

Таблица

s Ј

s

«rvSJ- «VI «si

fe S fe $

y

5J

I

I

Праен Sxvd-, Выдача fwa иыя toape M.Hb/r juaepeamt emuaaol i блвка Меда- faejra SMo- SttSoda 3n 3n

tpuKcaqat значении Oxt , JaetfleaiMMe сигхалоЈ

/ &кн)ны

flpaen 6nxtraff 8 t fafa &atod-

&ккрею ыг « МгЛс « и«иг|

сагкаюб . cuttnuco

блека Јfefa 6аека ббеда(ыбода 3tSttfoda 3t

Факсам эюченои Быходкык дискретных fff

| Патент США № 4258563, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| СПОСОБ ПУСКА САМОВОЗБУЖДАЮЩЕГОСЯ ПАРАЛЛЕЛЬНОГОИНВЕРТОРА | 0 |

|

SU166402A1 |

| Насос | 1917 |

|

SU13A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1991-05-07—Публикация

1989-04-06—Подача