(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ ЗАДАННОГО ПОРЯДКА

| название | год | авторы | номер документа |

|---|---|---|---|

| Передающая телевизионная камера на фоточувствительном приборе с зарядовой связью | 1987 |

|

SU1467791A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| Устройство контроля технического состояния механических объектов по вибрационным нагрузкам | 1989 |

|

SU1703991A2 |

| Способ контроля положения объекта относительно опорного луча и устройство для его осуществления | 1987 |

|

SU1674368A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Передающая телевизионная камера на фоточувствительном приборе с зарядовой связью | 1985 |

|

SU1284002A1 |

| Измерительный комплекс | 1988 |

|

SU1582156A1 |

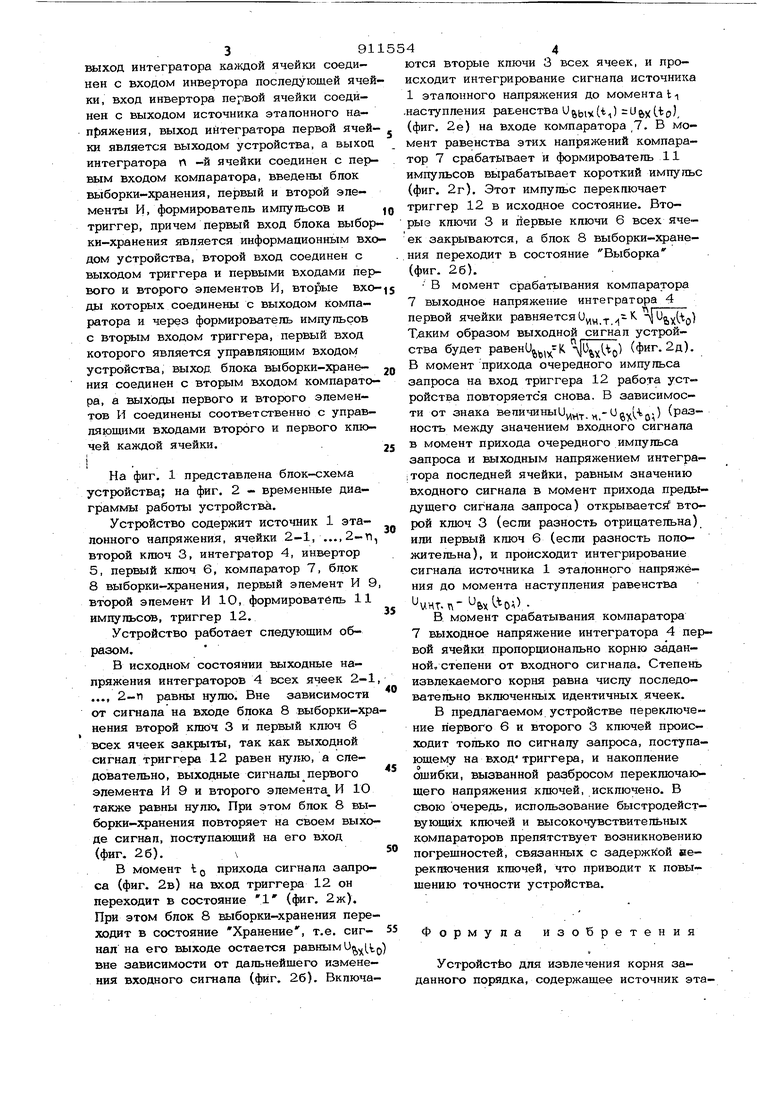

Изобретение относится к автоматике и вычислительной технике и может найти применение в аналоговых вычислительных машинах. Известно устройство для извлечения корня, содержащее управляемые интеграторы, ключи, фишэтр, одновибратор, блок формирования импульсов и блоки обнуления интеграторов tl. Недостатком указанного устройства , является большая инерционность, обуслов ленная наличием фильтра, выходной сиг нал которого является выходным сигналом всего устройства. Наиболее близким к предлагаемому яв ляется устройство для извлечения корня заданного порядка, содержащее последова тельно соединенные источник эталонного напряжения и п ячеек, каждая из которых содержит последовательно соединен- ные основной ключ и интегратор, ко входу основного ключа подключен вход инвер тора, выход которого через дополнительный ключ подключен к входу интегратора интегратора каждой ячейки соединен со входом инвертора последующей ячейки, Ы.1ХОД интегратора последней ячейки подключен к одному из входов компаратора, другой вход которого соединен с входом всего устройства, а выход компараторй подключен к управляющим входам основного и дополнительного ключей всех ячеек 2. Недостатком известного устройства является накопление погрюшностей в процессе работы, вызванное задержкой срабатывания ключей и компаратора. Цель изобретения - повышение точности работы устройства. Поставленная цель достигается тем, что в устройство для извлечения корня заданного порядка, содержащее источник эталонного напряжения и п ячеек, каждая из которых содержит последовательно соединенные инвертор и первый ключ, выход которого соединен с входом интегь. ратора и выходом второго ключа, вход которого соединен с входом инвертора, КЫХ.ОР. интегратора каждой ячейки соединен с входом инвертора последующей яче ки, вход инвертора первой ячейки соединен с выходом источника эталонного напряжения, выход интегратора первой ячей ки является выходом устройства, а выхо интегратора Л -и ячейки соединен с пер вым Входом компаратора, введены блок выборки-хранения, первый и второй элементы И, формирователь импульсов и триггер, причем первый вход блока выбо ки-хранения является информационным вх дом устройства, второй вход соединен с выходом триггера и первыми входами пер вого и второго элементов И, вторые BXO ды которых соединены с выходом компаратора и через формирователь импупьсов с вторым входом триггера, первый вход которого является управляющим входом устройства, выхад блока выборки-хранения соединен с вторым входом компарато ра, а выходы первого и второго элементов И соединены соответственно с управляющими входами второго и первого ключей каждой ячейки. . I. На фиг. 1 представлена блок-схема устройства,; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит источник 1 эталонного напряжения, ячейки 2-1, ...,2-п второй ключ 3, интегратор 4, инвертор 5, первый ключ 6, компаратор 7, блок 8 выборки-хранения, первый элемент И 9 второй элемент И 10, формирователь 11 импульсов, триггер 12. Устройство работает следующим образом. В исходном состоянии выходные напряжения интеграторов 4 всех ячеек 2-1 .... 2-п равны нулю. Вне зависимости от сигнала на входе блока 8 выборки-хра нения второй ключ 3 и первый ключ 6 всех ячеек закрыты, так как выходной сигнал триггера 12 равен нулю, а следовательно, выходные сигналы первого элемента И 9 и второго элементами 10 также равны нулю. При этом блок 8 выборки-хранения повторяет на своем выходе сигнал. Поступающий на его вход (фиг. 26).V В момент IQ прихода сигнала запроса (фиг. 2в) на вход триггера 12 он переходит в состояние (фиг. 2ж). При этом блок 8 выборки-хранения переходат в состояние Хранение, т.е. сигнал на его выходе остается равным вне зависимости от дальнейшего изменения входного сигнала (фиг. 26). Включаются вторые ключи 3 всех ячеек, и происходит интегрирование сигнала источника 1 эталонного напряжения до момента t .наступления равенства (tJ ) (фиг. 2е) на входе компаратора 7. В момент равенства этих напряжений компаратор 7 срабатывает и формирователь 11 импульсов вырабатывает короткий импульс (фиг. 2г). Этот импульс переключает триггер 12 в исходное состояние. Вторые ключи 3 и йервые ключи 6 всех ячеек закрываются, а блок 8 выборки-хранения переходит в состояние Выборка (фиг. 26).. В момент срабатывания компаратора 7выходное напряжение интегратора 4 первой ячейки равняется(} г - Таким образом выходной сигнал устройства будет равени К ) (фиг. 2д). 8момент прихода очередного импульса запроса на вход триггера 12 работа устройства повторяется снова. В зависимости от знака вeличиныU.-UaJi,,.) (разность между значением входного сигнала в момент прихода очередного импульса запроса и выходным напряжением интегра- TOpa последней ячейки, равным значению входного сигнала в момент прихода предыдущего сигнала запроса) открывается второй ключ 3 (если разность отрицательна), или первый ключ 6 (если разность положительна), и происходит интегрирование сигнала источника 1 эталонного напряжения до момента наступления равенства инт... В момент срабатывания компаратора 7 выходное напряжение интегратора 4 первой ячейки пропорционально корню заданной, степени от входного сигнала. Степень извлекаемого корня равна числу последовательно включенных идентичных ячеек. В предлагаемом устройстве переключение первого б и второго 3 ключей происходит только по сигналу запроса, поступающему на вход триггера, и накопление ощибки, вызванной разбросом перекгаочаюшего напряжения ключей, исключено. В свою очередь, использование быстродействующих ключей и высокочувствительных компараторюв препятствует возникновению погрешностей, связанных с задержкой аереключения ключей, что приводит к повышению точности устройства. Формула изобретения Устройство для извлечения корня заданного порядка, содержащее источник эта-

ионного напряжения и п ячеек, каждая. из которых содержит поспедовате 1ьно сое диненные инвертор и первый кпюч, выход которого соединен с входом интегратора и выходом вторюго кшоча, вход которого соединен с входом инвертора, выход интегратора каждой ячейки соединён с входом инвертора поспедуюшей ячейки, вход инвертора первой ячейки соединен с источником эталонного напряжения, выход интегратора первой ячейки является выходом устройства, а выход интегратора п- ячейки соединен с первым входом компаратора, отличающееся тем, что, с цепью повышейия точности работы устройства, в него введены блок выборкихранения, первый и второй элементы И, формирователь импульсов и триггер, причем первый вход блока выборки-хранения является информационным входом устройства, второй вход соединен с выходом триггера и первыми входами первого и второго элементов И, вторые входы кото1Я 1Х соединены с выходом компаратора и через формирователь импульсов с вторым входе триггера, первый вход которого ,явлйется управляющим входом устройства клход блока выб фки-храиения соединен с вто1яым входом компаратора, а выходы первого и второго элементов И соединены срответственно с управляющими вхо i дами второго и первого юпочей каждой ячейки.

Источвяки иифорлапви, принятые во внимание при зкспертид 1 Авторское свидетельство СССР № 729596. кя. Q 06 Q 7/20, 198О.

N

fy/f,xp.

0ff2,Z

Авторы

Даты

1982-03-07—Публикация

1980-08-04—Подача