(S) ШТЕРПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Узел резистивной сеточной модели | 1982 |

|

SU1070558A1 |

| УНИВЕРСАЛЬНЫЙ ГИБРИДНЫЙ ФУНКЦИОНАЛЬНЫЙПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU419919A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для задания граничных условий | 1984 |

|

SU1193695A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1229780A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Устройство для задания граничных условий | 1981 |

|

SU991447A1 |

| Линейный интерполятор | 1974 |

|

SU506873A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности в аналоговых и аналого-цифровых вычислительных, и управляющих устройствах и системах. Известен интерполятор, содержащий блок нелинейной интерполяции, коммутатор и фильтр низкой частоты Dl« Недостатком известного интерполя- тора является сложность технической реализации при высоких требованиях к точностивосстановления промежуточных значений сигнала. Известен также интерполятор, содер жащий суммирующие усилители, кодоуправляемые резисторы, регистр кода аргумента и преобразователи кодов (23. Недостатком известного интерполятора также является.сложность технической реализации Наиболее близким к предлагаемому является интерполятор, содержащий код управляемые проводимости и рперационные усилители, выход первого из которых является выходоминтерполятора, а вход второго операционного усилителя соединен с выходом первой кодоуправляемой проводимости,подключенной управляющими входами к выходам регистра кода аргумента и к управляющим входам второй и третьей кодоуправляемых проводимостей, причем третий операционный усилитель соединен выходом с сигнальным входом вторюй кодоуправляемой проводимости, а входом с выходом четвертой кодоуправляеиой проводимости, сигнальный вход которой подключен к шине ввода начального узлового значения второй производной, а сигнальные входы первой и третьей кодоуправляемых проводимостей соединен соответственно с шинами ввода начальных узловых значений третьей и первой производных, причем выход второго оп рационного усилителя подключен к сит нальному входу пятой кодоуправляемой проводимости, соединенной выходом че391

рез четвертый операционный усилитель с сигнальным входом шестой кодоуправляемой проводимости, а выходы второй третьей и шестой кодоуправляемых прово/ имостей и шина ввода начального узлового значения функции подключены к входам первого операционного усилителя, причем управляющие входы четвертой, пятой и шестой кодоуправляемых проводимостей соединены с выходами регистра кода аргумента 3.

Недостатком известного устройства является пониженная точность интерполяции, обусловленная накоплением ошибки к концу аппроксимируемого участка функции.

Цель изобретения - повышение точности интерполяции.

Указанная цель достигается тем, что в интерполятор, содержащий кодоуправляемые проводимости и операционные усилители, выход первого из которых является выходом интерполятора, а вход второго операционного усилителя соединен с выходом первой кодоуправляемой проводимости, подключенной управляющими входами к выходам регистра кода аргумента и к управляющим входам второй и третьей кодЬуправляемых проводимостей, причем третий операционный усилитель соединен выходом с сигнальным входом второй кодоуправляемой проводимости а входом с выходом четвертой кодоуп равляемой проводимости, сигнальный вход которой подключен к шине ввода начального узлового значения второй производной, дополнительно введены эталонные резисторы и блок инвертирования, соединенный входами с выходами регистра кода аргумента, а выходами с управляющими входами чет, вертой, пятой и шестой кодоуправляемых проводимостей, причем шина ввода конечного узлового знамения второй производной подключена к си|;нальному входу третьей кодоуправляемой проводимости и через первый эталонный резистор к входу третьего операционного усилителя, соединенного входом с выходом третьей кодоуправляемой проводимости и через второй эталонный pfesi CTOp с шиной ввода начального узлового значения второй производной, а выход второй кодоуправляемой проводимости подключен к сигнальному входу пятой кодоуправляемой проводимости, соединенной выходом с входом

5614

первого операционного усилителя, вход которого через третий эталонный резистор подключен к выходу второго операционного усилителя, соединенного входом с выходом шестой кодоуправля-емо.й проводимости, причем сигнальные входы первой и шестой кодоуправляемых проводимостей подключены соответственно к шинам ввода конечного fQ и начального узловых значений функции.

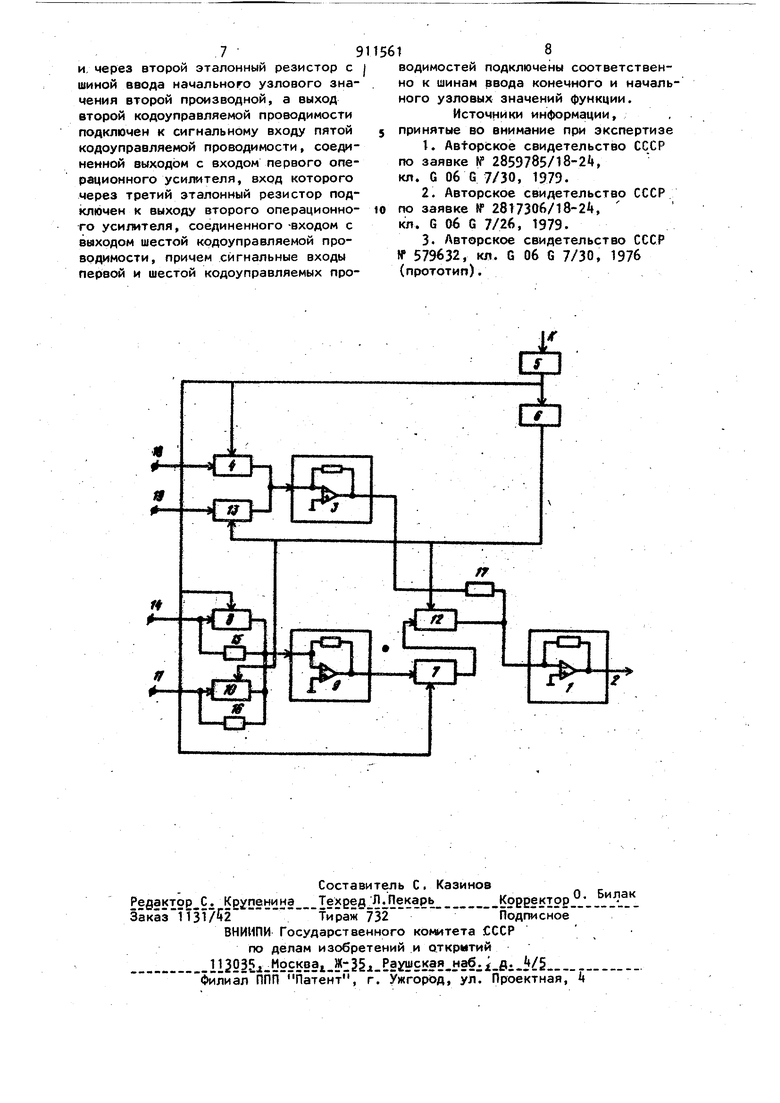

На чертеже изображена блок-схема и нтерполятора.

Устройство содержит первый операционный усилитель 1, вход которого является выходом 2 интерполятора, второй операционный усилитель 3 соединенный входом с выходом первой кодоуправляемой проводимости 4. Проводимость k подключена управляющими входами к выходам регистра 5 кода аргумента, входам блока 6 инвертирования и к управляющим входам второй и третьей кодоуправляемых проводимостей 7 и 8. Третий; операционный усилитель 9 соединен выходом с сигнальным входом проводимости 7, а вхЬдрм - с выходом четвертой кодоупра вляемой проводимости 10, сигнальный вход которой подключен к шине 11 ввода начального узлового значения второй производной f(о). Блок 6 инвертирования соединен выходами с управляющими входами четвертой, пятой и шестой коДоутправляемых проводимостей 10, 12 и 13. Шина Н ввода конечного узлового значения второй производной f(h) подключена к сигнальному Bxof проводимости 8 и через первый эталонный резистор 15 к входу усилителя 9. Усилитель 9 соединен входом с выходом проводимости 8 и через второй эталонный резистор 16 к шине 11. Выход проводимости 7 подключен к сигн льному входупятой проводимости 12, соединенной выходом с входом усилителя 1. Вход усилителя 1 через третий эталонный резистор 17 подключен к выходу усилителя 3. Усилитель 3 соединен -входом с выходом проводимости k. Сигнальные входы проводимостеЛ и 13 подключены соответственно к шинам 18 и 19 ввода конечного и начального узловых значений функции f(h) и f(0).

Работа интерполятора-основана на формировании на каждом из аппроксимирующих участков О,Ь интерполяцион ного полинома третьей степени вида :., , 0))).X WVHO. ,tW-J (j1i xploRaVt.x)4 444Vi x) , где X e CO.h аргумент функции; h(x.,,-xO длина участка аппрок симации; конечное и начальное узловые значения аргумента. При работе интерполятора вес младшего разряда каждой кодоуправляемой проводимости принят равным д. Тогда значения проводимостей G пропорциональны кодам, поступающим на их управляющие входы. Если емкость регист ра 5 кода аргумента равна V, то k + k V - 1, где k - прямой код регистра 5; k - инвертированный обратный код. . Для получения k служит, блок 6 инвертирования. Поэтому -принимают С gjjtV-l). Так как проводимость С постоянная, то для моделирования пр 1водимостей , Gg и йспользу ют постоянные резисторы в цепях обратной связи усилителей 1, 3 и 9 и эталонный резистор 17. Для моделирю вания величин (2h-x) и (h+x) параллельно проводимостям 10 и 8 подключены эталонные резисторы 16 и 15 с проводимостью С. Так как проводимости 8 и 10 соответственно равны GQ gpk gpx GIO Jflk go(h-x), TO с учетом резисторов 15 и 16 формируютсяfi& go(h+x) GIO+C g(p(2h-x). ,При работе интерполятора код промежуточных значений аргумента х вво дится в регистор 5, 3 начальные и конечные узловые значения функции f(0) и f(h) и второй производной f(0) и f(h) подаются в аналоговой форме соответственно на шины 19, 18 12 и It. При работе интерполятора, в случаях X О и х h на выходе 2 интерполятора будут присутствовать напряжения, соответствующие f(0) и f(h) с минимальной ошибкой, так как в это время к выходу 2 будут подклю чены только два усилителя 1 и 3 с коэффициентами передачи, равными ед нице. Максимальная ошибка появляетс внутри каждого отрезка о,Н и оп91 ределяется неточностью задания величин ), f(h), f(o) и f(h) и аргумента X (в зависимости от шага квантования), однако величина этой ошибки существенно меньше ошибки интерполирования в известном устройстве, так как в рассмотренном интерполятс/ре ошибка не накапливается по длине участка интерполирования. Кроме этого, предлагаемый интерполятор содержит на один усилитель меньше, что приводит к уменьшению инструментальной ошибки от смещения нулей усилителей. Таким образом, технико-экономи- . ческий эффект, достигаемый при использовании предлагаемого интерполятора, заключается в повышении точности интерполяции полиноминальных функций при достаточной npocToie реализации интерполятора. Формула изобретения Интерполятор, содержащий кодоуправляемые проводимости и операционные усилители, выход первого из которых является выходом интерполятор, а вход второго операционно о усили-. теля соединен с выходом первой кодоуправляемой проводимости, подключен-ной управляющими входами к выходам регистра кода аргумента и к управляющим входам второй и третьей кодоуправляемых проводимостей, причем третий операционный усилитель соединен выходом с сигнальным входом второй кодоуправляемой лроводимости, а входом с выходом четвертой кодоуправляемой проводимости, сигнальный вход которой подключен к шине ввода начального узлового значения второй производной, отличающийся тем, что, с целью повышения точности интерполяции, в него введены эталонные резисторы и блок инвертирования, соединенный входами с выходами регистра кода аргумента, а выходами с управляющими входами четвертой, пятой и шестой кодоуправляемых проводимостей, причем шина ввода конечного узлового значения второй производной Подключена к сигнальному входу треть,ей кодоуправляемой проводимости и через первый эталонный резистор к входу третьего операционного усилителя, соединенного входом с выходом третьей кодоуправляемой проводимости

.79

и, через второй эталонный резистор с шиной ввода начального узлового значения второй производной, а выход второй кодоуправляемой проводимости подключен к сигнальному входу пятой кодоуправляемой проводимости, соединенной выходом с входом первого операционного усилителя, вход которого через третий эталонный резистор подключен к выходу второго операционного усилителя, соединенного -входом с выходом шестой кодоуправляемой проводимости, причем сигнальные входы первой и шестой кодоуправляемых про18

водимостей подключены соответственно к шинам ввода конечного и начального узловых значений функции. Источники информации,

принятые во внимание при экспертизе

кл. G Об G 7/26, 1979.

Авторы

Даты

1982-03-07—Публикация

1980-08-21—Подача