Изобретение относится к автомати- ке и вычислительной технике и может найти применение для вычисления В-сплайнов вида

ь +

.S, (t) ajt

с- t + (1)

d.

где а,

j

- коэффициенты

сплайна;

t - нормированное значение аргумента (времени), , п - число подынтервалов представления функции,

по значениям интерполирующих коэффициентов у , заданных в виде кодов в узлах равномерной сетки 0,1,2,...,п, п+1 и связанных с узловыми значениями ординат f воспроизводимой функци соотношением вида

f: 7 (у, + 4у,

6 0-,

..)

(2)

Цель изобретения - упрощение устройства за счет сокращения объема памяти.

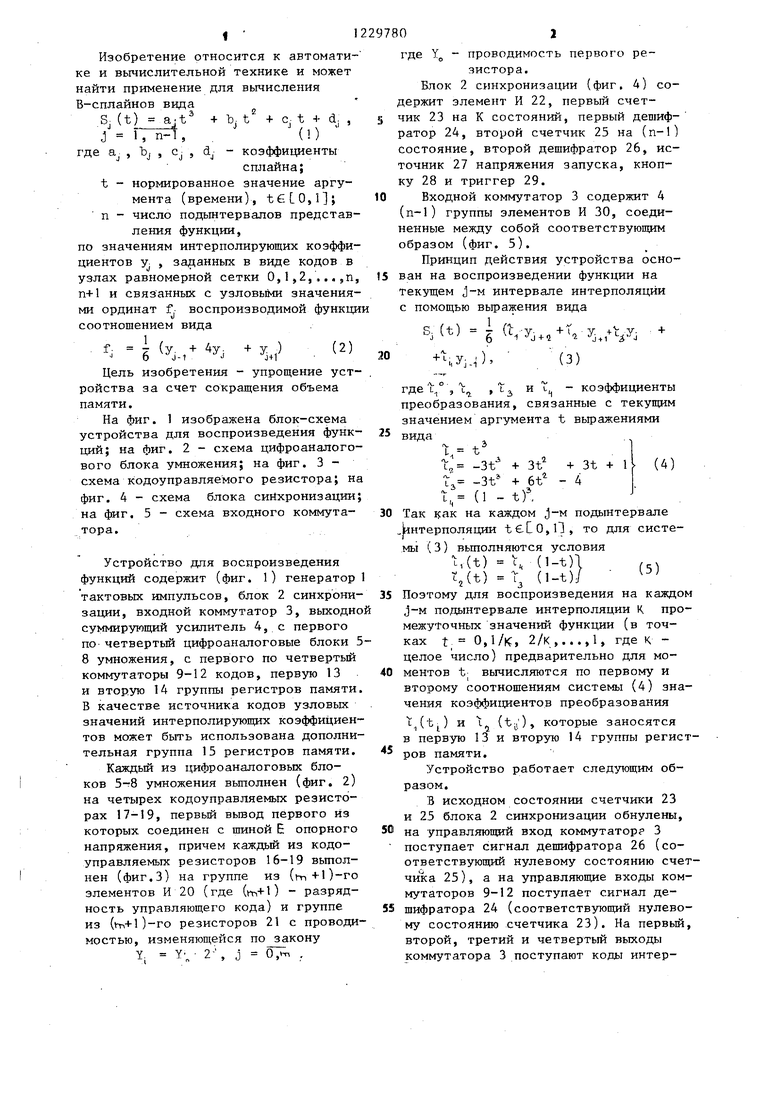

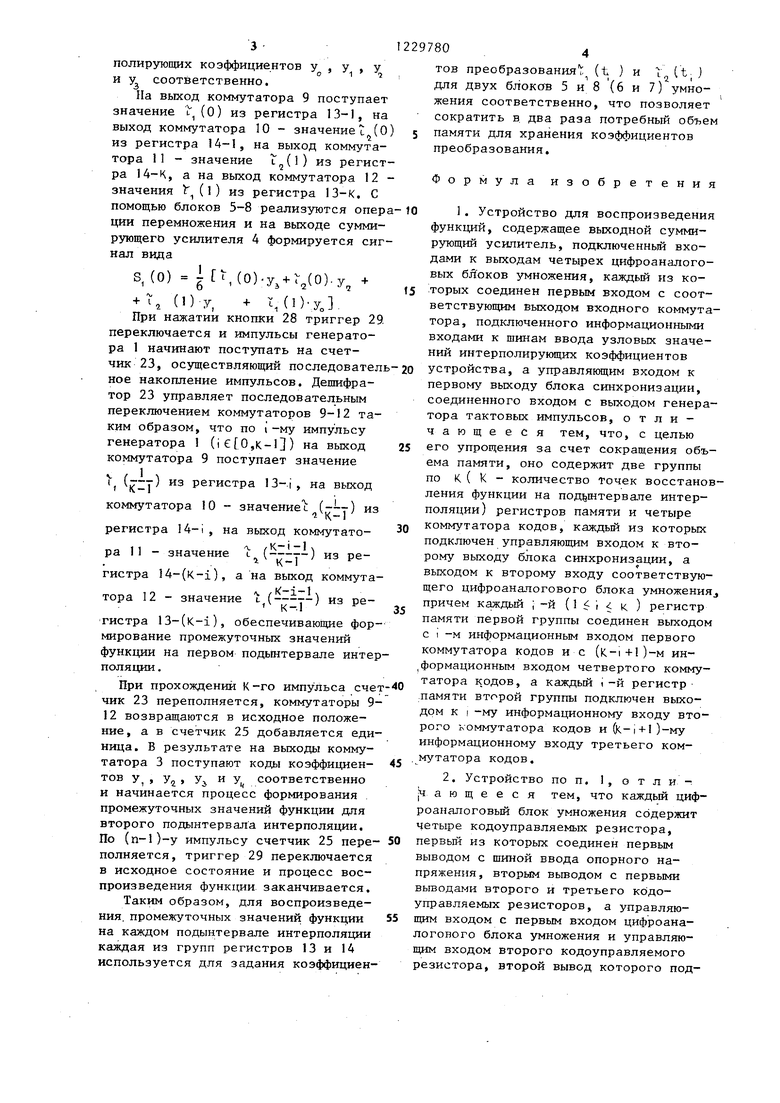

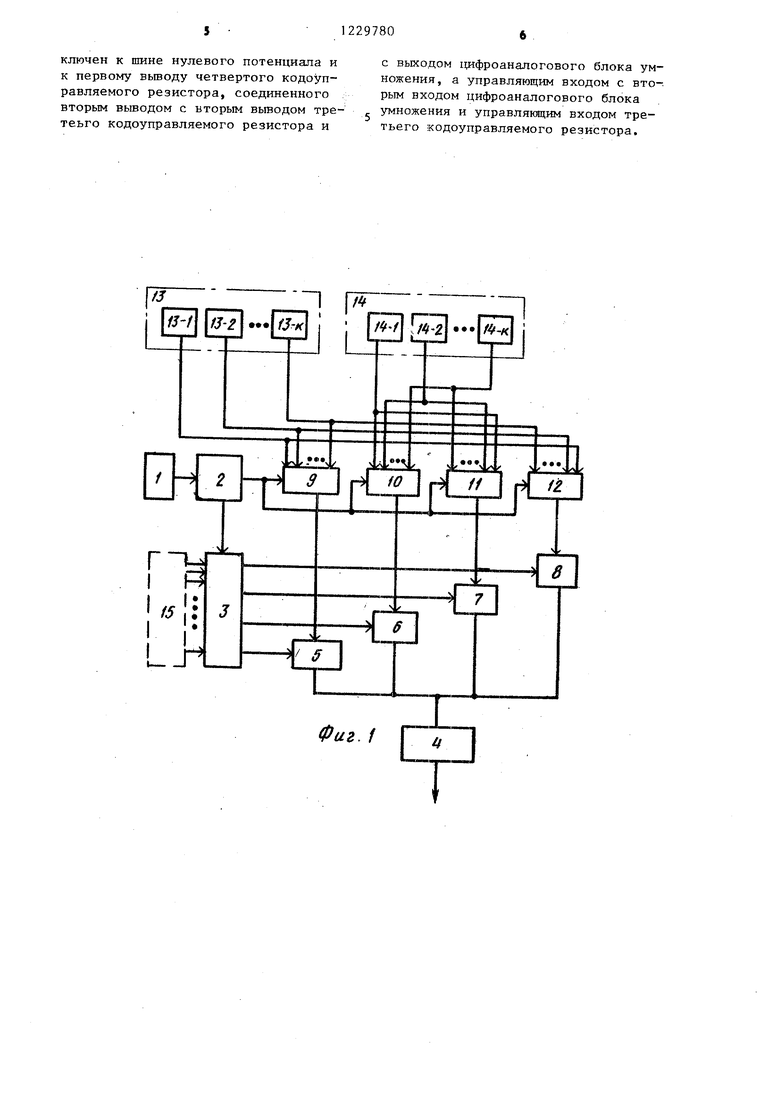

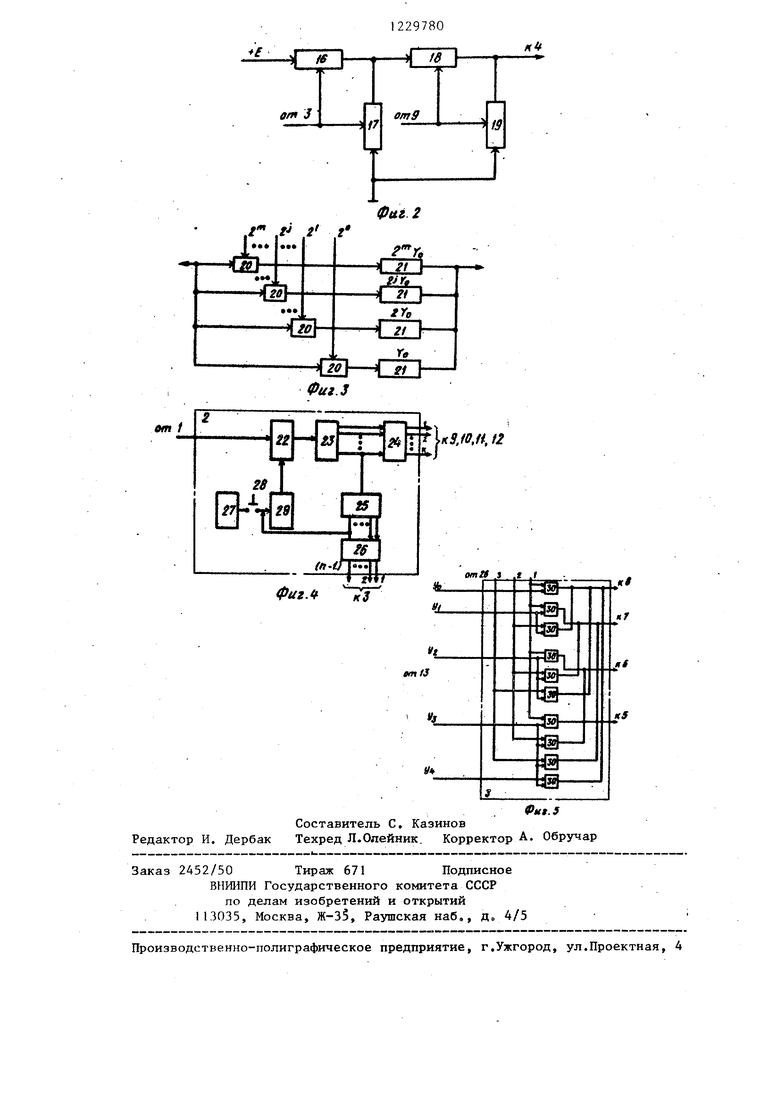

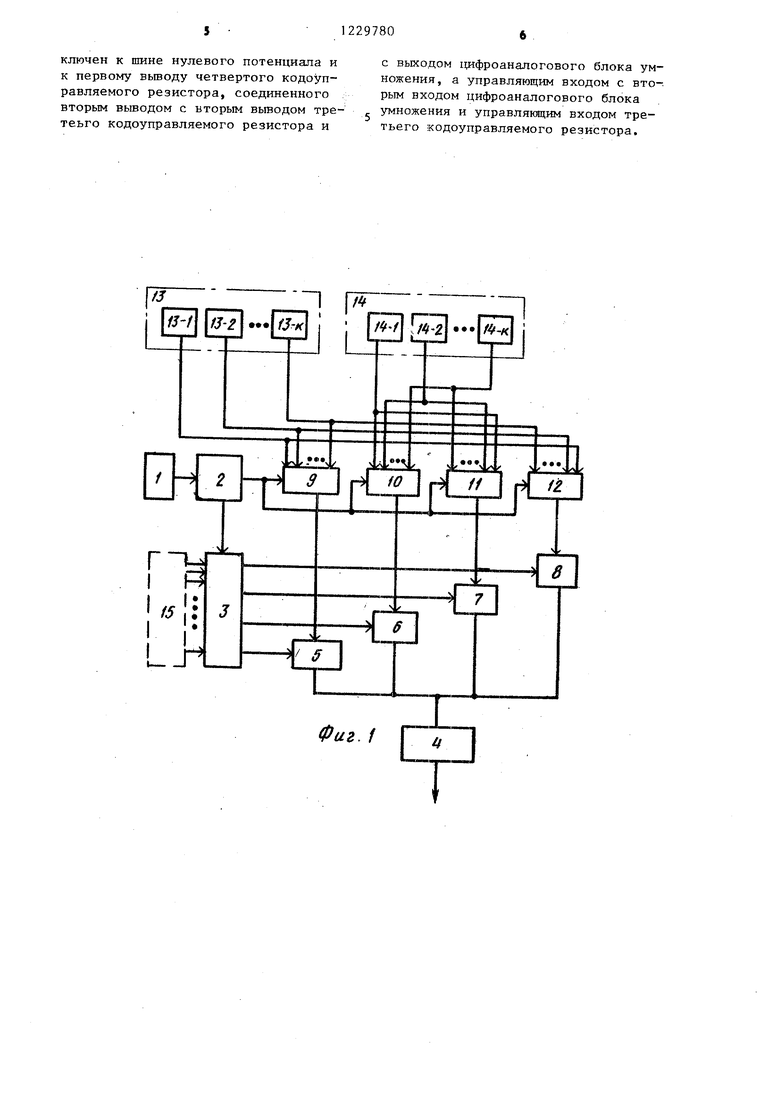

На фиг. 1 изображена блок-схема устройства для воспроизведения функций; на фиг. 2 - схема цифроаналого- вого блока умножения; на фиг. 3 - схема кодоуправляемого резистора; на фиг. 4 - схема блока сийхронизации; на фиг. 5 - схема входного коммутатора.

Устройство для воспроизведения функций содержит (фиг. 1) генератор тактовых импульсов, блок 2 синхронизации, входной коммутатор 3, выходно суммирующий усилитель 4, с первого по четвертый цифроаналоговые блоки 5 8 умножения, с первого по четвертый коммутаторы 9-12 кодов, первую 13 и вторую 14 группы регистров памяти. В качестве источника кодов узловых значений интерполирующих коэффициентов может быть использована дополнительная группа 15 регистров памяти.

Каждый из цифроан;злоговых блоков умножения вьшолнен (фиг. 2) на четырех кодоуправляемых резисторах 17-19, первьш вывод первого из которых соединен с шиной Е опорного напряжения, причем каждьш из кодоуправляемых резисторов 16-19 вьтол- нен (фиг.З) на группе из (fTi+l)ro элементов И 20 (где (vn+0 - разрядность управляющего кода) и группе из (т,+ 1)-го резисторов 21 с проводимостью, изменяющейся по закону Y, Y;- 2-, О 07 ,

где YJ, - проводимость первого резистора.

Блок 2 синхронизации (фиг, 4) содержит элемент И 22, первый счетчик 23 на К состояний, первый дешифратор 24, второй счетчик 25 на (п-1) состояние, второй дешифратор 26, источник 27 напряжения запуска, кнопку 28 и триггер 29.

Входной коммутатор 3 содержит 4 (п-1) группы элементов И 30, соединенные между собой соответствующим образом (фиг. 5).

Принцип действия устройства основан на воспроизведении функции на текущем j-м интервале интерполяции с помощью выражения вида

Б. (t) 1 а

+ L

V О где L ,

j-1

. у... + y..,V. (3)

- коэффициенты

и

1 -3 1

преобразования, связанные с текущим значением аргумента t выражениями вида

t-ЗГ-3t

3t

6t

+ 3t - 4

+ 1

(4)

t,, (1 - t) Так на каждом j-м подынтервале интерполяции t€LO,n, то для системы (3) вьшолняются условия

4(t) (-t)l ,,.

t,(t) r (1-t)/

Поэтому для воспроизведения на каждом J-M подаштервале интерполяции К промежуточных значений функции (в точках t, 0,l/K:, 2/К, ...,1, где К - целое число) предварительно для моментов t; вычисляются по первому и второму соотношениям системы (4) значения коэффи1щентов преобразования

) и t () которые заносятся в перв уто 13 и вторую 14 группы регистров памяти.

Устройство работает следующим образом,

В исходном состоянии счетчики 23 и 25 блока 2 синхронизации обнулены,

на управляющий вход коммутатор 3 поступает сигнал дешифратора 26 (соответствующий нулевому состоянию счет- чи1са 25), а на управляющие входы коммутаторов 9-12 поступает сигнал дешифратора 24 (соответствующей нулевому состоянию счетчика 23). На первый, второй, третий и четвертый выходы коммутатора 3 поступают коды интер

полирующих коэффициентов у , у , и

У,

УЗ

соответственно.

Па выход коммутатора 9 поступает значение (0) из регистра 13-1, на выход коммутатора 10 - значениеt (0 из регистра 14-1, на выход коммутатора 11 - значение 1,2(1) из регистра 14-К, а на выход коммутатора 12 - значения (1) из регистра 13-К. С помощью блоков 5-8 реализуются опера ции перемножения и на выходе суммирующего усилителя 4 формируется сигнал вида

S, (0) i fs(0).y + r,(0).y -ь

+ Г (1)-у l,(l}-yj.

При нажатии кнопки 28 триггер 29. переключается и импульсы генератора 1 начинают поступать на счет

чик 23, осуществляющий последователь-20 устройства, а управляющим входом к нее накопление импульсов. Дешифратор 23 управляет последовательным переключением коммутаторов 9-12 таким образом, что по i-му импульсу генератора 1 (,K-ll) на выход 25 коммутатора 9 поступает значение

первому выходу блока синхронизации, соединенного входом с выходом генер тора тактовьЕх импульсов, отличающееся тем, что, с целью его упрощения за счет сокращения об ема памяти, оно содержит две группы по К( К - количество точек восстан ления функции на под гнтерватте интер поляции) регистров памяти и четыре коммутатора кодов, каждый из которы подключен управляющим входом к второму выходу блока синхронизации, а выходом к второму входу соответству щего цифроаналогового блока yмнoжeн причем каждьш i -и (1 i i к ) регист памяти первой группы соединен выход с i -м информационным входом первого коммутатора кодов и с (к-i+1)-м ин- формационным входом четвертого комму татора кодов, а каждый i-и регистр памяти второй группы подключен выходом к I -му информационному входу вто рого коммутатора кодов и(к-| + 1)-му информационному входу третьего коммутатора кодов.

к-:Т

ИЗ регистра 13-.i , на выход

коммутатора 10 - значениеL (--т) из

регистра ра 11 14-i

значение

на выход коммутато--г(ц1Т из регистра 14-(К-1), а на выход коммута1 п V / -i-1 тора 12 - значение ьД-г-; из регистра 13-(к-1), обеспечивающие формирование промежуточных значений функции на первом подьштервале интерполяции .

При прохождений К-го импульса сче чик 23 переполняется, коммутаторы 9- 12 возвращаются в исходное положение, а в счетчик 25 добавляется единица. В результате на выходы коммутатора 3 поступают коды коэффициентов у , у , у и у соответственно и начинается процесс формирования промежуточных значений функции для второго подынтервала интерполя1Ц1и. По (n-l)-y импульсу счетчик 25 переполняется, триггер 29 переключается в исходное состояние и процесс воспроизведения функции заканчивается. Таким образом, для воспроизведения, промежуточных значений функции на каждом подынтервале интерполяции каждая из групп регистров 13 и 14 используется для задания коэффициен

5 0 r,(t,)

297804

тов преобразования t (t ) и для двух блоков 5 и 8 (6 и 7) умножения соответственно, что позволяет сократить в два раза потребный объем 5 памяти для хранения коэффициентов преобразования.

Формула изобретения

1. Устройство для воспроизведения функций, содержащее выходной суммирующий усилитель, подкпюченньй входами к выходам четырех цифроаналого- вых бЯоков умножения, каждый из которых соединен первым входом с соответствующим выходом входного коммутатора, подключенного информационными входами к шинам ввода узловых значений интерполирующих коэффициентов

20 устройства, а управляющим входом к 5

0

5

0

5

0

первому выходу блока синхронизации, соединенного входом с выходом генератора тактовьЕх импульсов, отличающееся тем, что, с целью его упрощения за счет сокращения объема памяти, оно содержит две группы по К( К - количество точек восстановления функции на под гнтерватте интерполяции) регистров памяти и четыре коммутатора кодов, каждый из которых подключен управляющим входом к второму выходу блока синхронизации, а выходом к второму входу соответствующего цифроаналогового блока yмнoжeнияJ причем каждьш i -и (1 i i к ) регистр памяти первой группы соединен выходом с i -м информационным входом первого коммутатора кодов и с (к-i+1)-м ин- формационным входом четвертого коммутатора кодов, а каждый i-и регистр памяти второй группы подключен выходом к I -му информационному входу второго коммутатора кодов и(к-| + 1)-му информационному входу третьего коммутатора кодов.

2. Устройство по п. 1, о т л и - |Ч а ю щ е е с я тем, что каждый циф- роаналоговый блок умножения содержит четыре кодоуправляемых резистора, первый из которых соединен первым выводом с шиной ввода опорного напряжения, вторым выводом с первыми выводами второго и третьего кодоуправляемых резисторов, а управляющим входом с первым входом цифроаналогового блока умножения и управляющим входом второго кодоуправляемого резистора, второй вывод которого подключей к шине нулевого потенциала и к первому вьгооду четвертого кодоуп- равляемого резистора, соединенного вторым выводом с вторьпя выводом тре- теьго кодоуправляемого резистора и

с выходом цифроаналогового блока умножения, а управляющим входом с вторым входом цифроаналогового блока умножения и управляющим входом третьего кодоуправляемого резистора.

/r«

Фиг.З

от f

Составитель С. Казинов Редактор И. Дербак Техред Л.Олейник. Корректор А. Обручар

Заказ 2452/50 Тираж 671 Подписное ВНГОШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1125632A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1562929A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1987 |

|

SU1495825A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1157552A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1126975A1 |

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение устройства за счет сокращения объема памяти. Устройство содержит генератор такто- вьк импульсов, блок синхронизации, входной коммутатор, выходной суммирующий усилитель и цифроаналоговые блоки умножения. При формировании промежуточных значений функции на каждом подынтервале интерполяции для каждого из блоков умножения необходимо хранить в памяти соответствующий набор коэффициентов преобразования. Упрощение устройства достигается за счет сокращения памяти на основе использования группы регистров для задания коэффициентов преобразования для двух блоков умножения одновременно при взаимообратном порядке и подключения регистров группы к входам указанных блоков умножения через соответствующие коммутаторы. 1 з.п. ф-лы, 5 ил. (О to iNd СО 00

| Амплитудно-импульсный функциональ-Ный пРЕОбРАзОВАТЕль | 1979 |

|

SU842853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор | 1980 |

|

SU911561A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1125632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-10-23—Подача