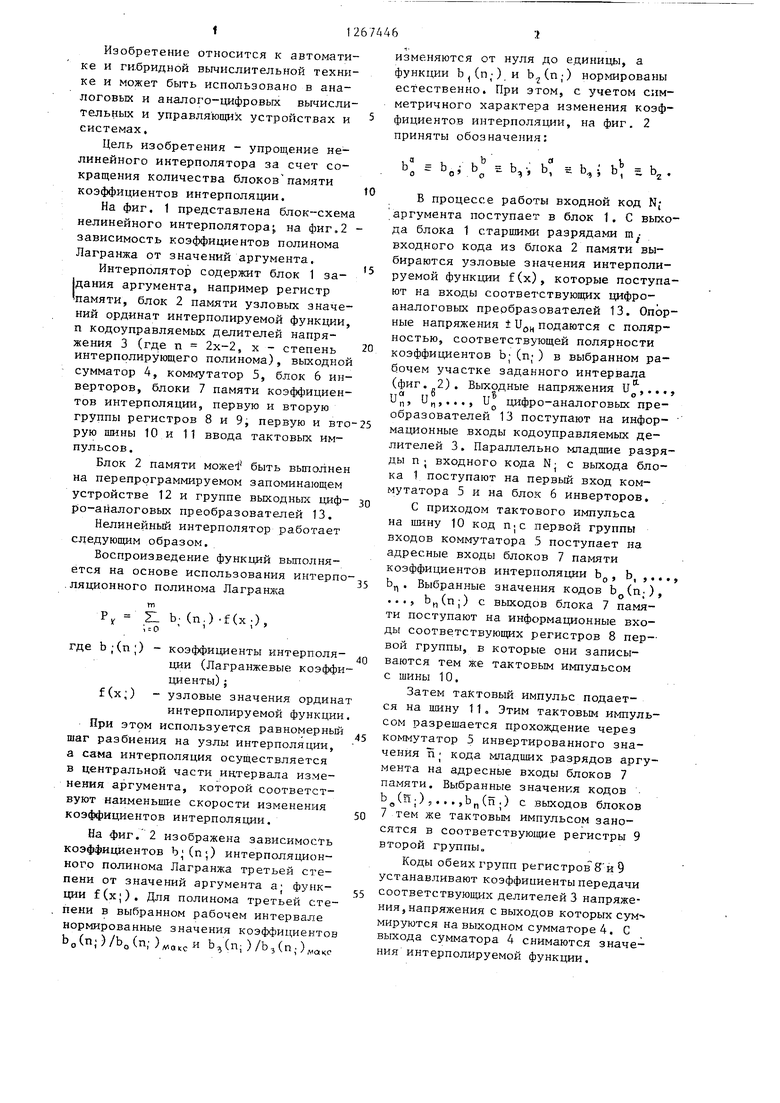

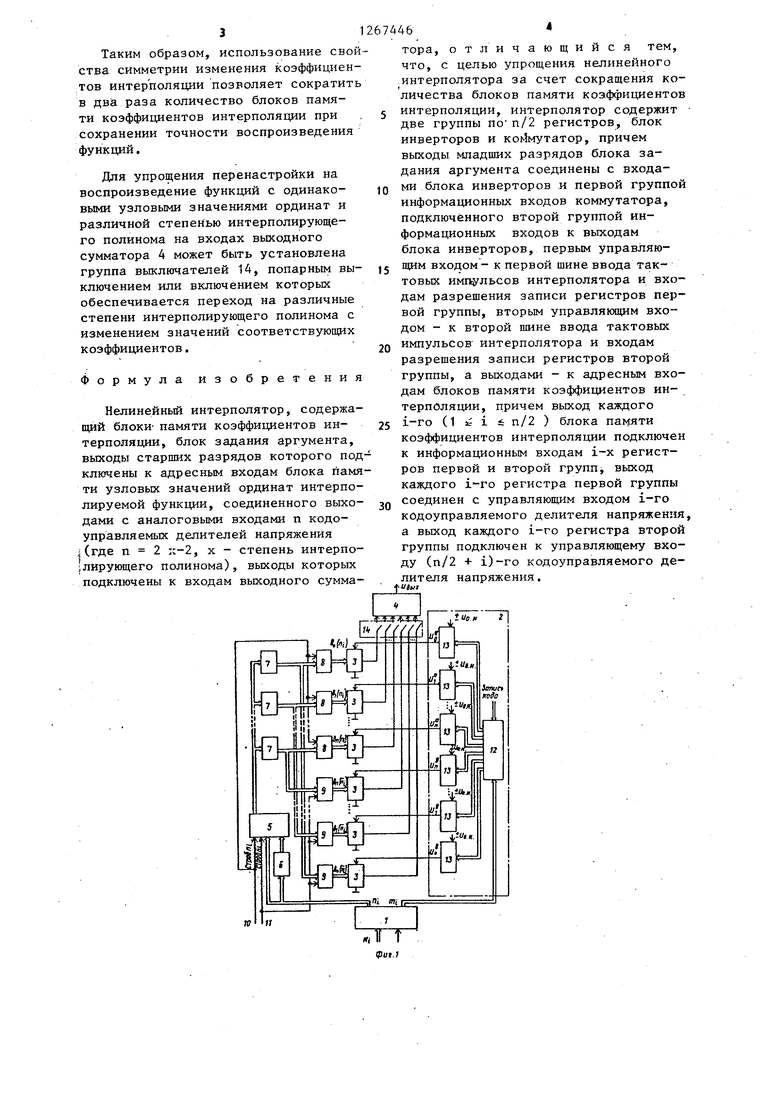

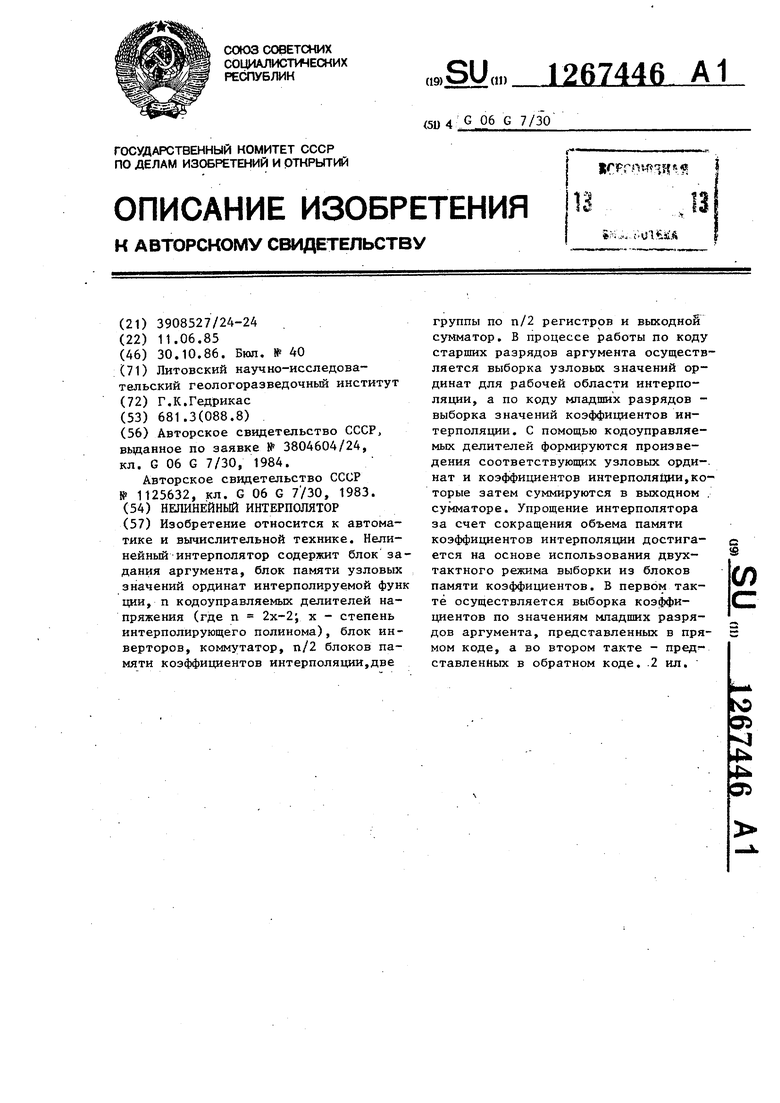

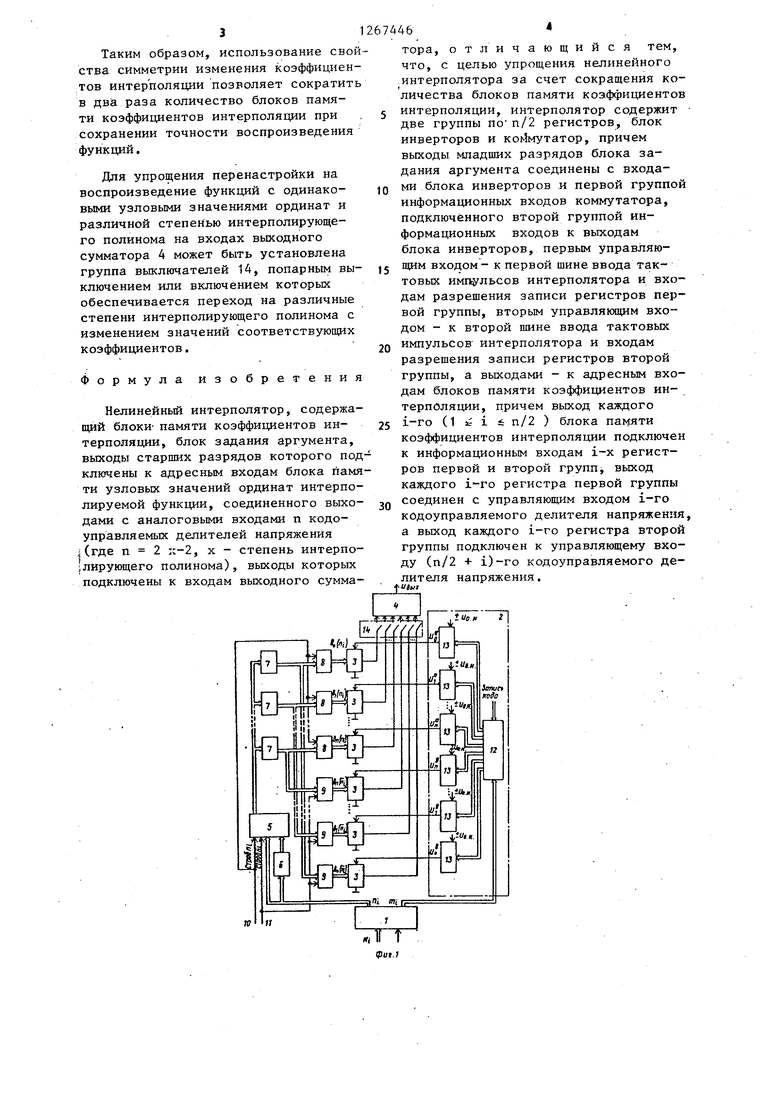

Изобретение относится к автоматике и гибридной вычислительной технике и может быть использовано в аналоговых и аналого-цифровых вычислительных и управляющих устройствах и системах. Цель изобретения - упрощение нелинейного интерполятора за счет сокращения количества блоковпамяти коэффициентов интерполяции. На фиг. 1 представлена блок-схема нелинейного интерполятора;, на фиг,2 зависимость коэффициентов полинома Лагранжа от значений аргумента. Интерполятор содержит блок 1 за1дания аргумента, например регистр памяти, блок 2 памяти узловых значений ординат интерполируемой функции, п кодоуправляемых делителей напряжения 3 (где п 2х-2, х - степень интерполирующего полинома), выходной сумматор 4, коммутатор 5, блок 6 инверторов, блоки 7 памяти коэффициен тов интерполяции, первую и вторую группы регистров 8 и 9, первую и вт рую шины 10 и 11 ввода тактовых импульсов. Блок 2 памяти можеФ быть выполне на перепррграммируемом запоминающем устройстве 12 и группе выходных циф ро-аналоговых преобразователей 13. Нелинейный интерполятор работает следуюпщм образом. Воспроизведение функций вьтолняется на основе использования интерп .ляционного полинома Лагранжа Р, Д1 Ь; (n,).f(x;), где Ь;(п;) - коэффициенты интерполя ции (Лагранжевые коэфф циенты) ; f(x;) - узловые значения ордин интерполируемой функци При этом используется равномерньш шаг разбиения на узлы интерполяции, а сама интерполяция осуществляется в центральной части интервала изменения аргумента, которой соответствуют наименьшие скорости изменения коэффициентов интерполяции. Иа фиг. 2 изображена зависимость коэффициентов Ъ;(п;) интерполяционного полинома Лагранжа третьей степени от значений аргумента а- функций f(x;). Для полинома третьей сте пени в выбранном рабочем интервале нормированные значения коэффициенто Ьо(п;)/Ь„(п; )л,аксИ )/Ь , (п ; ) „о,ко зменяются от нуля до единицы, а ункции ЬДп;).и Ь,,(п;) нормированы стественно. При этом, с учетом симетричного характера изменения коэфициентов интерполяции, на фиг. 2 риняты обозначения: b S b, , b, Н b- i Ь. т; b, в процессе работы входной код N; аргумента поступает в блок 1. С выхода блока 1 старшими разрядами Шу входного кода из блока 2 памяти выбираются узловые значения интерполируемой функции f(x), которые поступают на входы соответствующих цифроаналоговых преобразователей 13. Опорные напряжения i U подаются с полярностью, соответствующей полярности коэффициентов Ь; (п; ) в выбранном рабочем участке заданного интервала (фиг, 2). Выходные напряжения U,..., и, и,.... Up цифро-аналоговых преобразователей 13 поступают на инфор- мационные входы кодоуправляемых делителей 3. Параллельно младшие разряды П; входного кода N; с выхода блока 1 поступают на первый вход коммутатора 5 и на блок 6 инверторов. С приходом тактового импульса на шину 10 код первой группы входов коммутатора 5 поступает на адресные входы блоков 7 памяти коэффициентов интерполяции Ь,, Ь, ,..., Ь . Выбранные значения кодов Ь|(п;), ..., Ь|(п;) с выходов блока 7 памяти поступают на информационные входы соответствующих регистров 8 пер-вой группы, в которые они записываются тем же тактовым импульсом с шины 10. Затем тактовый импульс подается на шину 11„ Этим тактовым импульсом разрешается прохождение через коммутатор 5 инвертированного значения п J кода младщих разрядов аргумента на адресные входы блоков 7 памяти. Выбранные значения кодов Ь(п|),...,Ь(п.) с выходов блоков 7 тем же тактовым импульсом заносятся в соответствую111;ие регистры 9 второй группы,, Коды обеих групп регистров 5и 9 устанавливают коэффициенты передачи соответствуюшд-ix делителей 3 напряжения, напряжения с выходов которых сум-v мируются на выходном сумматоре 4. С выхода сумматора 4 снимаются значения интерполируемой функции. Таким образом, использование свой ства симметрии изменения коэффициен тов интерполяции позволяет сократит в два раза количество блоков памяти коэффициентов интерполяции при сохранении точности воспроизведения функций. Для упрощения перенастройки на воспроизведение функций с одинаковыми узловыми значениями ординат и различной степенью интерполирующего полинома на входах выходного сумматора 4 может быть установлена группа выключателей 14, попарным выключением или включением которых обеспечивается переход на различные степени интерполирующего полинома с изменением значений соответствующих коэффициентов. Формула изобретения Нелинейный интерполятор, содержащий блоки- памяти коэффициентов интерполяции, блок задания аргумента, выходы старших разрядов которого под ключены к адресным входам блока памя ти узловых значений ординат интерполируемой функции, соединенного выходами с аналоговыми входами п кодоуправляемых делителей напряжения i (где п 2 :с-2, х - степень интерпо|лирующего полинома), выходы которых подключены к входам выходного сумма46тора, отличающийся тем, что, с целью упрощения нелинейного интерполятора за счет сокращения количества блоков памяти коэффициентов интерполяции, интерполятор содержит две группы поп/2 регистров, блок инверторов и коммутатор, причем выходы младших разрядов блока задания аргумента соединены с входами блока инверторов и первой группой информационных входов коммутатора, подключённого второй группой информационных входов к выходам блока инверторов, первьм управляю- щим входом - к первой шине ввода тактовых импульсов интерполятора и входам разрешения записи регистров первой группы, вторым управлякяцим входом - к второй шине ввода тактовых импульсов интерполятора и входам разрешения записи регистров второй группы, а выходами - к адресным входам блоков памяти коэффициентов интерполяции, причем выход каждого i-ro (1 t i i n/2 ) блока памяти коэффициентов интерполяции подключен к информационным входам i-x регистров первой и второй группj выход каждого i-ro регистра первой группы соединен с управляющим входом i-ro кодоуправляемого делителя напряжения, а выход каждого i-ro регистра второй группы подключен к управлякицему входу (п/2 i)-ro кодоуправляемого де- лителя напряжения.

.

;%/;

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1125632A1 |

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1987 |

|

SU1495825A1 |

| Интерполятор третьей степени | 1988 |

|

SU1566369A1 |

| Интерполятор | 1986 |

|

SU1396140A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1229780A1 |

| Экстраполятор | 1986 |

|

SU1413651A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Полиномиальный интерполятор | 1983 |

|

SU1239732A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

Изобретение относится к автоматике и вычислительной технике. Нелинейный интерполятор содержит блок задания аргумента, блок памяти узловых значений ординат интерполируемой функ ции, п кодоуправляемых делителей напряжения (где п 2х-2; х - степень интерполирующего полинома), блок инверторов, коммутатор, п/2 блоков памяти коэффициентов интерполяции,две группы по п/2 регистров и выходной сумматор. В процессе работы по коду старших разрядов аргумента осуществляется выборка узловых значений ординат для рабочей области интерполяции, а по КОДУ младших разрядов выборка значений коэффициентов интерполяции. С помощью кодоуправляемых делителей формируются произведения соответствующих узловых орди-. нат и коэффициентов интерполя1щи,которые затем суммируются в выходном , сумматоре. Упрощение интерполятора за счет сокращения объема памяти коэффициентов интерполяции достигас 9 ется на основе использования двух(Л тактного режима выборки из блоков памяти коэффициентов. В первом такте осуществляется выборка коэффициентов по значениям мпадших разрядов аргумента, представленных в прямом коде, а во втором такте - пред ставленных в обратном коде. .2 ил.

| Авторское свидетельство СССР, вьщанное по заявке № 3804604/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1125632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-06-11—Подача