Изобретение относится к автоматике и вычислительной технике.

. Известны двеиадцатиканальные распределители уровней, содержащие триггеры и дешифратор 1.

Недостаток устройств - низкая надежность функционирования.

Наиболее близким техническим решением к предлагаемсМу является двенадцатиканальный распределитель уровней, содержащий четыре .0 -триггера-, С-входы которых соединены с тактовой шиной, а единичные и нулевые выходы подключены ко входам дешифратора, выходы которого, соединены с выходными шинами 2.

К недостаткам известного устройства относится низкая надежност.

Цель изобретения - поёьшенив надежности двенадцатиканальыого распределителя уровней. .

Указанная цель достигается за счет того что в двенадцатиканальном распределителе уровней, содержацем четыре D.-триггера, С-входы которых соединены с тактовой шиной, а единичные и нулевые выходы подключены ко входам дешифратора, выходы которого соединены с выходными шинами, введены интег)атор и одиннадцать

элементов И-НЕ, причем единичный выход первого D. -триггера соединен с первыми входами первого и второго элементов И-НЕ, а нулевой выход подключен к первым входам третьего и четвертого элементов И-НЕ, единичный выход второго D -триггера соединен со вторым входом второго и первым входом пятого элементов И-НЕ, а нуле10вой выход подключен ко второму входу четвертого элемента И-НЕ, единичный выход третьего D -триггера соединен со вторыми .входами первого и третьего- и первым щходом шестого

15 элементов И-НЕ, а нулевой выход подключен ко второму входу пятого элемента И-НЕ, нулевой выход четвертого D. -триггера соединен со вторым входом шестого и первым входом седьмого элементов И-НЕ,. D-вход первого Di гтриггера соединен с выходом восьмого элемента.И-НЕ, входы которого подключены к выходам первого и пятого элементов И-НЕ, D-вход второго

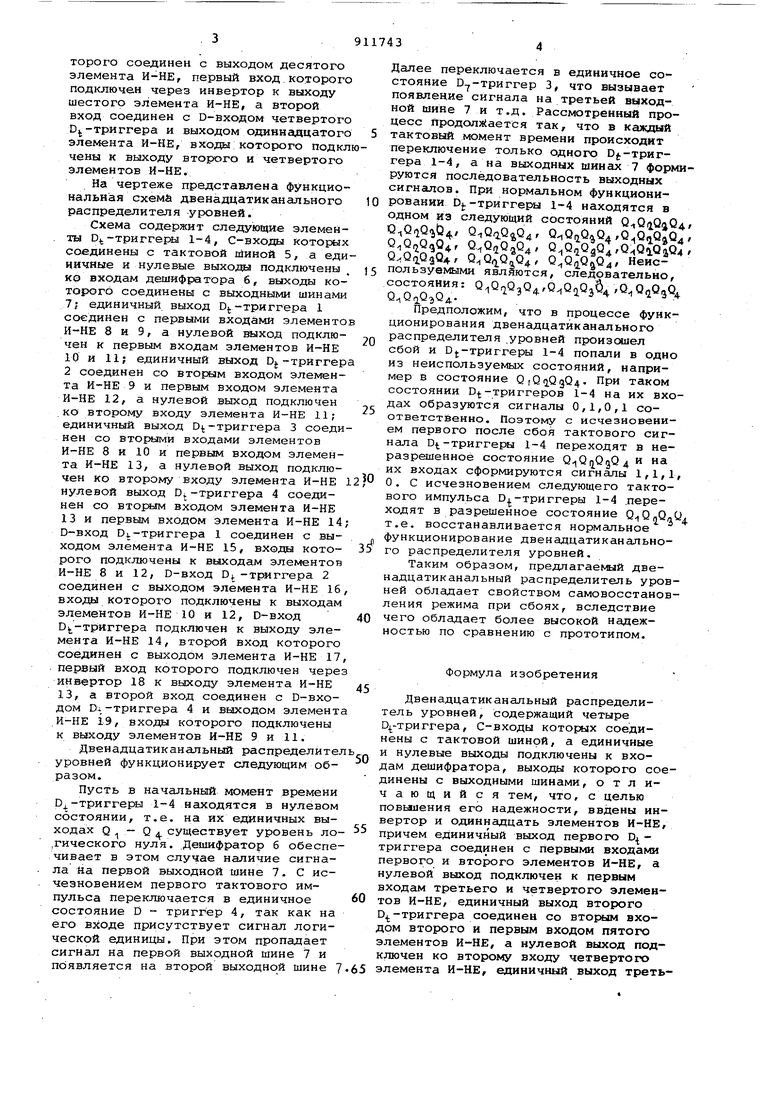

25 ,Dt-триггера соединен с выходом девятого элемента И-НЕ, входы которого подключены к выходам третьего и пятого элементов И-НЕ, D-вход третьего D -триггера подключен к выходу седь30мого элемента И-НЕ, второй вход которого соединен с выходом десятого элемента И-НЕ, первый вход которого подключен через инвертор к выходу шестого элемента И-НЕ, а второй вход соединен с D-входом четвертого D -триггера и выходом одиннадцатого элемента И-НЕ, входы которого подкл чены к выходу второго и четвертого элементов И-НЕ. На чертеже представлена функциональная схема двенадцатиканального распределителя уровней. Схема содержит следующие элементы D,-триггеры 1-4, С-входы которых соединены с тактовой гйиной 5, а еди ничные и нулевые выходы подключены ко входам дешифратора б, выходы которого соединены с выходными шинами 7; единичный выход Dj.-триггера 1 соединен с первыми входами элементо И-НЕ 8 и 9, а нулевой выход подключен к первым входам элементов И-НЕ 10 и 11; единичный выход Dj-триггер 2 соединен со вторым входом элемента И-НЕ 9 и первым входом элемента И-НЕ 12, а нулевой выход подключен ко второму входу элемента И-НЕ 11; единичный выход D -триггера 3 соеди нен со вторыми входами элементов И-НЕ 8 и 10 и первым входом элемента И-НЕ 13, а нулевой выход подключен ко второму входу элемента И-НЕ нулевой выход D.-триггера 4 соединен со входом элемента И-НЕ 13 и первым входом элемента И-НЕ 14 D-вход DV-триггера 1 соединен с выходом элемента И-НЕ 15, входы которого подключены к выходам элементов И-НЕ 8 и 12, D-вход D). -триггера 2 соединен с выходом элемента И-НЕ 16 входы которого подключены к выходам элементов И-НЕ 10 и 12, D-вход D -TpiHrrepa подключен к выходу элемента И-НН 14, второй вход которого соединен с выходом элемента И-НЕ 17 первый вход которого подключен чере инвертор 18 к выходу элемента И-НЕ 13, а второй вход соединен с D-входом Di-триггера 4 и выходом элемент И-НЕ 19, входы которого подключены к выходу элементов И-НЕ 9 и 11. Двенадцатиканальный распределител уровней функционирует следующим образом. Пусть в начальный момент времени 04.-тригге1Ж1 1-4 находятся в нулевом состоянии, т.е. на их единичных выходах Q - Q 4- существует уровень ло ,гического нуля. Дешифратор б обеспе чивает в этом случае наличие сигнала На первой выходной шине 7. С исчезновением первого тактового импульса переключается в единичное состояние D - триггер 4, так как на его входе присутствует сигнал логической единицы. При этом пропадает сигнал на первой выходной шине 7 и появляется на второй выходной шине Далее переключается в единичное состояние D -триггер 3, что вызывает появление сигнала на третьей выходной шине 7 и т.д. Рассмотренный процесс Продсшзйается так, что в каждый тактовьай момент времени происходит переключение только одного D -триггера 1-4, а на выходных шинах 7 формируются последовательность выходных сигналов. При нормальном функционировании DJ.-триггеры 1-4 находятся в одном из следующий состояний Q QrtQnQ, Q, О ОаОаОд Q-iQri04Q4,Q.Q«QjQ., Q,Q,jQqQ4r О.,0гг0з04/ Q QiQgQ4Q-fQiQiQ4 Q QaQaQ Q.. , неиспользуемыми являются, следовательно, состояния: .,0 010364,0,0,1030 О Ог ОэОд Предположим, что в процессе функционирования двенадцатиканального распределителя .уровней произсядел сбой и DJ-триггеры 1-4 попали в одно из неиспользуемых состояний, например в состояние (10з04 При таком состоянии Dt-триггеров 1-4 на их входах образуются сигналы 0,1,0,1 соответственно. Поэтому с исчезновением первого после сбоя тактового сигнала П -триггеры 1-4 переходят в неразрешенное состояние О ОпОпОд и на их входах сформируются сигналы 1,1,1, О. С исчезновением следующего тактового импульса О -триггеры 1-4 .переходят в разрешенное состояние ,Q.Q. т.е. восстанавливается нормальное функционирование двенадцатиканального распределителя уровней. Таким образом, предлагаеьий двенадцатик анальный распределитель уровней обладает свойством самовосстановления режима при сбоях, вследствие чего обладает более высокой надежностью по сравнению с прототипом. Формула изобретения Двенадцатиканальный распределитель уровней, содержащий четыре D -триггера, С-входы которых соединены с тактовой шиной, а единичные и нулевые выходы подключены к входам дешифратора, выходы которого соединены с выходными шинами, о т л ичающийся тем, что, с целью повышения его надежности, ввдены инвертор и одиннадцать элементов И-НЕ, причем единичный выход первого D триггера соединен с первыми входами первого и втогюго элементов И-НЕ, а нулевой выход подключен к первым входам третьего и четвертого элементов И-НЕ, единичный выход второго D -триггера соединен со вторым входом второго и первым входом пятого элементов И-НЕ, а нулевой выход подключен ко второму входу четвертого элемента И-НЕ, единичный выход третьего D -триггера соединен со вторыми входами первого и третьего и первым входом шестого элементов И-НБ, а нулевой выход подключен ко второму входу пятого элемента И-НЕ, нулевой выход четвертого D -триггера соедине со вторым входом шестого и первым входом седьмого элементов И-НЕ, р-вход первого D -триггера соединен с выходом восьмого элемента И-НЕ, входы которого подключены к выходам первого и пятого элементов И-ЙЕ, D-.вход второго Dfc-триггера соединен с выходом девятого элемента И-НЕ, D-вход второго D -триггера соединен с выходом девятого элемента И-НЕ, входы которого подключены к выходам третьего и пятого элементов И-НЕ, D-вход TpeTbeiXD D -триггера подключен к выходу седы«юго элемента

И-НЕ, второй вход которого соединен с выходом десятого элемента И-НЕ, первый вход которого подключен через инвертор к выходу шестого элемента И-НЕ, а второй вход соединен с D-входом четвертого D -триггера и выходом одиннадцатого элемента И-НЕ, входы которого подключены к выходу второго и четвертого элементов И-НЕ.

Источники информации, принятые во внимание при экспертизе

1.Будинский Я. Логические цепи в цифровой технике. М., Связь, 1977, с. 287, рис. 6.136.

2.Букреев И.Н. и др. Микроэлектронные схек&1 цифровых устройств. М., Советское радио , 1975, с. 269, рис. 6.5 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Двенадцатиканальный распределитель уровней | 1982 |

|

SU1040618A1 |

| Многопрограмный распределитель импульсов | 1987 |

|

SU1443163A1 |

| Распределитель импульсов | 1978 |

|

SU771873A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Электронные часы | 1983 |

|

SU1117582A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

Авторы

Даты

1982-03-07—Публикация

1980-03-25—Подача