(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1977 |

|

SU799133A1 |

| Комбинированный прибор | 1990 |

|

SU1718138A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| ФЕРРОЗОНДОВЫЙ МАГНИТОМЕТР | 1998 |

|

RU2153682C1 |

| Способ импульсной стабилизации постоянного напряжения и устройство для его осуществления | 1982 |

|

SU1120304A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ—ЦИФРА | 1972 |

|

SU347910A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

Изобретение относится к вычиспитепь я ной технике и может быть использовано Б измерительных приборах и устройствах ввода цифровых вычислительных машин.

Известен аналого-цифровой преобразователь, содержащий источник опорного напряжения, аналоговые ключи, интегратор, блок управления, генератор импульсов, счетчик и элемент И 1 .

Недостатком устройства является низкая точность преобразования, обусловленная тем, что период интегрирования измеряемого сигнала разбит на поднериоды, в течение которых происходит подкгасчение на вход интегратора опорного напряжения.

Известен аналого-цифровой преобразователь, содержащий источник опорного напряжения, выход которого через первый аналоговый ключ соединен с первым входом интегратора, второй вход которого через второй аналоговый ключ соединен с выходом источника измеряемого снгна- ла, а выход соеди ен с входами порогового устройства и компаратора, выход которого соединен с первыкш входами генератора импульсов и блока формирова.ния периода интегрирования опорного папряжения второй вход которого соодпнен с выходом первого элемента И, а третий вход соединен с упраачяющим входом второго аналогового ключа п выходом блока формироЕйния периода интегрирования измеряемого сигнала, вход которого

10 соединен с первым выходом генератора имл5льсов и первым входом второго элемента И, второй вход которого соединен с выходом блока формттрованмя периода интегрирования опорного н.апряженпя и с

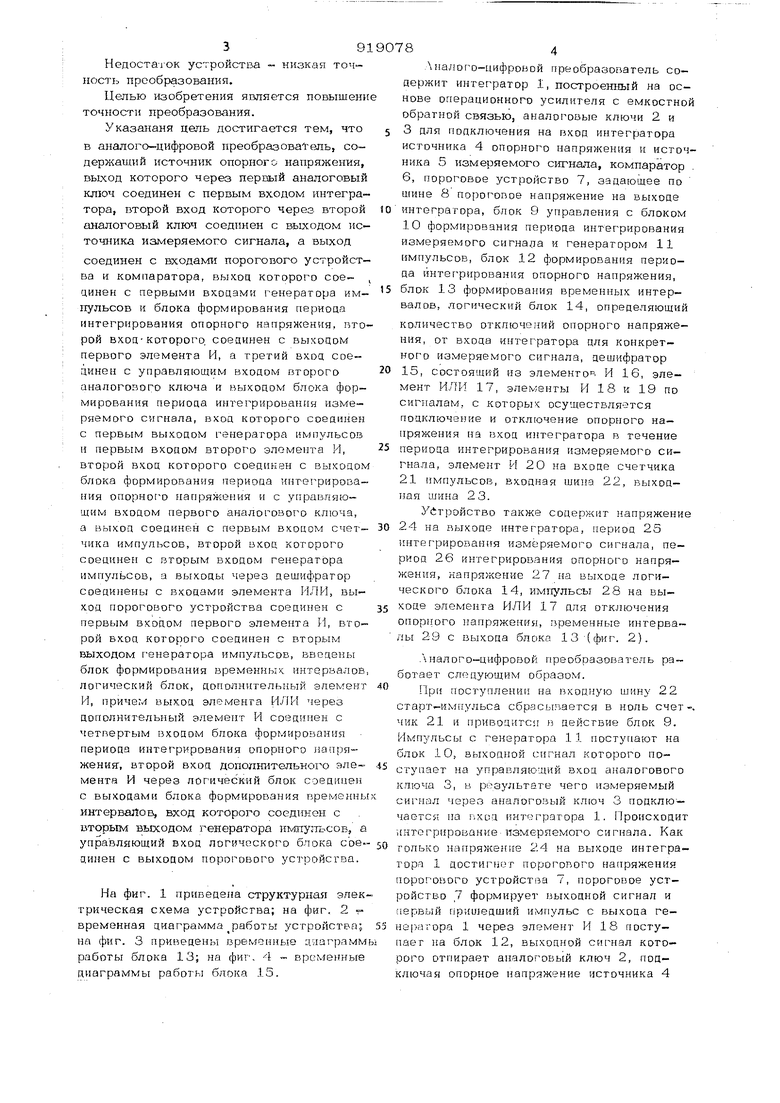

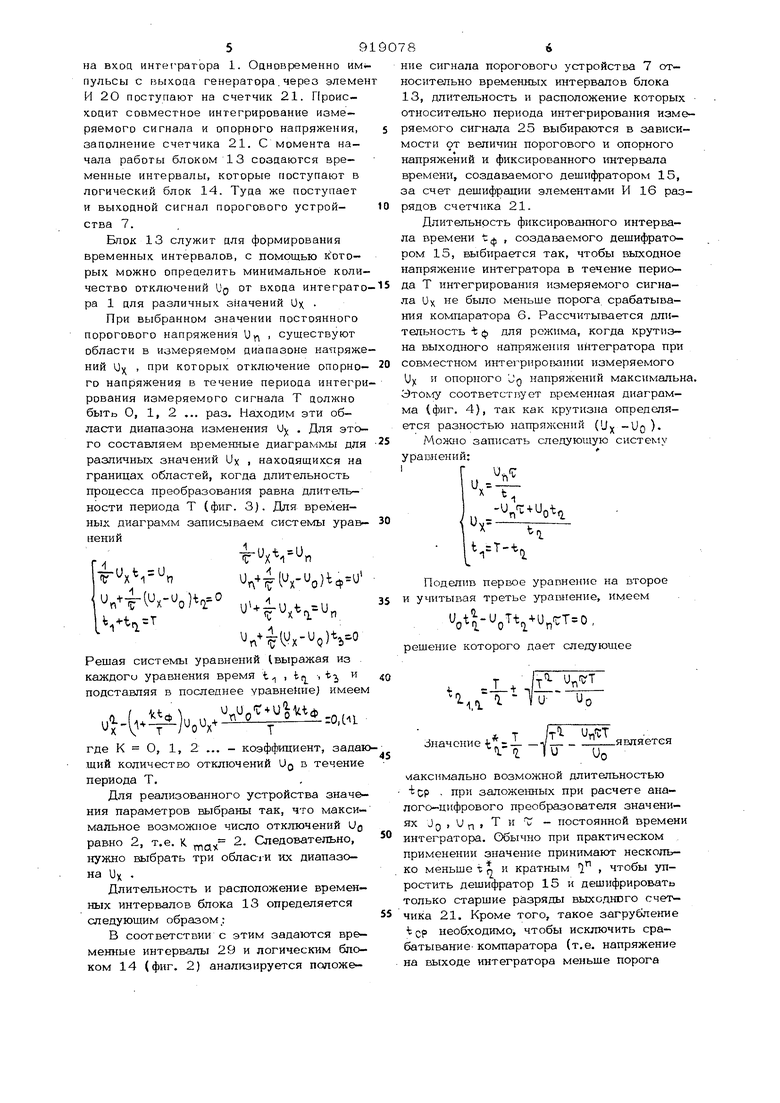

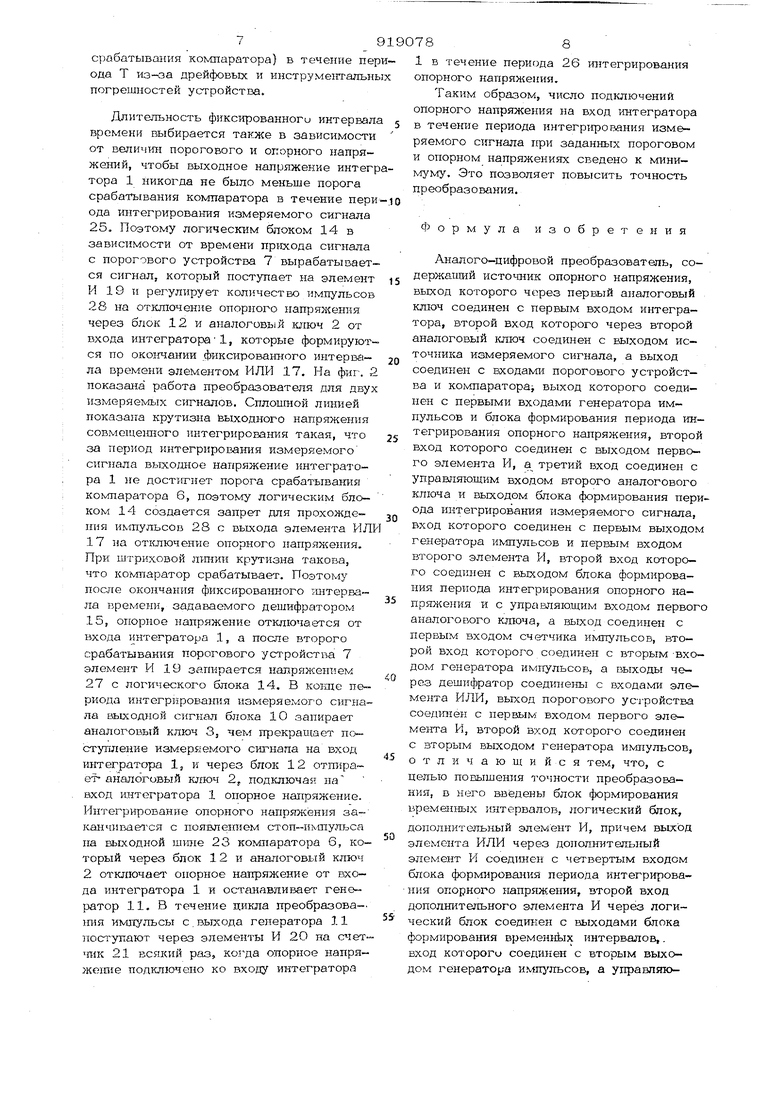

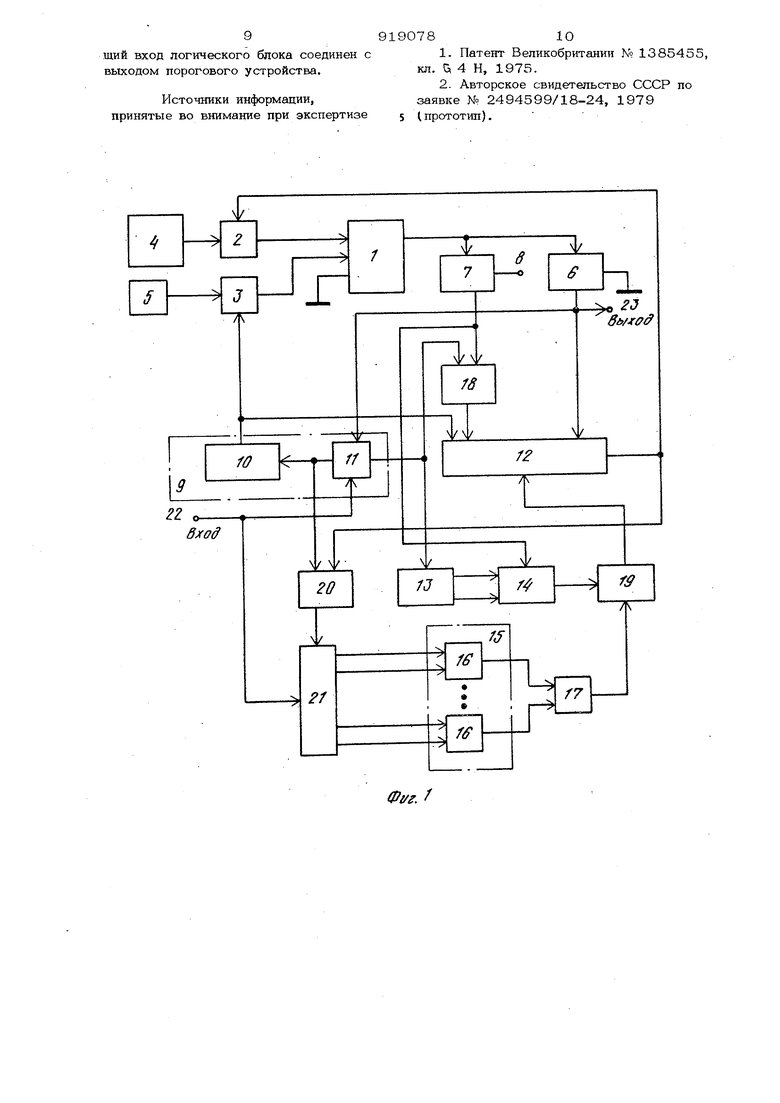

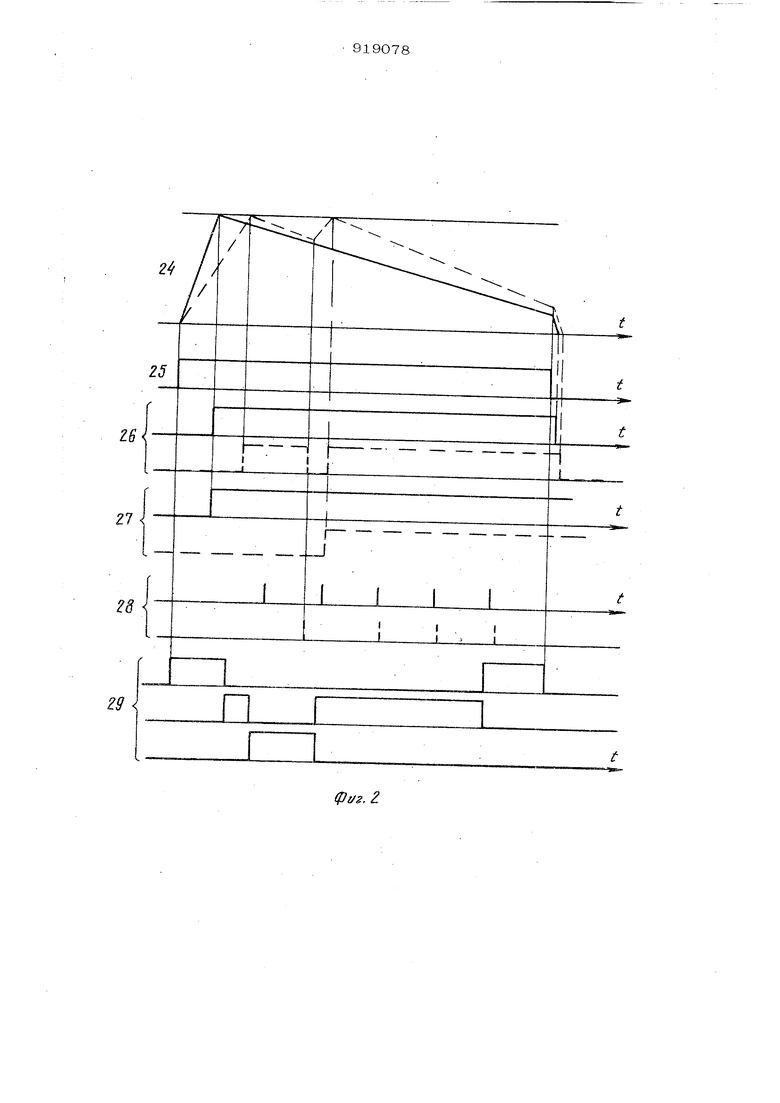

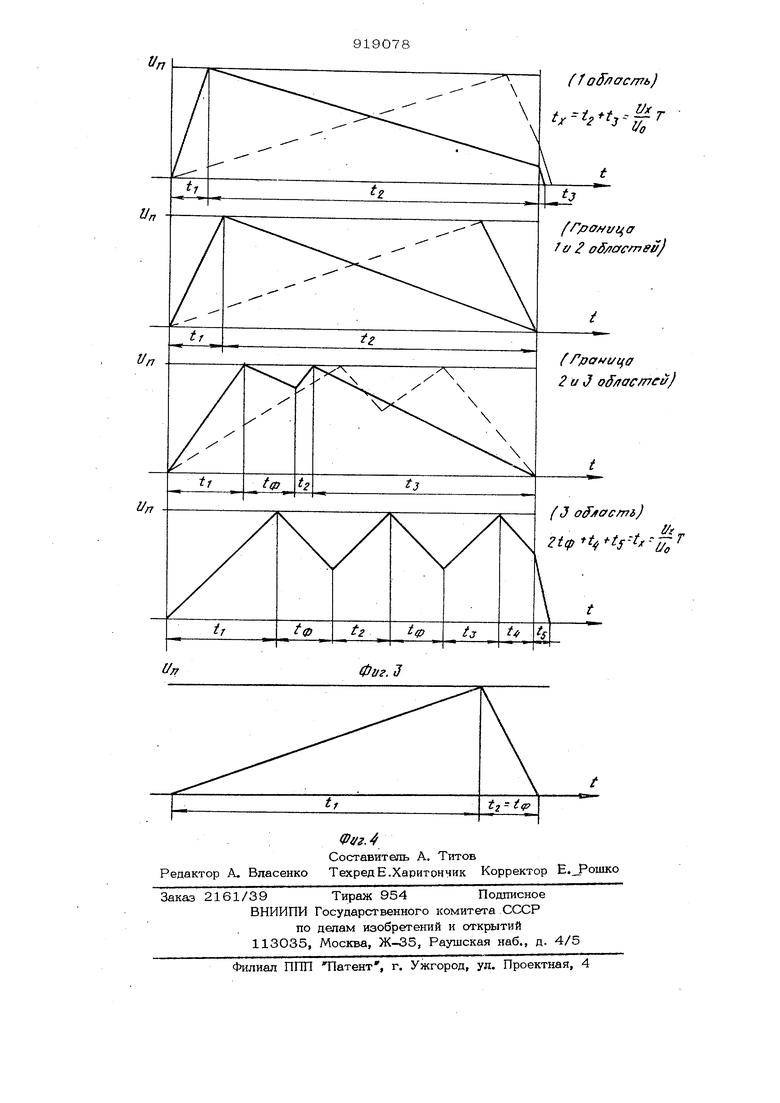

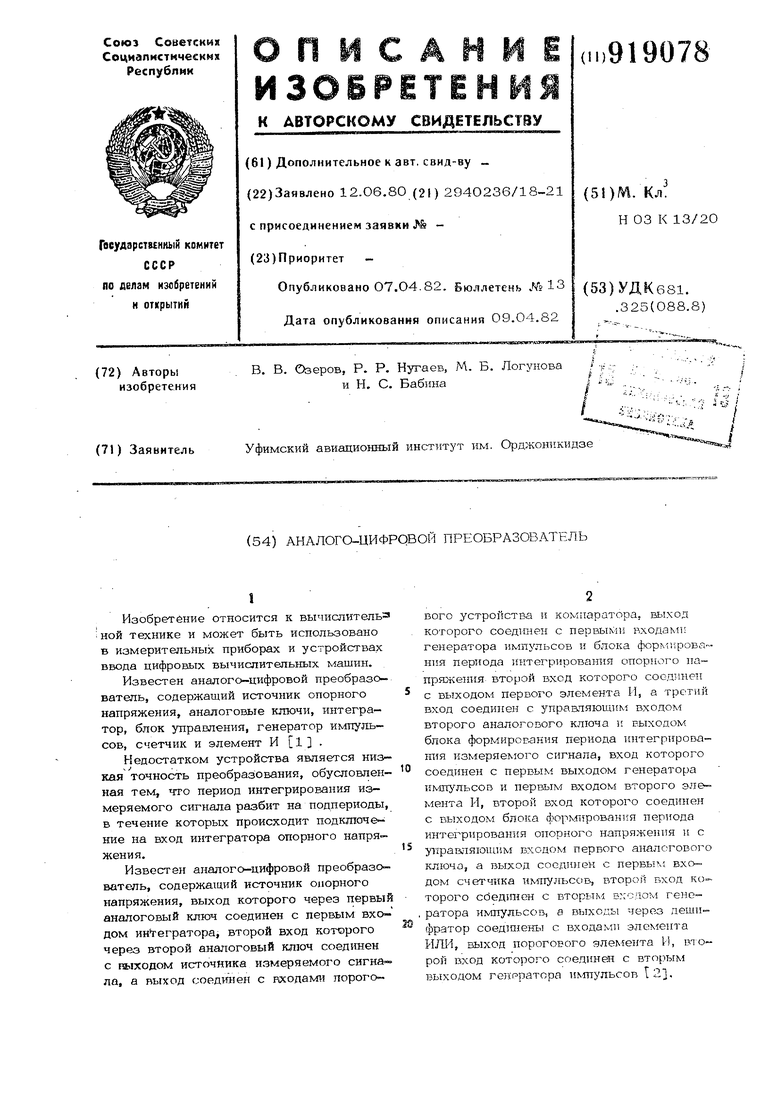

15 уптравлягощим входом первого аналогового ключа, а выход соединен с первым входом счетчика импульсов, второй вход ко торого сс) с вторым входом гене. ратора импульсов, а выходы через дешифратор соедш1ень с входами элемента 11ПИ, выход порогового элемента И, впо рой вход которого соединен с вторым выходом гепрратора и тульсов 12, НедостзАОК устройства - низкая точность преобразования. Целью изобретения является повышени точности преобразования. Указананя цель достигается тем, что в аналого-цифровой преобразоват«5ль, содержащий источник опорного напряжения, выход которого через первый аналоговый ключ соединен с первым входом интегратора, второй вход которого через второй а}шлоговый ключ соединен с выходом источника измеряемого сигнала, а выход соединен с входами порогового устройства и компаратора, выхоа которого соединен с первыми вхоцами генератора импульсов и блока формирования периоцга Интегрирования опорного напряжения, второй вход которого, соецинен с выкоцом первого элемента И, а третий вхоц соединен с управляющим входом второго аналогового ключа и выходом блока формирования периода интегрирования измеряемого сигнала, вход которого соединен с первым выходом генератора импульсов и первым вхоаом второго элемента И, второй вход которого соединен с выходом блока формирования периода интегрировапия опорного напряжения и с управляющим входом первого аналогового ключа, а выход соединен с первым входом счетчика импульсов, второй вхоц которого соединен с вторым входом генератора импульсов, а выходы через дешиф р ор соединены с входами элемента ИЛИ, выход порогового устройства соединен с первым вхоаом первого элемента И, второй вход которого соединен с вторым выходом генератора импульсов, введены блок формирования временные интервалов логический блок, дополнительный эяемергт И, причегл выход элемента ИЛИ через дополнительньп элемент И соединен с четвертым входом блока формирования периода интегрирования опорного напряжения, второй вход дополнительного элемента И через логический блок соединен с выходами блока формирования временны интервалов, вход которого соединен с вторым выходом генератора ик-шу.тьсов, а управляющий вход логического блока сое аинен с выходом nopoiOBoro устройства. На фиг. 1 приведена структурная элек трическая схема устройства; на фиг, 2 временная диаграмма работьг устройства; на фиг. 3 приведены временные анаграмм работы блока 13; на фиг, -4 - временные диаграммы работы блока 15. Хналого-дифровой преобразователь содержит интегратор 1, построенный на основе операционного усилителя с емкостной обратной связью, аналоговые ключи 2 и 3 для подключения на вход интегратора источника 4 опорного напряжения и источника 5 измеряемого сигнала, компаратор 6, пороговое устройство 7, задающее по шине 8 пороговое напряжение на выходе интегратора, блок 9 управления с блоком 10 формирования периода интегрирования измеряемого сигнала и генератором 11 импульсов, блок 12 формирования периода интегрирования опорного напряжения, блок 13 формирования временных интервалов, логический блок 14, определяющий количество отключений опорного напряжения, от входа интегратора для конкретного измеряемого сигнала, дешифратор 15, состоящий из элементов И 16, элемент ИЛИ 17, элементы И 18 и 19 по сигналам, с которых осуществляется подключение и отключение опорного напряжения на вход интегратора в течение периода интегрирования измеряемого сигнала, элемент И 2О на входе счетчика 21 импульсов, входная шина 22, выходная шина 23. Устройство также содержит напряжение 24 на выходе интегратора, период 25 интегрирования измеряемого сигнала, период 26 интегрирования опорного напряжения, напряжение 27 на выходе логического блока 14, импульсы 28 на выходе элемента ИЛИ 17 для отключения опорного напряжения, временные интервалы 29 с выхода блока 13(фиг. 2). .налого-дифровой преобразователь работает следующим образом. При поступлении ва входную шину 22 старт-импульса сбрасывается в ноль счет-, чик 21 и привоцитс1 в действие блок 9. Импульсы с генератора 11 поступают на блок 10, выходной сигнал которого поступает на управляющий вход аналогового ключа 3, в результате чего измеряемый сигнал через аналоговый ключ 3 подклю- чается на вход интегратора 1. Ироисходит интегрирование измеряемого сигнала. Как только напряжение 24 на выходе интегратора 1 достигнет порогового напряжения порогового устройства 7, пороговое устройства 7 формирует выходной сигнал и ЕШрвЕлй приьиедший импульс с выхода ге- не|)агора 1 через элемент И 18 поступает на блок 12, выходной сигнал которого отпирает аналоговый ключ 2, подключая опорное напряжение источника 4 59 на вкоц интегратора 1. Одновременно им пульсы с Fibixoaa генератора, через элеме И 2О поступают на счетчик 21. Проискоцит совместное интегрирование измеряемого сигнала и опорного напряжения, заполнение счетчика 21. С момента начала работы блоком 13 создаются временные интервалы, которые поступают в логический блок 14. Туда же поступает и выходной сигнал порогового устройства 7. Блок 13 служит для формирования временных интервалов, с помощью кото- рых можно определить минимальное коли чество отключений DO от входа интеграто ра 1 для различных значений Ux При выбранном значении постоянного порогового напряжения } , существуют области в измеряемом диапазоне напряже ний U) , при которых отключение опорно- го напряжения в течение периода интегри рования измеряемого сигнала Т должно быто О, 1, 2 ... раз. Находим эти области диапазона изменения Uj . Для этого составляем временные диаграммы для различных значений DX , находящихся на границах областей, когда длительность процесса преобразования равна длитачь- ности периода Т (фиг. 3). Для временных диаграмм записываем системы уран- нений .t и ) .)4 U4. )4-0 Решая системы уравнений (выражая из каждого уравнения время t,, , t( , ti, подставляя в последнее уравнение) имеем ,..(,.),.V., где К О, 1, 2 ... - коэффициент, задак щий количество отключений UQ в течение периода Т. Для реализованного устройства значения параметров выбраны так, что максимальное возможное число отключений UQ равно 2, т.е. К. пач - Следовательно, нужно выбрать три обласч-и их диапазона Ux . Длительность и расположение временных интервалов блока 13 определяется следующим образом; В соответствии с этим задаются временные интервалы 29 и логическим блоком 14 (фиг. 2) анализируется положе786ние сигнала порогового устройства 7 относительно временных интервалов блока 13, длительность и расположение которых относительно периода интегрирования измеряемого сигнала 25 выбираются в зависимости 9т величин порогового и опорного напряжений и фиксированного интервала времени, создаваемого дещифратором 15, за счет дещифрации элементами И 16 разрядов счетчика 21. Длительность фиксированного интервала времени иф , создаваемого дешифратором 15, выбирается так, чтобы выходное напряжение интегратора в течение периода Т интегрирования измеряемого сигнала Ux не было меньше порога срабатывания компаратора 6. Рассчитывается длительность t ф для режима, когда крутизна выходного напряжения интегратора при совместном интегрированиуг измеряемого U)( и опорного JQ напрял еш1й максимальна. Этому соответстБует временная диаграмма (фиг. 4), так как крутизна определяется разностью напряжений (ijj -Do ). Можно записать следующую систему уравнений: и Ц и . хq- t,T-i Поделив первое уравнение на второе и учитывая третье уравнение, имеем , ,, решение которого дает следующее i тт UflCT Значение i z-V-является IUUo у1аксимально возможной длительностью ЬСР при заложенных при расчете аналого-цифрового преобразователя значениях JQ , VJ , Т и - постоянной времени интегратора. Обычно при практ1тч еском . применении значение принимают несколько меньше t о и кратным 1 , чтобы упростить дешифратор 15 и дешифрировать только старшие разряды выходного счетчика 21. Кроме того, такое загрубление t СР необходимо, чтобы исключить срабатывание компаратора (т.е. напряжение на выходе интегратора меньше порога срабатывания компаратора) в течение пе ода Т из-за дрейфовых и инструментальн погрешностей устройства. Длительность фиксированноги интервал времени выбирается также в зависимости от величин порогового и опорного напряже.1Шй, чтобы выходное напряжение интег тора 1 никогда не было меньше порога срабатывания компаратора в течение пери ода интегрирования измеряемого сигнала 25, Поэтому логическим блоком 14 в зависимости от времени сигнала с порогового устройства 7 вырабатывает ся сигнал, который поступает на элемент И 19 и регулирует количество импульсов 28 на отключение опорного напряжения через блок 12 и аналоговый ютюч 2 от входа интегратора1, которые формируют ся по око1гчании фиксированьюго интервала времени элементом ИЛИ 17. На фиг. 2 показана работа преобразователя для дву измеряемьлх сигналов. Сплошной линией показана крутизна выходного напряжения совме1це1шого интегрирования такая, что за период интегрироват1я намеряемого сигнала выходное напряжение интегратора 1 не достигнет порога срабатывания компаратора 6, поэтому логическим блоком 14 создается запрет для прохождения импульсов 28 с выхода элемента ИЛ 17 на отключение опорного панряже1шя. При штриховой крутизна такова, что компаратор срабатывает. Поэтому после окончания фиксированного иштервала времени, задаваемого дешифратором 15, опорное напряжение отключается от входа интегратора 1, а после второго срабатывания порогового устройства 7 элемент И 19 запирается напряжением 27 с логического блока 14. В кокпе периода интегрирования измеряемого сигнала выходной сигнал блока 10 запирает аналоговый ключ 3, чем прекращает не- ступление измеряемого сигнала на вход интегратора I, и через блок 12 отпирает- аналоговый KJrюч 2, подключая на вход интегратора 1 опорное напряжение. Интегрирование опорного напряжения заканчивается с появлением стоп-икшульса на выходной шшю 23 компаратора 6, который через блок 12 и аналоговый ключ 2 отключает опорное напряжение от входа интегратора 1 и ост4шавливаег генератор 11, В течение цикла преобразовання импульсы с , выхода генератора 11 noci-yii-ают через элементы И 2О на счет шк 21 всякий раз, когда опорное напряжеш1е подключено ко входу интегратора 1 в течение периода 26 интегрирования опорного напряжения. Таким образом, число подключений опорного напряжения на вход интегратора в течение периода интегрирования измеряемого сигнала при заданных пороговом и опорном напряжениях сведено к минимуму. Это позволяет повысить точность преобразования. ормула зобретения Аналого-цифровой преобразователь, содержаишй источник опорного напряжения, выход которого через первый аналоговый ключ соединен с первым входом интегратора, второй вход которого через второй аналоговый ключ соединен с выходом источника измеряемого сигнала, а выход соединен с входами порогового устройства и компаратора выход которого соединен с первыми входами генератора импульсов и блока формирования периода интегрирования опорного напряжения, второй вход которого соединен с выходом первого элемента И, а третий вход соединен с управляющим входом второго аналогового ключа и вьпсодом блока формирования периода интегрирования измеряемого сигнала, вход которого соединен с первым выходом генератора импульсов и первым входом второго элемента И, второй вход которого соединен с вых.одом блока формирования периода интегрирования опорного напряжения и с управляющим входом первого аналогоЕюго ключа, а выход соединен с первым входом счетчика импульсов, второй вход которого соединен с вторым вхо- дом генератора импульсов, а выходы через дешифратор соединены с входами элемента ИЛИ, выход порогового устройства соединен с первым входом первого элемента И, второй вход которого соединен с вторым выходом генератора импульсов, о т л и ч а ю щ и и с я тем, что, с целью повышения точности преобразования, в него введены блок формирования bpeMQiHbix интервалов, логический блок, дополнительный элемент И, причем выход элемента ИЛИ через дополнительный элемент И соединен с четвертым входом блока формирования периода интегрирова1ГИЯ опорного напряжения, второй вход дополнительного элемента И через логический блок соединен с выходами блока формирования времеин1з1х интервалов,. вход которого соединен с вторым выходом генератора имщльсов, а управляющий вход логического блока соединен выходом порогового устройства. Источники информации, принятые во внимание при экспертиз

/ 78 1.Патент Великобритании J 1385455 кл. С, 4 Н, 1975. 2.Авторское свидетельство СССР по заявке № 2494599/18-24, 1979 (прототип).

(pi/г.г

Авторы

Даты

1982-04-07—Публикация

1980-06-19—Подача