(54) НАКАПЛИВАЩИЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Накапливающий сумматор | 1985 |

|

SU1319023A1 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

I

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых устройств.

По основному авт. св. № 577528 известен накапливающий сумматор, содержащий в каждом разряде злемент, сложения по модулю два, выход которого подключен к третьему входу первого элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, первый и второй входы элемента сложения по модулю два соединены соответственно с первым и вторым входами переноса в данный .разряд и с первым и вторым входами второго элемента И, выход второго элемента ИЛИ подключен ко входу элемента задержки, выход которого является выходом сигнала переноса в (i+1) разряд сумматора, подключенный к первому входу третьего элемента И, второй вход которого соединен с управляницгй пшной, а выход является

выходом переноса в (i-2) разряд сук. матора, единичный выход триггера со счетным входом является выходом сум(1 i-ro разряда l .

Однако он не позволяет суммировать числа, представленные в избыточных (г, р), система счисления, заполня- : кщие существующий пробел по помехоустойчивости, быстродействию выполнения арифметических операций и диапазону представления чисел между классической и известными Фибоначчи- евыми системами счисления, предназначенными для сквозного контроля информационно-вычислительных систем иве.

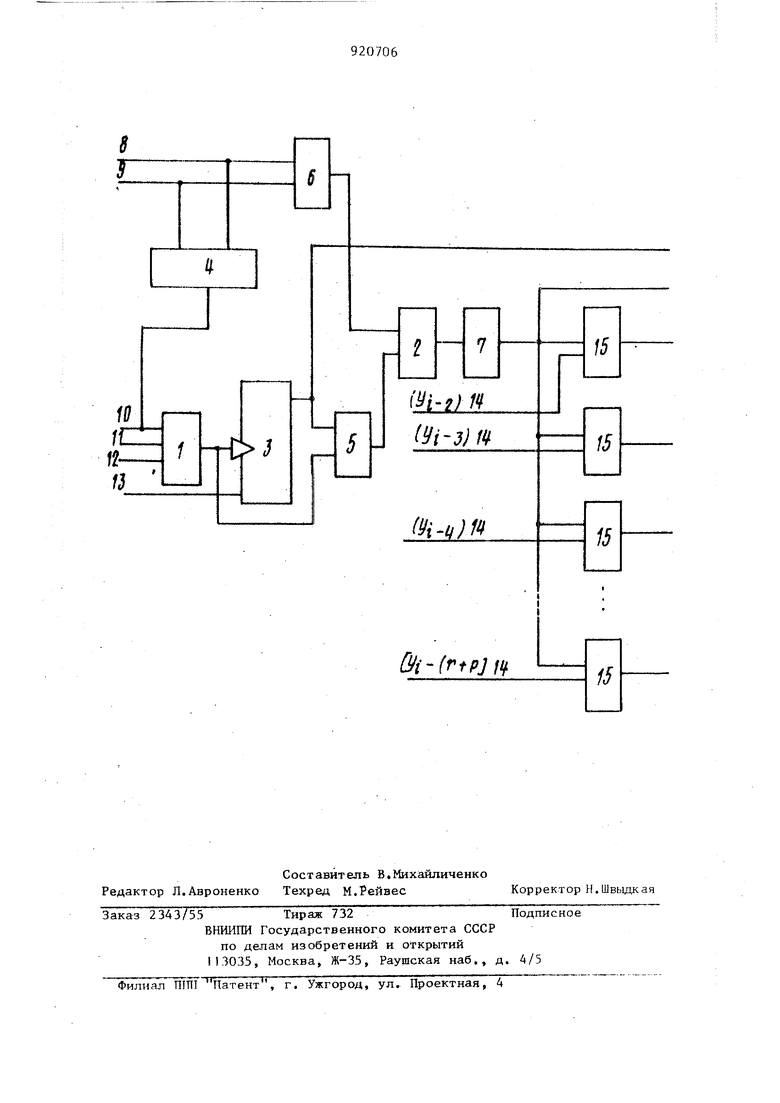

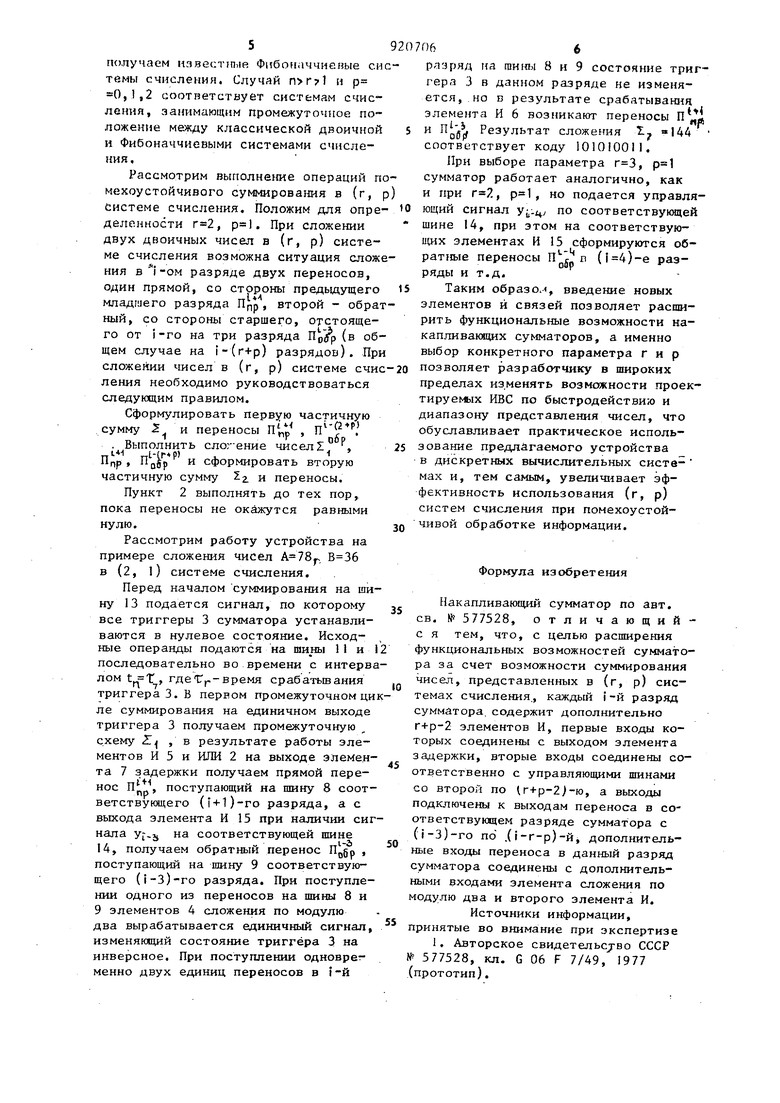

Цель изобретения - расшир 1ше функциональных возможностей известных накапливающих сумматоров за счет возможности суммирования двоичных чисел, представленных в (г,р) системах счисления, при сохранении функции суммирования двоичных чисел в традиционной двоичной и Фибоначчиевой системах счисления. . Поставленная цель достигается тем, что в накапливающем сумматоре, содержащем первый элемент ИЛИ„ пред назначенный для приема двух слагаемых А и Bj- и переноса, поступающего с элемента сложения по модулю два, триггер со счетным входом, пер вый и второй элементы И, второй эле мент ИЛИ и элемент задержки, выход которой соединен с шиной переноса в (i + l) разряд и с первым входом третьего элемента И (k,j), второй вход которого соединен с первой управляющей шиной, а выход соединен с шиной переноса разряда (i-2), раз ряд сумматора содержит дополнительно (г+р-2) элементов И, превые входы которых соединены с выходом элемента задержки, вторые входы соединены соответственно с управляющими шинами со второй по (г+р-2), а выходы подключены к выходам переноса в соответствующем разряде сумматора с (-3)-го по (1-г-р)-й, дополнительные входы переноса в данный раз ряд сумматора соединены с дополнительными входами элемента слолсенця по модулю два и второго элемента И, На чертеже приведена схема i-ro разряда накапливающего сумматора (,...,n, где п - разрядность сум мируемых чисел), Каждый разряд сумматора содержит элементы ИЛИ 1 и 2, триггер 3 со счетным входом, элемент 4 сложения по модулю два, элементы -ИЗ и 6, эл мент 7 задержки, шину 8 прямых.пере носов из предыдущего младшего разря да , шины 9 обратных переносов ср сторонь старпшх разрядов , Пр5р,... ,, шину 10 входного пер носа Cji, входные шины 11 и 12 первого AJ и второго Bj. слагаемых, шину, 13 сброса, управляющие шины 14 (сигналов у.2, y.i У1.(г«) менты И 15. При сложении двоичных чисел в традиционной двоичной системе счисления предлагаемое устрой ство работает известным способом, при этом в работе участвуют элемен ИЛИ 1, триггер 3, шина 13, элемент И 5, элемент ИЛИ 2, элемент 7 задержки, причем выход элемента 7 яв ляется выходом переноса в (+1)-й разряд сумматора, шина 10 переноса входные шины 1 I и 12 слагаемых А,, В , единичный выход триггера 3 является выходом суммы данного i-ro разряда. При слоукении двоичных чисел в Фибоначчиевой системе счисления сумматор .работает известным способон, при этом .в работе участвуют шины II и 12 слагаемых А, В;, шины 8 и 9 переносов, элемент ИЛИ I, триггер 3, шина 13 сброса, элемент И 5, элемент 4 сложения по модулю два, элемент И 6, элемент ИЛИ 2, элемент 7 задержки, выход которого является выходом переноса в (1+1)-й разряд, управляющая шина 4, по которой подается сигнал У(-,2. выходной элемент И 15, выход которого является выходом переноса в (i-2)-и разряд, единичный выход триггера 3 является выходом суммы данного i-го разряда. При сложении двоичных чисел в избыточной (г, р) системе счисления в работе участвуют входные шины tl и 12 слагаемых А1 i шины 8 и 9 прямых и обратных переносов, элемент ИЛИ 1, триггер 3, шина 13 сброса, элемент И 5, элемент 4 сложения по модулю два, элемент И 6, элемент ИЛИ 2, элемент 7 задержки, выход которого является выходом переноса в (|+1)-й разряд и один из элементов И 15, выбор которого зависит от KOHKpeTiibix заданных параметров г и р, причем при, включается в схему элемент И 15, на который подан сигнал при г-З, - элемент И 15, на который подан сигнал у.ц и и т.д. Весовые коэффициенты избыточной (г, р) систе «)1 счисления связаны между собой следующим рекурентным соотношением 1-1 + 1-г+...ibc-2.+.г-р; i p-t-r+1, р+г+2,...; ,2,3,...; ,1,2,...; Ь Ь7 .. . I ; ; , p+4,..., p+r. Здесь г - максимальное количество единиц, находящихся в соседних двоичных разрядах числа и образующих ргизрешенную группу единиц, а параметр р указывает на минимальное количество нулей между разрешенными группами единиц. При и любом р, (г, р) система счисления является классической двоичной, так как при общем числе двоичных разрядов равном п содержит только одну группу разрешенных единиц, весовые коэффициенты которых равны степени двойки. При и ,,2 5 получаем нзвеспшш Фибояаччиевые си темы счисления. Случай и р 0,1,2 соответствует системам счисления, занимающим промежуточное по ложенне между классической двоичной и Фибоначчиевыми системами счисления . Рассмотрим вынолнение операций п мехоустойчивого суммирования в (г, системе счисления. Положим для опре деле.нности , . При сложении двух двоичных чисел в (г, р) системе счисления возможна ситуация слож ния в i-ом разряде двух переносов, один прямой, со стороны предыдущего младшего разряда Прр, второй - обра ный, со стороны старшего, отстоящего от i-ro на три разряда Пд/р (в об щем случае на i-(r+p) разрядов). Пр сложении чисел в (г, р) системе счи ления необходимо руководствоваться следующим правилом. Сформулировать первую частичную 2, и переносы п, , Р обр чисел , . Выполнить слогение ПОР и сформировать вторую г частичную сумму i и переносы. Пункт 2 выполнять до тех пор, пока переносы не окажутся равными нулю. Рассмотрим работу устройства на примере сложения чисел , в (2, 1) системе счисления. Перед началом суммирования на ши ну 13 подается сигнал, по которому все триггеры 3 сумматора устанавливаются в нулевое состояние. Исходные операнды подаются на шины 11 и последовательно во времени с интерв лом , где время срабатьюания триггера 3. В первом промежуточном ци ле суммирования на единичном выходе триггера 3 получаем промежуточную схему 2Г , в результате работы элементов И 5 и ИЛИ 2 на выходе элемен та 7 задержки получаем прямой перенос , поступающий на шину 8 соот ветствукяцего (i-t-l)-ro разряда, а с выхода элемента И 15 при наличии си нала на соответствующей шине 14, получаем обратный перенос , поступающий на шину 9 соответствующего (-3)-го разряда. При поступлении одного из переносов на шины 8 и 9 элементов 4 сложения по модулю два вырабатывается единичный сигнал изменяющий состояние триггера 3 на инверсное. При поступлении одновретменно двух единиц переносов в i-й nh разряд на гаишл 8 и 9 состояние триггера 3 в данном разряде не изменяется, но в результате срабатывания элемента И 6 возникают переносы П и nJjA Результат сложения 1 144 соответствует коду 101010011. При выборе параметра , сумматор работает аналогично, как и при г-., , но подается управля- ющий сигнал у;,: по соответствующей шине 14, при этом на соответствующих элементах И 15 сформируются обратные переносы D ()-e разряды и т.д. Таким образ о., введение новых элементов и связей позволяет расширить функциональные возможности накапливакяцих сумматоров, а именно выбор конкретного параметра г и р позволяет разработчику в широких пределах изменять возможности проектиpye fcIX ИВС по быстродействию и диапазону представления чисел, что обуславливает практическое использование предлагаемого устройства в дискретных вычислительных систвмах и, тем самым, увеличивает эффективность использования (г, р) систем счисления при помехоустойчивой обработке информации. Формула изобретения Накапливающий сумматор по авт. св. № 577528, отличающийс я тем, что, с целью расширения функциональных возможностей сумматора за счет возможности суммирования чисел, представленных в (г, р) системах счисления, каждый i-и разряд сумматора, содержит дополнительно г+р-2 элементов И, первые входы которых соединены с выходом элемента задержки, вторые входы соединены соответственно с управляющими шинами со второй по г+р-2)-ю, а ВЬЕХОДЫ подключены к выходам переноса в соответствующем разряде сумматора с (i-3)-ro по ,(-г-р)-й, дополнительные входы переноса в данный разряд умматора соединены с дополнительыми входами элемента сложения по одулю два и второго элемента И. Источники информации, ринятые во внимание при экспертизе 1. Авторское свидетельс/во СССР 577528, кл. G 06 F 7/49, 1977 прототип).

s

г

/5

f

( 1 )

/5

D/t-(

15

Авторы

Даты

1982-04-15—Публикация

1980-03-19—Подача