Изобретение относится к вычислительной технике и может быть использовано для параллельного суммирования многоразрядных двоичных чисел.

Цель изобретения - упрощение сумматора .

На чертеже представлена функциональная схема накапливающего сумматора.

Накапливающий сумматор содержит триггер 1, три элемента И 2-4, два элемента ИЛИ 5 и 6, элемент 7 задержки, первый сумматор по модулю два 8, входы 9 и 10 соответствующих разрядов первого и второго слагаемых, вход 11 переноса из (i-l)-ro разряда, вход 12 переноса из (1+2)-го разряда сумматора, выход 13 суммы данного разряда сумматора, выход 14 переноса в .(1+1)-й разряд сумматора, выход 15 переноса в (1-2)-й разряд сумматора, вход 16 сброса сумматора, вход 17 разрешения сложения в Фибо- наччиевой системе счисления, три элемента И 18-20, элемент -ИЛИ 21, второй сумматор по модулю два 22, три элемента ИЛИ 23-25, элемент И 26, вход 27 переноса из (i+5)-ro разряда, вход 28 переноса из (i+3)-ro разряда сумматора, вход 29 разрешения сложения в минимальной системе счис-, ления, элемент И 30, выход 31 переноса в (1-3)-й разряд сумматора, выход 32 переноса в (1-5)-й разряд сумматора.

Любое натуральное, число А в минимальной системе счисления представляется в виде многочлена:

А ZIa;((i),

где а

,1

50

Го при

((i) I 1 при 0. (-1) v(i-2)+v(i-3) при 171. .

Значение Cp Cn+l) является мощностью п-разрядного минимального кода.

Предлагаемый способ сложения основан на соотношении

V(i) + V(i)(f (i+1)+V(i-3) + (i-5) (2) 55

выт екающем из рекуррентного соотношения (1), следовательно, правило

сложения представляется следующим выражением:

(3)

5

0

5

0

5

0

5

0

5

Учитывая, что в минимальной системе счисления минимальная форма представления чисел предполагает наличие после каждой единицы не менее четырех нулей, можно заметить, что сигналы переносов в (1+1)-й, (1-3)-й разряды осуществляются беспрепятственно, возможное наличие единицы в (i-5)-M разряде приводит к необходимости появления промежуточных сумм в ряде случаев.

Следовательно, алгоритм сложения чисел, представленных в минимальной системе счисления, имеет следующий вид:

1.Образование промежуточной суммы и сигнала переноса.

2.Суммирование промежуточной суммы и сигнала переноса.

3.Повторение пунктов 1 и 2 до тех пор, пока промежуточная сумма не станет эквивалентна окончательной, о чём будет свидетельствовать нулевой сигнал переноса.

Особенностью предлагаемого способа сложения является поступление переносов в i-й разряд из (i-l)-ro, (i+3)-ro, (г+5)-го разрядов суммато ра при использовании накапливающего типа суммирования. Сигналы переноса из указанных разрядов участвуют как в формировании суммы данного разряда, так и в выработке сигнала переноса , из i-ro разряда.

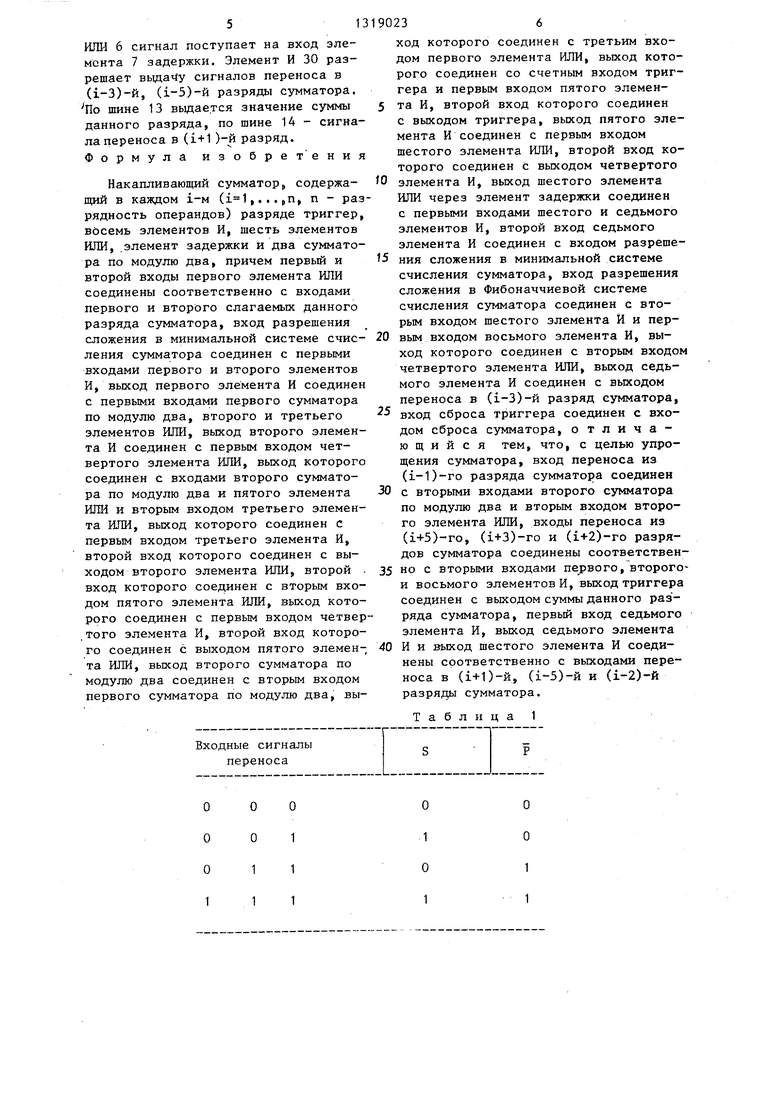

Конкретно при поступлении двух нулевых и одного единичного сигнапов сигнал, участвующий в формировании суммы, равен 1, а сигнал переноса - 0. При единичных и одном нулевом сигналах переноса сигнал, участвующий в процессе суммирования (S),равен О, а сигнал переноса (Р) равен 1, при наличии всех единичных сигналов переноса и сигнал переноса из данного разряда и сигнал, участвующий в формировании суммы, равны 1, что описано в табл.1.

Этой особенностью вызвана необходимость введения в сумматор устройства, способного реализовать функции в соответствии с табл.1.

Сумматор работает следующим образом.

При сложении чисел, представленных в традиционной системе счисления, на первой и второй управляющих шинах присутствует логический ноль. При этих условиях cyNiMaTop осуществляет следующий алгоритм сложения:

y(i)+(,(i)V(i+1).

Следовательно, сумматор подключен к входной шине переноса из (i-1)-ro разряда, выходным шинам суммы данного разряда и переноса в (1+1)-й разряд. Разряды слагаемых подаются на вход элемента ИЛИ 5, с выхода которого результат подается на счетный вход триггера 1 и вход элемента И 3, результат суммирования поступает на вход суммы данного разряда, а также на вход элемента ИЗ, формирующего перенос из данного разряда, поступающий на вход элемента ИЛИ 6, затем на элемент 7 задержки и на вход переноса в (141)-й разряд.

Сигнал переноса в рассматриваемый разряд поступает на входную щину переноса из (i-l)ro разряда, подается на вход сумматора по модулю два 8, без изменений проходит сумматор по модулю два 22 и поступает на вход элемента ИЛИ 5.

Сигнал переноса в данный разряд участвует только в процессе сложения из него может быть сформирован сиг- нал переноса из данного разряда.

При работе с числами, представленными в Фибоначчиевой системе счисления, логическая единица подается на первую управляющую шину. Разряд сум- матора подключается к входным шинам переноса из (1-1}-го, (i+2)-ro разрядов и входным шинам переноса в (1+1)-й, (1-2)-й разряды, а также шине входа суммы данного разряда. Следовательно, сумматор выполняет следующий алгоритм сложения:

Ct (i)+(f (i)V(i+1)+V(i-2)

и как видно, оперирует со следующими сигналами: входными сигн1лами переносов, разрядами слагаемых.

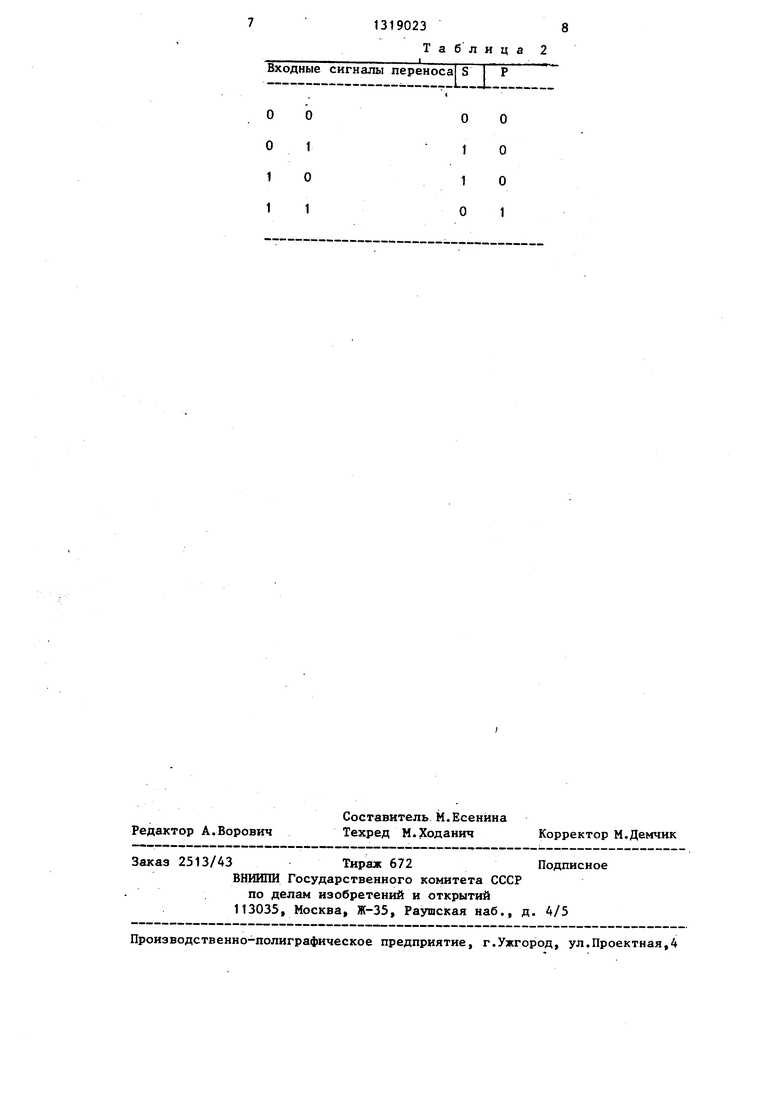

Наличие двух сигналов переноса в данный разряд приводит к необходимости получения из них сигнала, уча ствующего в сложении, и сигнала переноса из .данного разряда, что поясняется в табл.2.

15

5

,0

, 35

45

20

25

30

50

55

Сигналы переноса поступают: сигнал переноса из (1+2)-го разряда на вход элемента И 20, через элемент ИЛИ.21 на вход сумматора по модулю два 8, сигнал переноса из (i-1)-ro разряда на другой вход сумматора по модулю два 8, который и осуществляет работу в соответствии со столбцом S табл.2, а также на входы элементов ИЛИ 24 и 25 и элементов ИЛИ 23 и 24 соответственно. Элементы ШШ 23-25, элементы И 2 и 26 образуют устройства, формирующие сигнал переноса в соответствии со столбцом Р табл.2. Сигнал переноса с выхода элемента И 2 поступает на вход элемента ШШ 6, после которого поступает-на элемент 7 задержки и далее на вход элемента И 4, а также выход переноса в (1+1)-й разряд, после элемента И 4 сигнал переноса вЬщается в (1-2)-й разряд сумматора. Сложение разрядов слагаемых осуществляется так же, как и в традиционной системе счисления.

При работе сумматора с числами, представленными в двоичной системе счисления, осуществляется алгоритм сложения, представленный соотношением (2) ,

Разряд сумматора подключен наличием логической единицы на второй управляющей шине к входным щннам переноса из (i-l)-ro, (i+5)-ro разрядов, выходным шинам суммы данного разряда, переносов в (1+1)-й,(-3)-й, (1-5)-й разряды.

Работа устройства с учетом трех сигналов переноса поясняется табл.1.

Разряды слагаемых поступают на входы элемента ИЛИ 5, на третий вход которого подается сигнал, участвующий в процессе сложения, с выхода сумматора по модулю два 22, сформированный из входных сигналов переноса в соответствии со столбцом ,S табл.1, с выхода элемента ИЛИ 5 - на вход триггера 1, где происходит суммирование разрядов слагаемых. Результат суммирования выдается на выход 15. Элемент И 3 формирует сигнал переноса из разрядов слагаемых и сигнала, поступающего с выхода сумматора по модулю два.22, и вьщает его на вход элемента ИЛИ 6, который учитывает также и сигнал переноса, сформированный элементами ИЛИ 23-25, элементами И 2 и 26 из входных сигналов переноса. С выхода элемента

ИЛИ 6 сигнал поступает на вход элемента 7 задержки. Элемент И 30 разрешает выдаг у сигналов переноса в (1-3)-й, (1-5)-й разряды сумматора. По шине 13 вьщается значение суммы данного разряда, по шине 14 - сигнала переноса в(i+1)-й разряд. Формула изобрет ения

Накапливающий сумматор,, содержащий в каждом i-M (,...рП, п - разрядность операндов) разряде триггер, восемь элементов И, шесть элементов ИЛИ, элемент задержки и два сумматора по модулю два, причем первый и второй входы первого элемента ИЛИ соединены соответственно с входами первого и второго слагаемых данного разряда сумматора, вход разрешения сложения в минимальной системе счисления сумматора соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с первыми входами первого сумматора по модулю два, второго и третьего элементов ИЛИ, выход второго элемента И соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с входами второго сумматора по модулю два и пятого элемента ШШ и вторым входом третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом второго элемента ШШ, второй . вход которого соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с первым входом четвер- ,того элемента И, второй вход которого соединен с выходом пятого элемен-, та ИЛИ, выход второго сумматора по модулю два соединен с вторым входом первого сумматора по модулю два, выход которого соединен с третьим входом первого элемента ИЛИ, выход которого соединен со счетным входом триггера и первым входом пятого элемента И, второй вход которого соединен с выходом триггера, выход пятого элемента И соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом четвертого

элемента И, выход шестого элемента ИЛИ через элемент задержки соединен с первыми входами шестого и седьмого элементов И, второй вход седьмого элемента И соединен с входом разрешения сложения в минимальной системе счисления сумматора, вход разрешения сложения в Фибоначчиевой системе счисления сумматора соединен с вторым входом шестого элемента И и первым входом восьмого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход седьмого элемента И соединен с выходом переноса в (1-3)-й разряд сумматора,

вход сброса триггера соединен с входом сброса с умматора, отличающийся тем, что, с целью упро

щения сумматора, вход переноса из (i-1)-ro разряда сумматора соединен

с вторыми входами второго сумматора по модулю два и вторым входом второго элемента ШШ, входы переноса из (i+5)-ro, (i+3)-ro и (i+2)-ro разрядов сумматора соединены соответствено с вторыми входами первого, второго- восьмого элементов И, выход триггера соединен с выходом суммы данного разряда сумматора, первый вход седьмого элемента И, выход седьмого элемента

И и вькод шестого элемента И соединены соответственно с выходами переноса в (1-«-1)-й, (1-5)-й и (1-2)-й разряды сумматора.

Т а б л II ц а 1

О 1

О 1

О О 1 1

Входные сигналы переноса

ОО

01

1О

11

ор А.Ворович 2513/43

Составитель М.Есенина Техред М.Ходанич

Корр Подп

Тираж 672 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

13190238

Таблица 2

ILL

0О

1о

1о

о1

Корректор М.Демчик Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Сумматор избыточной минимальной системы счисления | 1988 |

|

SU1539768A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

Изобретение относится к вычислительной технике и передаче данных и может быть использовано для параллельного суммирования многоразрядных двоичных чисел. Цель изобретения - упрощение устройства. Накапливающий сумматор содержит триггер 1, восемь элементов Я 2,3,4,18,19,20, 26,30, шесть элементов ИЛИ 5,6,21 23,24,25, элемент задержки 7, два сумматора по модулю два 8,22. Предлагаемый сумматор может быть использован для построения вычислительных систем, адаптивных по помехоустойчивости п классу решаемых задач. Использование данного сумматора позволит уменьшить аппаратурные затраты, необходимые ранее для обнаружения и коррекции ошибок. 1 ил., 2 табл. 13

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-23—Публикация

1985-09-02—Подача