1

Изобретение относится к вычислительной технике и может быть применено в комплексе с цифровой вычислительной машиной или в спецпроцессорах для оперативного вычисления показательно-степенной Лункции, например, в системах автоматического :управления динамическими объектами.

Известно устройство для возведения в дробную степень,содержащее блок памяти, блок возведения в дробную степень, блок извлечения корня, схемы сравнения, блоки ключей, цифро-аналоговый преобразователь, подключенный ко второму входу схемы сравнения, соединенной своим выходом с управляющим входом блока возведения в дробную степень П.

Недостатками известного устройства являются ограниченные функциональ- ные возможности (так как число вое-, производимых функций с дробными показателями ограничено), сложность изза наличия блока памяти и необходимости цифро-аналогового преобразования, а также относительно низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее первый входной регистр, три блока умножения, два запоминающих блока, второй входной регистр, причем выход старших разрядов второго входного регистра соеди10нен со входом второго запоминающего блока, а выход младших разрядов - с первым входом второго блока умноже- . ния 2 .

Недостаток известного устройства 15ограниченные функциональные возможности. Так как в устройстве вычисляется только та функция z х , для которой в блоках памяти записано значение натурального логарифма старших

30

vcr ,

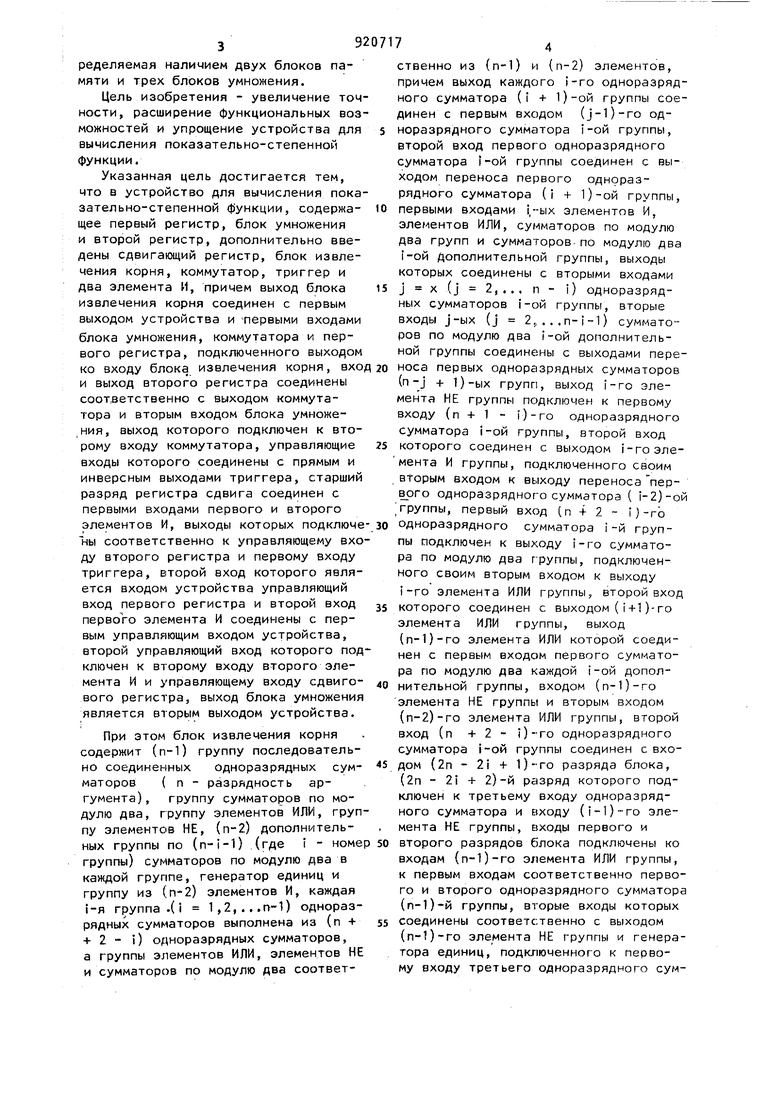

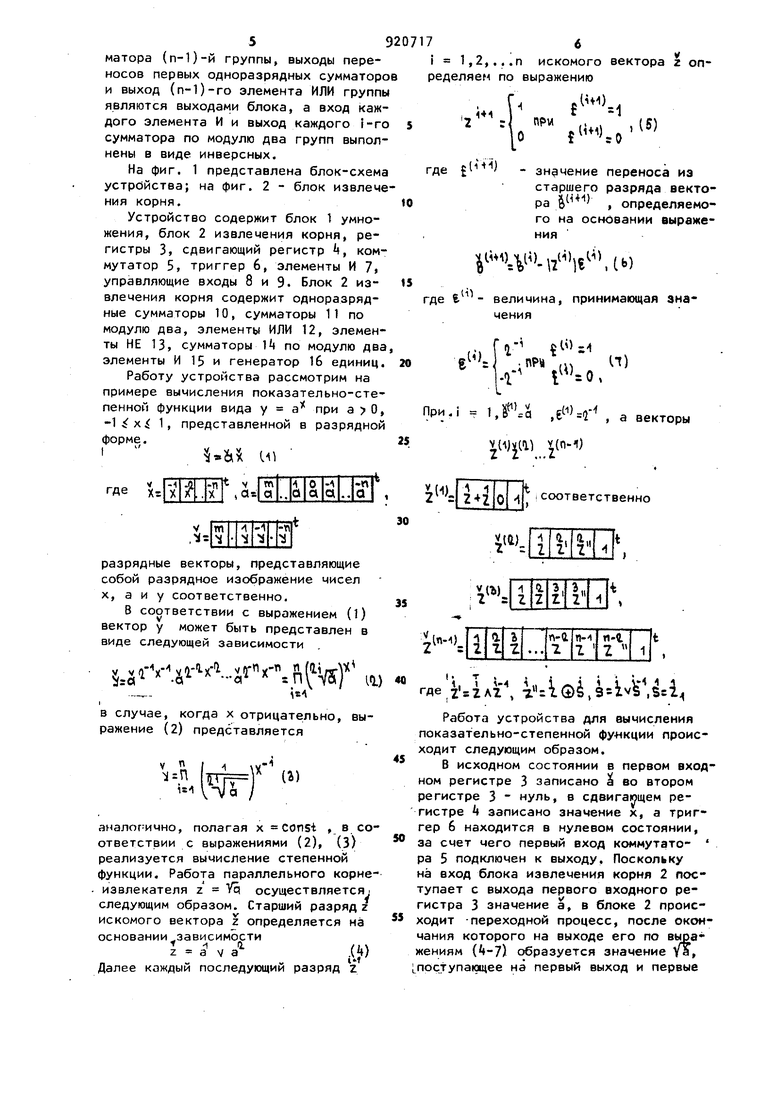

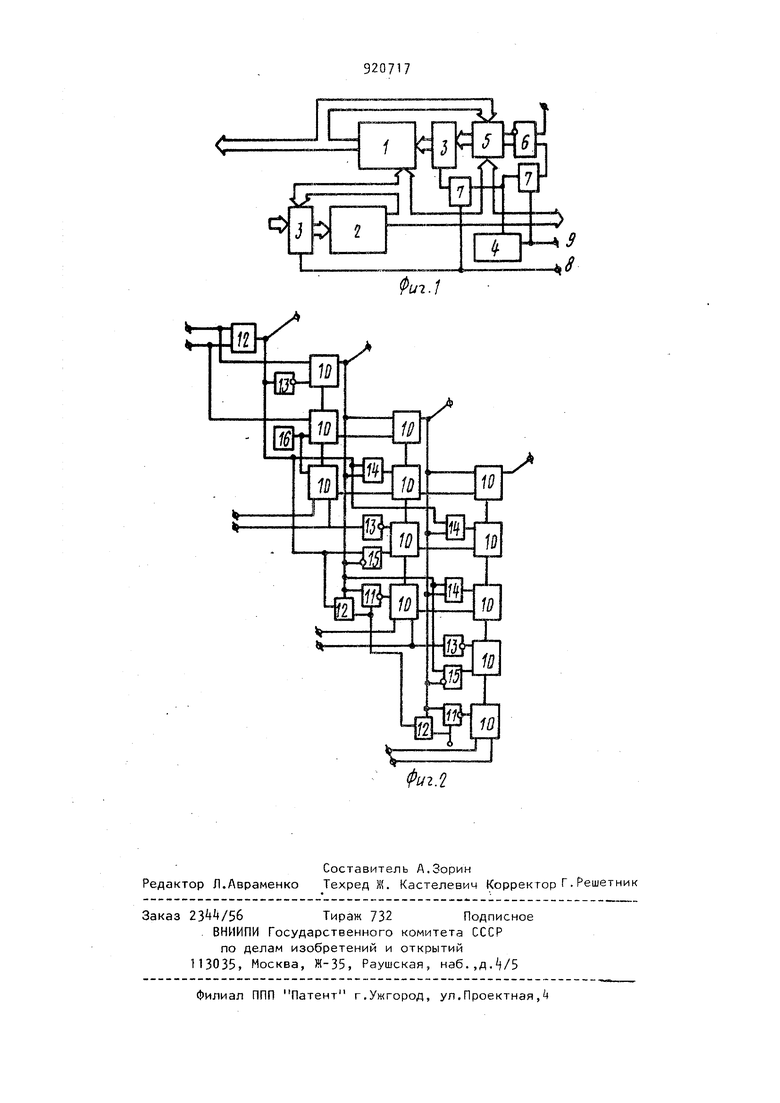

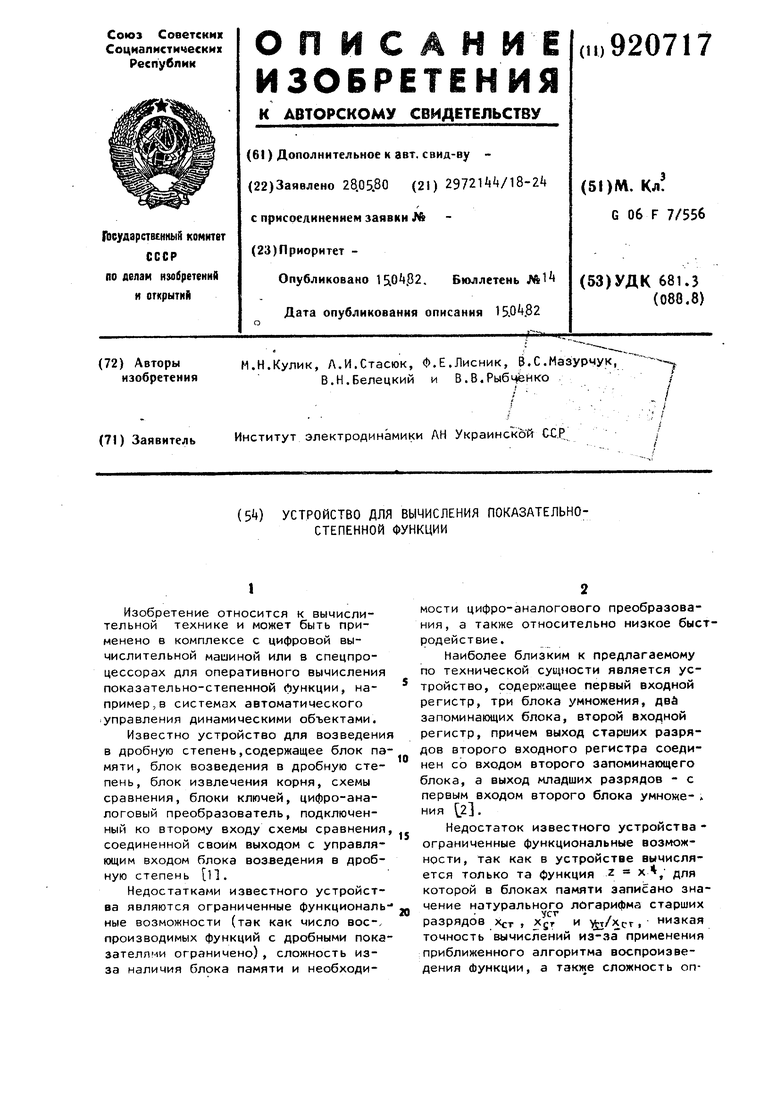

разрядов XCT , XgT и /XCT , низкая точность вычислений из-за применения приближенного алгоритма воспроизведения Функции, а также сложность определяемая наличием двух блоков памяти и трех блоков умножения. Цель изобретения - увеличение точности, расширение функциональных возможностей и упрощение устройства для вычисления показательно-степенной функции. Указанная цель достигается тем, что в устройство для вычисления показательно-степенной функции, содержащее первый регистр, блок умножения и второй регистр, дополнительно введены сдвигающий регистр, блок извлечения корня, коммутатор, триггер и два элемента И, причем выход блока извлечения корня соединен с первым выходом устройства и первыми входами блока умножения, коммутатора и первого регистра, подключенного выходом ко входу блока извлечения корня, вхо и выход второго регистра соединены соответственно с выходом коммутаИ вторым входом блока умножеторавыход которого подключен к вто, ния, рому входу коммутатора, управляющие входы которого соединены с прямым и инверсным выходами триггера, старший разряд регистра сдвига соединен с первыми входами первого и второго элементов И, выходы которых подключе ны соответственно к управляющему вхо ду второго регистра и первому входу триггера, второй вход которого является входом устройства управляющий вход первого регистра и второй вход nepBoVo элемента И соединены с первым управляющим входом устройства, второй управляющий вход которого под ключен к второму входу второго элемента И и управляющему входу сдвигового регистра, выход блока умножения является вторым выходом устройства. При этом блок извлечения корня содержит (п-1) группу последовательно соединенных одноразрядных сумматоров ( п - разрядность аргумента) , группу сумматоров по модулю два, группу элементов ИЛИ, груп пу элементов НЕ, (п-2) дополнительных группы по (n-i-l) .(где i - номе группы) сумматоров по модулю два в каждой группе, генератор единиц и группу из (п-2) элементов И, каждая i-я группа .(I 1,2,...п-1) одноразрядных сумматоров выполнена из (п + + 2 ) одноразрядных сумматоров, а группы элементов ИЛИ, элементов НЕ и сумматоров по модулю два соответ9274 ственно из (п-1) и {п-2) элементов, причем выход каждого i-ro одноразрядного сумматора (i + 1)-ой группы соединен с первым входом (j-l)-ro одноразрядного сумматора i-ой группы, второй вход первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого одноразрядного сумматора (i + 1)-ой группы, первыми входами |,--ых элементов И, элементов ИЛИ, сумматоров по модулю два групп и сумматоров.по модулю два i-ой Дополнительной группы, выходы которых соединены с вторыми входами j X (j 2, . . . п - 1) одноразрядных сумматоров 1-ой группы, вторые входы j-ых (j 2,...n-i-l) сумматоров по модулю два 1-ой дополнительной группы соединены с выходами переноса первых одноразрядных сумматоров (n-J + 1)-ых групп, выход i-ro элемента НЕ группы подключен к первому входу (п + 1 - i)-ro одноразрядного сумматора i-ой группы, второй вход которого соединен с выходом i-ro элемента И группы, подключенного своим вторым входом к выходу переноса первого одноразрядного сумматора ( i-2)-oй группы, первый вход (п -f 2 - i)-rb одноразрядного сумматора I -и группы подключен к выходу i-ro сумматора по модулю два группы, подключенного своим вторым входом к выходу i-ro элемента ИЛИ группы, второй вход которого соединен с выходом ( i + 1)-го элемента ИЛИ группы, выход (п-1)-го элемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой i-ой дополнительной группы, входом (п-1)-го элемента НЕ группы и вторым входом (п-.)-го элемента ИЛИ группы, второй вход (п + 2 - одноразрядного сумматора i-ой группы соединен с входом (2п - 21 + 1)-го разряда блока, (2п - 2i + 2)-и разряд которого подключен к третьему входу одноразрядного сумматора и входу (i-l)-ro элемента НЕ группы, входы первого и второго разрядов блока подключены ко входам (п-1)-го элемента ИЛИ группы, к первым входам соответственно первого и второго одноразрядного сумматора (п-1)-и группы, вторые входы которых соединены соответственно с выходом (n-t)-ro элемента НЕ группы и генератора единиц, подключенного к первому входу третьего одноразрядного сум59207матора (п-1)-й группы, выходы переносов первых одноразрядных сумматоров и выход (п-1)-го элемента ИЛИ группы являются выходами блока, а вход каждого элемента И и выход каждого i-ro 5 сумматора по модулю два групп выполнены в виде инверсных. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок извлечения корня.О Устройство содержит блок 1 умножения, блок 2 извлечения корня, регистры 3, сдвигающий регистр 4, коммутатор 5, триггер 6, элементы И 7« управляющие входы 8 и 9. Блок 2 из- 5 влечения корня содержит одноразрядные сумматоры 10, сумматоры 11 по модулю два, элементы ИЛИ 12, элементы НЕ 13, сумматоры И по модулю два, элементы И 15 и генератор 16 единиц. 20 Работу устройства рассмотрим на примере вычисления показательно-степенной функции вида у а при а О, -1 X 1, представленной в разрядной форме.25 bJbi ( где х .п искомого вектора z опо выражению . ПРИ .. . 10 - значение переноса из старшего разряда вектора , определяемого на основании выражения) личина, принимающая знанияГ „ .т ,. U) f , , а векторы )С11) У{П.() соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1104511A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Вычислительное устройство | 1985 |

|

SU1262485A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

разрядные векторы, представляющие собой разрядное изображение чисел X, а и у соответственно,

В соответствии с выражением (1) вектор у может быть представлен в виде следующей зависимости .4r...ft|Vsr а, « В случае, когда х отрицательно, выражение (2) представляется Л. h аналогично, полагая х COnsi , в со ответствии с выражениями (2), (3) реализуется вычисление степенной функции. Работа параллельного корне . извлекателя z Vq осуществляется следующим образом. Старший разрядz искомого вектора z определяется на основании зависимости I , z а V а Далее каждый последующий разряд z

35

Дпи) .,,a, Работа устройства для вычисления показательно-степенной фу-нкции происходит следующим образом. В исходном состоянии в первом входном регистре 3 записано а во втором регистре 3 нуль, в сдвигающем регистре k записано знамение х, а триггер 6 находится в нулевом состоянии, за счет чего первый вход коммутатора 5 подключен к выходу. Поскольку на вход блока извлечения корня 2 поступает с выхода первого входного регистра 3 значение а, в блоке 2 происходит -переходной процесс, после окончания которого на выходе его по вьшажениям ) образуется значение YS, поступающее на первый выход и первые

7

входы коммутатора 5, блока у-;н:: 1 и первого регистра 3- Usjias i:

я управляющий вход устройс i за дается импульс С, поступающ:1Й :;а первый элемент И 7 и управляиои.

вход перЕ.ого регистра 3--.

Если значение старшего разопдс; :; лектора X, поступающее к а перчу -v-j элементов И 7 равно едини1;€;;. т:, ::.;: выходе первого элемента И 7 :;vf--;/;. v ся сигнал ;, который посту; in;-: управляюи.1ий вход второго per;- i;;;s ., и по переднему фронту записывает г него значение fa, nocTynaxiiier .; коммутатор 5 на вход второг . 3. Кроме того, сигналом С по нему фронту записывает в перЕЫЙ регистр 3 значение 1;з, :::г:.: в блоке умножения 1 и 2 ходит переходной процесс а на втором управляющий вход устройства S s это Еремя подае тся сигнал Сг; . который через второй элемент И 7 по пер-, :-: фронту устанавливает григг р 6 ,: е.- ичное состояние (который наход;Ггся в этом состоянии в течение всего LixiK ла работы) за счет этого в коммуravoое

второй вход подк;

чУэ S по заднему фронту счг:- И С л p-i ализует а сдвиговом регистре 4 информа11ии влево на один разряд, После окончания переходного процессг ка первом выходе устройства сзораЗУется

значение лг. а на втором ,|Г50 1зг;еде

./7Г 4/7- 1 . г ,ние VQ --уо Ьсли значение тооогс: оаз

-1 V

ряда X вектора х ранкое;/;-;-;1и;.:, то

по сигналу С .,. значение- й , .тг;; в первый входной регисто 3; s so вт:;ЗОЙ регистр 3 - соответственно зирчз ние й-т/й , после чего процесс nofsTO-1 яется. Если х О, то во второг-; регистре 3 останется предыдуиизя информация, а после окончания последую;.:-го переходного процесса на пераом зь ходе образуется значение ЗД , в на втором -1/5 VS , образом, ;О:.ле поступления (п-1) пар сигналсэе С С ()На втором выходе устройства о вырах ению (2) образуется значение иc coмoгo вектора Y. В этом случае.,

когда в первом такте работы знз :еь;ие

1

старшего разряда х О или к старши); разрядов равно нулю, то при поступлеНИИ сигнала С ., «реализуется запись то лько в первый регистр 3 ДО тех пор, пока после очередного сдвига информации в с,о встающем регистре «-f по сигналу С,-; на выходе старшего разряда его не пол зится единица. После зтогп

.; c/i а - алогично оисан- 1У: .-iy-iae. ь:ог,г.а значение х отаицательио. то в исходном состоянии ij перзьж регистр 3 записывается знаi- iHi/ia |i и .-1СЛ1тельный процесс рее.::- яуотс,к аналоги«-но в СООТЕШТСТВИИ с ;--;ра):;ением (З), при реализации вы-; 1слкния степенней Фу1нкции величина ч. является переменной и при каждом iOBj,-: ;i;: -1Сле;-1ии яя11исг1г.;1р7ся G пер1V

. .13; .;.::тр J, 3 оначзгН-е ;; считает : разным константе о

Использование новых элементов ). Оочисленб-гя корня коммутгторр. гр;/;г iepa, и дзух 3nsMei-iTOB Il, s так-;i.;s зеден;-;е новых соязей между ниг

:vii:ecTвенке, расширяют функ иЮналь:;,:::: ,{::ог:тм. то есть Еыь:исляется лу оая гюсазательная или степенная фуг1К-ция а при а /О и .- 1 ,: х 1 , в отпи ме :;т прототипа функц1-;Й5 ;; логорем ог-раничеко количество исход-:- f ffi i :;-;формации 5 З-Э-П- СЕННОЙ в блоках ::-:;-,, а 3i-i -:K гельно узелйчи;:: ;е1 ся точнс сть вычислений за счет того,, ТО в устройстве реализуется гоч;-М; й,, а не прибл;:;-;ен:-:ь;й алгорм-тм, ч-:;;: ; г рото-гипв чт-Э позволяет вымиС -::-:,:. ;;.-чеченке соункч-пч а с наперед чг

Чгч-чсй -точностью, Ipcbie того, гфи ;--:; «ой с-груктурной организации yc-i роист со з :числения Г|О1аьа-ге,пьчо--стерэн кой, фу;1К;Л-ил нвляетс :; более ппостым по с извес-гнь м- -гак а

:Че ИЛЮЛоЗуЮТСЯ блОХИ ПаМЯТК. С

i.-e -4i:iecTQei i4o упр-Э1цает(.я оргаг:изец-|Я аь --1чсл1 ;тел1эНО-о |-1роцессг, ибо для по--::У ; г;ил результата вычислен ; v s.f. 1-3 уг1рЕЗллю1; ие входы устроит ТЕЗ О :i g |-;еобходи1:с подать только {п-1) пар импульсс3 С,. Г; „ ripi-; это;; па-рал. ЕЫМЧСЛЯ: ТСЯ (п-- }-раз значеHi-ie целой стеге -;и корил

1, yc-4JOiicTBC5 /:,ля вь: ислени покакгельно-степенной функции, содер ка;е первый регистр., блок умнох ения и

осой р«гцг.тр„ о т л и ч а ю щ е егя те;-,; iTO, с целью повышения ч/; „ в -.eiO BBsnei-ibi сдвигающий рестр, блок извле1ечия корня, коммутсю, -|-риггер и два з,лeмet тa И, при;,i зьход бпока извлечения корня соеНЕ:н с г-|ервым вы ;одом устройства и рзымк входами блока умножения, комтйтора и первого регис т}а, подклю99207ценного выходом к входу блока извлечения корня, вход и выход второго регистра соединены соответственно с выходом коммутатора и вторым входом блока умножения, выход которого подключен к s второму входу коммутатора, уп авляю- ,, щие входы которого соединены с прямым и инверсным выходами триггера,старший разряд регистра сдвига соединен с первыми входами первого и второго элементов И,10 выходы которых подключены соответственно к управляющему входу второго регистра и первому входу триггера, второй вход которого является входом устройства, управляющий вход первого ре-15 гистра и второй вход первого элемента И соединены с первым управляющим входом устройства, второй управляющий вход которого подключен к второму входу второго элемента И vi управляющему 20 входу сдвигового регистра, выход блока умножения является вторым выходом устройства. 2...Устройство по П.1, отличающееся тем, что блок извле- 25 чения корня содержит (п-1) группу последовательно соединенных одноразрядньр сумматоров(п - разрядность аргумента), группу сумматоров по модулю два,группу элементов ИЛИ, группу элементов JQ НЕ, (п-2) дополнительных группы по (n-i-1) (где i - номер группы) сумматоров по модулю два в каждой группе, - генератор единиц и группу из (п-2) элементов И, каждая i-ая группа (i 1,2,... п-1) одноразрядных сумматоров В1;1полнена из (п + 2 - i) одноразрядных сумматоров, а группы элементов ИЛИ, элементов НЕ и сумма- , торов по модулю два соответственно из (п-1) и (п-2) элементов, причем выход каждого j-ro одноразрядного сумматора (i + 1)-ой группы соединен с первым входом (j-l)-ro одноразрядного сумматора i-ой группы, второй вход „ первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого одноразрядного сумматора (1 + 1)-ой группы, первыми входами i-x элементов И, элементов ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два i-ой дополнительной группы, выходы которых соединены с вторыми входами j х (j 2,...,п-i) одноразрядных сумматоров i-ой группы, вторые входы j-ых (j 2,..., jj „. „ 17О п-1-1) сумматоров по модулю два i-ой дополнительной группы соединены с выходами переноса первых одноразрядных сумматоров(n-j + 1)-ых групп, выход i-ro элемента НЕ группы подклю первому входу (гн-1-i )-го одноразрядного сумматора i-ой группы, втоРой вход которого соединен с выходом то элемента И группы,подключенного / своим вторым входом к выходу переноса первого одноразрядного сумматсэра (-2)-ой группы, первый вход (п +2-i)J .одноразрядного сумматора i-ой группы подключен к выходу 1-го сумматора по модулю два группы, подключенного своим вторым входом к выходу i-ro . элемента ИЛИ группы, второй входкоторого соединен с выходом( + 1)-г6 элемента ИЛИ группы, выход(п-1)-го элемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой i-ой дополнительной группы, входом (п-1)-го элемента НЕ группы и вторым входом (п-2)-го элемента ИЛИ группы, второй вход (n+2-i)-ro одноразрядного сумматора i-ой группы соединен с входом. (2п-2 + 1)-го разряда блока, (2п - 21 4+ 2)-и разряд которого подключен к третьему входу одноразрядного сумматора и входу (i-l) -го элемента НЕ группы, входы первого и второго разря дов блока подключены к входам (п-1 ) элемента ИЛИ группы, к первым входам .соответственно первого и второго одноразрядного сумматоров (п-1)-и группы , вторые входы которых соединены соответственно с выходом (п-1)-го элемента НЕ группы и генератора единиц, подключенного к первому входу третьего одноразрядного сумматора (п-1)-й группы, выходы переносов первых одноразрядных сумматоров и выход (п-1)-го элемента ИЛИ группы являются выходами блока, а вход каждого элемента И и выход каждого i -го сумматора по модулю два групп выполнены в виде инверсных. Источники информации, принятые во внимание при экспертуое 1.Авторское свидетельство СССР № , кл. G 06 F 7/38, 1978. 2.Авторское свидетельство СССР № , кл. G 06 F 7/38, 1977 (протЪтип).

Авторы

Даты

1982-04-15—Публикация

1980-05-28—Подача