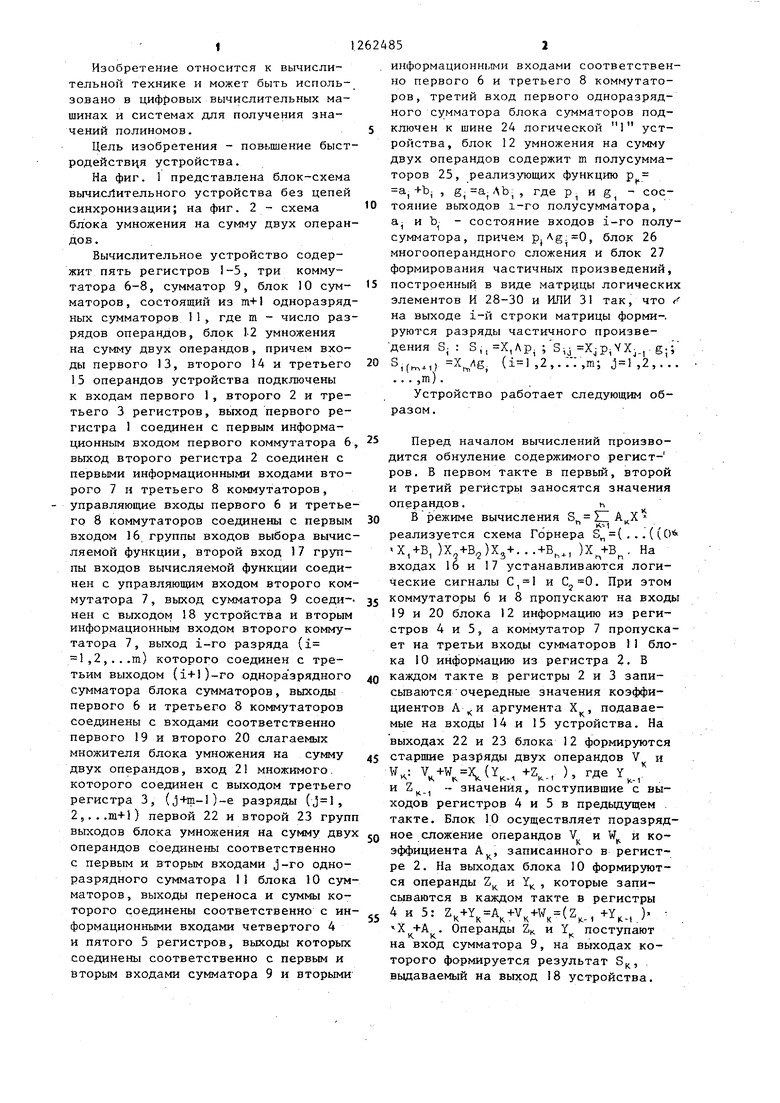

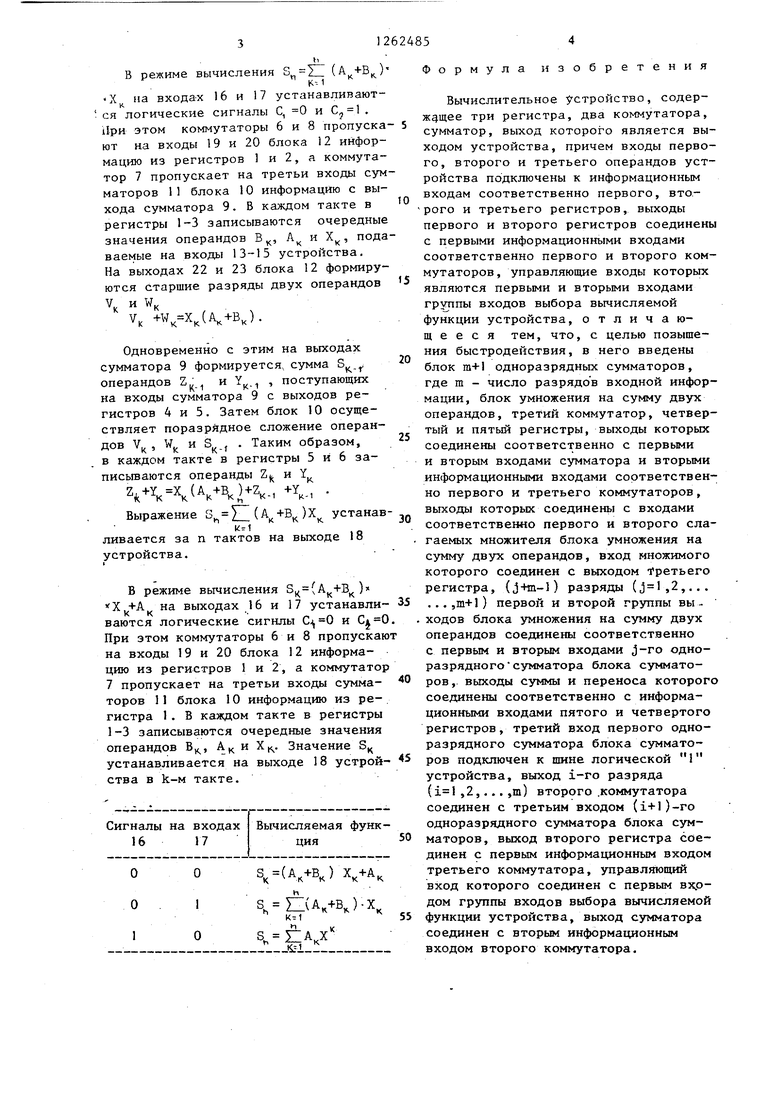

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и системах для получения значений полиномов. Цель изобретения - повышение быст родействия устройства. На фиг. 1 представлена блок-схема вычислительного устройства без цепей синхронизации; на фиг. 2 - схема блока умножения на сумму двух операн дов. Вычислительное устройство содержит пять регистров 1-5, три коммутатора 6-8, сумматор 9, блок 10 сумматоров, состоящий из т+1 одноразряд ных сумматоров I1, где m - число разрядов операндов, блок 1-2 умножения на сумму двух операндов, причем входы первого 13, второго 14 и третьего 15 операндов устройства подключены к входам первого 1, второго 2 и третьего 3 регистров, выход первого регистра 1 соединен с первым информационным входом первого коммутатора 6 выход второго регистра 2 соединен с первыми информационными входами второго 7 и третьего 8 коммутаторов, управляющие входы первого 6 и третье го 8 коммутаторов соединены с первым входом 16 группы входов выбора вычис ляемой функции, второй вход 17 группы входов вычисляемой функции соединен с управляющим входом второго ком мутатора 7, выход сумматора 9 соеди-ней с выходом 18 устройства и вторым информационным входом второго коммутатора 7, выход i-ro разряда (1 1,2,...т) которого соединен с третьим выходом {i+l)-ro одноразрядного сумматора блока сумматоров, выходы первого 6 и третьего 8 коммутаторов соединены с входами соответственно первого 19 и второго 20 слагаемых множителя блока умножения на сумму двух операндов, вход 21 множимого, которого соединен с выходом третьего регистра 3, (j+m-l)-e разряды (, 2,..,т+1) первой 22 и второй 23 групп выходов блока умножения на сумму двух операндов соединены соответственно с первым и вторым входами j-ro одноразрядного сумматора И блока 10 сумматоров , выходы переноса и суммы которого соединены соответственно с информационными входами четвертого 4 и пятого 5 регистров, выходы которых соединены соответственно с первым и вторым входами сумматора 9 и вторыми 852 информационными входами соответственио первого 6 и третьего 8 коммутаторов, третий вход первого одноразрядного сумматора блока сумматоров подключен к шине 24 логической 1 устройства, блок 12 умножения на сумму двух операндов содержит m полусумматоров 25, реализующих функцию р а,+bj , , ЛЬ. , где р и g - состояние выходов 1-го полусумматораJ а и Ъ - состояние входов i-ro полусумматора, причем р, .0, блок 26 многооперандного сложения и блок 27 формирования частичных произведений, построенный в виде матрицы логических элементов И 28-30 и ИЛИ 31 так, что на выходе 1-й строки матрицы форми-. руются разряды частичного произведения S. : S,, Х,Лр. ;s,j .,, g,; S,(,,, (i-l ,2,.:-;,m; j l,2,... ...,m). Устройство работает следующим образом. Перед началом вычислений производится обнуление содержимого регистров. В первом такте в первый, второй и третий регистры заносятся значения операндов,п В режиме вычисления реализуется схема Горнера Б„(...((0 «Х,-ЬВ, )Х,)Х,+ ...В,,, ), На входах 16 и 17 устанавливаются логические сигналы С, 1 и C,. При этом коммутаторы 6 и 8 пропускают на входы 19 и 20 блока 12 информацию из регистров 4 и 5, а коммутатор 7 пропускает на третьи входы сумматоров 11 блока 10 информацию из регистра 2. В каждом такте в регистры 2 и 3 записьгоаютсяочередные значения коэффициентов аргумента Х, подаваемые на входы 14 и 15 устройства. На выходах 22 и 23 блока 12 формируются старшие разряды двух операндов V и к: (V. ) Д Y., и Z - значения, поступившие с выходов регистров 4 и 5 в предьщущем такте. Блок 10 осуществляет поразрядное сложение операндов V и W и коэффициента А , записанного в регистре 2. На выходах блока 10 формируются операнды Z и Y, которые записываются в каждом такте в регистры 4 и 5: (Z, +Y., ) . Операнды ZK и Y поступают на вход сумматора 9, на выходах которого формируется результат 3,, выдаваемый на выход 18 устройства. () Фор в режиме вычисления Х па входах 16 и 17 устанавливают ся логические сигналы С, 0 и . ilpR этом коммутаторы 6 и 8 пропуск ют на входы 19 и 20 блока 12 инфор мацию из регистров и 2, а коммута тор 7 пропускает на третьи входы су маторов 11 блока 10 информацию с вы хода сумматора 9. В каждом такте в регистры 1-3 записываются очередны значения операндов В , Л и Х, под ваемые на входы 13-15 устройства. На выходах 22 и 23 блока 12 формиру ются старшие разряды двух операндов и WK V, ,+BJ. Одновременно с этим на выходах сумматора 9 формируется сумма 5, операндов Z, и Y. , поступающих на входы сумматора 9 с выходов регистров 4 и 5. Затем блок 10 осуществляет поразрядное сложение операндов V| , Wj, и S J . Таким образом, в каждом такте в регистры 5 и 6 записьшаются операнды Z и Y - Выражение S И (В,) устанав k-1 ливается за п тактов на выходе 18 устройства. В режиме вьмисления 5ц() Х +А на выходах 16 и 17 устанавли Баются логические сигнлы и С При этом коммутаторы 6 и 8 пропуска на входы 19 и 20 блока 12 информацию из регистров 1 и 2, а коммутато 7 пропускает на третьи входы сумматоров 11 блока 10 информацию из регистра 1. В каждом такте в регистры 1-3 записываются очередные значения операндов Вц, Ац и Х. Значение S устанавливается на выходе 18 устрой ства в k-M такте. 1262485 4 мула изобретения Вычислительное устройство, содерждщее три регистра, два коммутатора, сумматор, выход которого является выходом устройства, причем входы первого, второго и третьего операндов устройства подключены к информационным входам соответственно первого, второго и третьего регистров, выходы первого и второго регистров соединены с первыми информационными входами соответственно первого и второго коммутаторов, управляющие входы которых являются первыми и вторыми входами группы входов выбора вычисляемой функции устройства, отличающееся тем, что, с целью повыщения быстродействия, в него введены блок т+1 одноразрядных сумматоров, где m - число разрядов входной информации, блок умножения на сумму двух операндов, третий коммутатор, четвертый и пятый регистры, выходы которых соединены соответственно с первыми и вторым входами сумматора и вторыми ин(1юрмационными входами соответственно первого и третьего коммутаторов, выходы которых соединены с входами соответственно первого и второго слагаемых множителя блока умножения на сумму двух операндов, вход множимого которого соединен с выходом третьего регистра, (j-Hn-l) разряды (j l,2,... ...,m+l) первой и второй группы выходов блока умножения на сумму двух операндов соединены соответственно с первым и вторым входами j-ro одноразрядного сумматора блока сумматоров , выходы суммы и переноса которого соединены соответственно с информационными входами пятого и четвертого регистров, третий вход первого одноразрядного сумматора блока сумматоров подключен к шине логической 1 устройства, выход i-ro разряда (,2,...,т) второго .коммутатора соединен с третьим входом (i+l)-ro одноразрядного сумматора блока сумматоров, выход второго регистра соединен с первым информационным входом третьего коммутатора, управляющий вход которого соединен с первым вхрдом группы входов выбора вычисляемой функции устройства, выход сумматора соединен с вторым информационным входом второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислитель ных машинах и системах для получения значений полиномов 3..(А„+В)Х +А (A..i - -- - - f, f. к к . Цель ., .j.-,-)x к Ktl изобретения - повьшенйе быстродействия устройства - достигается за счет введения в него блока 12 умножения на сумму двух операндов, блока 10 сумматоров, состоящего из m+l одноразрядных сумматоров 1I, четвертого 4 н пятого 5 регистров и третьего коммутатора 8 с соответствующими функцио нальными связями между ними. 2 ил. (Л to Од ю 00 ел

| Устройство для вычисления значения полинома -й степени | 1978 |

|

SU769536A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1981 |

|

SU1016779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-04—Подача