(54} ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

| Управляемый делитель частоты | 1984 |

|

SU1238234A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Умножитель частоты импульсов | 1984 |

|

SU1238222A1 |

| Селектор импульсов по периоду сле-дОВАНия | 1979 |

|

SU813766A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Делитель частоты с дробным коэффициентом деления кратности 0,5 | 1979 |

|

SU788387A1 |

| Перестраиваемый делитель частоты следования импульсов | 1984 |

|

SU1213542A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1001534A1 |

| Устройство для разделения импульсов двух последовательностей | 1984 |

|

SU1238223A1 |

Изобретение относится к импульсной технике. Известен делитель частоты следования импульсов содержащий два триггера,, счетные входы которых соединеныс входной шиной, прямой выход первого триггера соединен с 1-входом второго триггера, инверсный выход второго триггера соединен с 1-входом первого триггера 1. Недостагок данного устройства - невысокие стабильность работы и быстродействие. . Наиболее близким по технической сущности к изобретению является делитель частоты следрвания импульсов, содержащий два D-триггера и два элемента И-НЕ, первый вход первого из которых соединен с С-входом первого D-триггера и входной щиной, второй вход - с прямым выходом первого D-триггера, а выход - с С-выходом второго D-триггера, инверсный выход которого подключен к S-входу первого триггера и D-входу второго триггера, причем ,D-BXOA первого триггера соединен с его инверсным выходом, а прямой выход - с первым входом второго элемента И-НЕ второй вход которого соединен с инверсным выходом второго D-триггера 2. Однако устройство обладает недостаточной надежностью работы и невысоким быстродействием. Цель изобретения - повышение надежности работы при одновременном повыщении быстродействия. С этой целью в делитель частоты следования импульсов, содержащий два D-триггера и два элемента И-НЕ, первый вход первого из которых соединен с входной щиной, а выход - с С-входом первого Dтриггера, инверсный выход которого соединен с его D-входом и первым входом второго элемента И-НЕ, второй вход котор.ого соединен с прямым выходом второго D-триггера, введен инвертор, вход которого соединение первым входом первого элемента И-НЕ, второй вход которого подключен к выходу второго элемента И- НЕ, а выход соединен с С-входом второго D-триггера, D-вход которого соединен с прямым выходом первого D-триггера, а а R-вход с R-входом первого D-триггера и с шиной установки нуля.

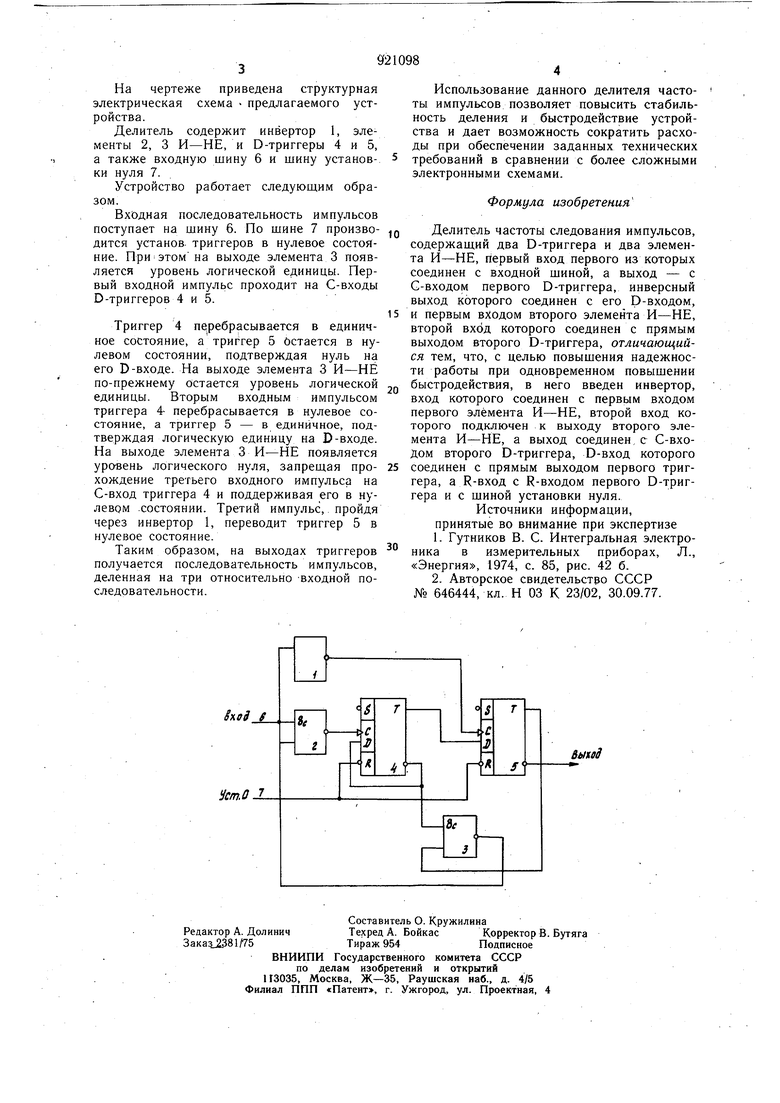

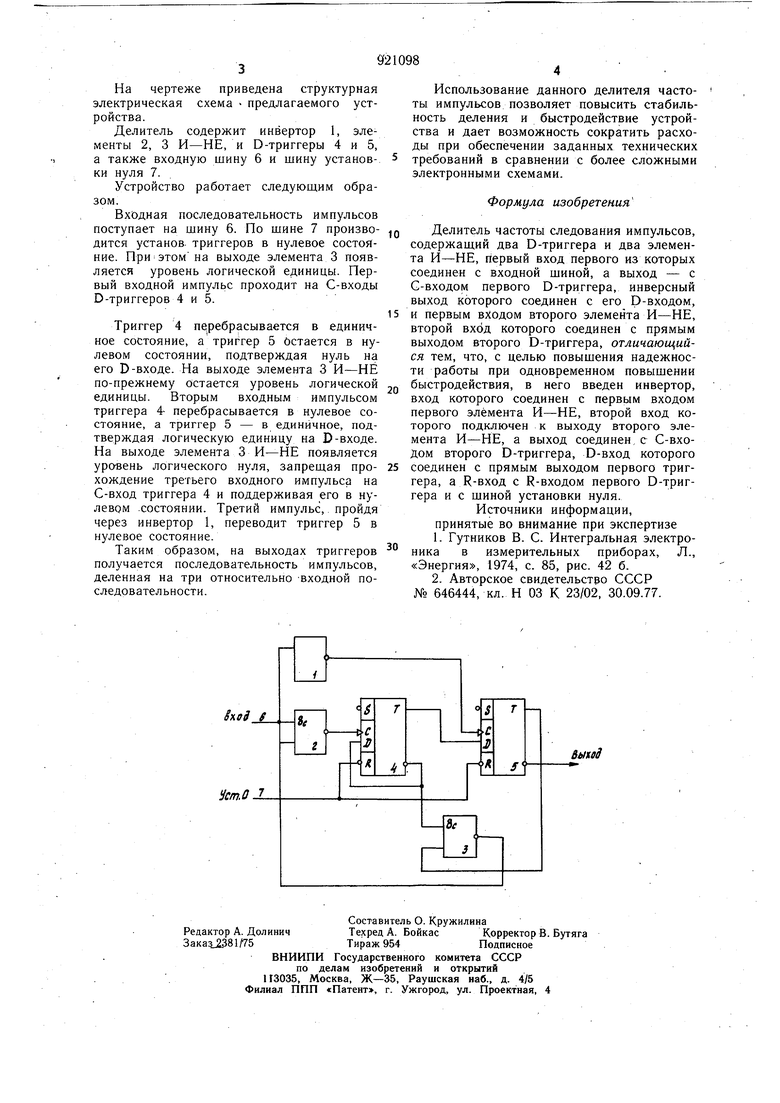

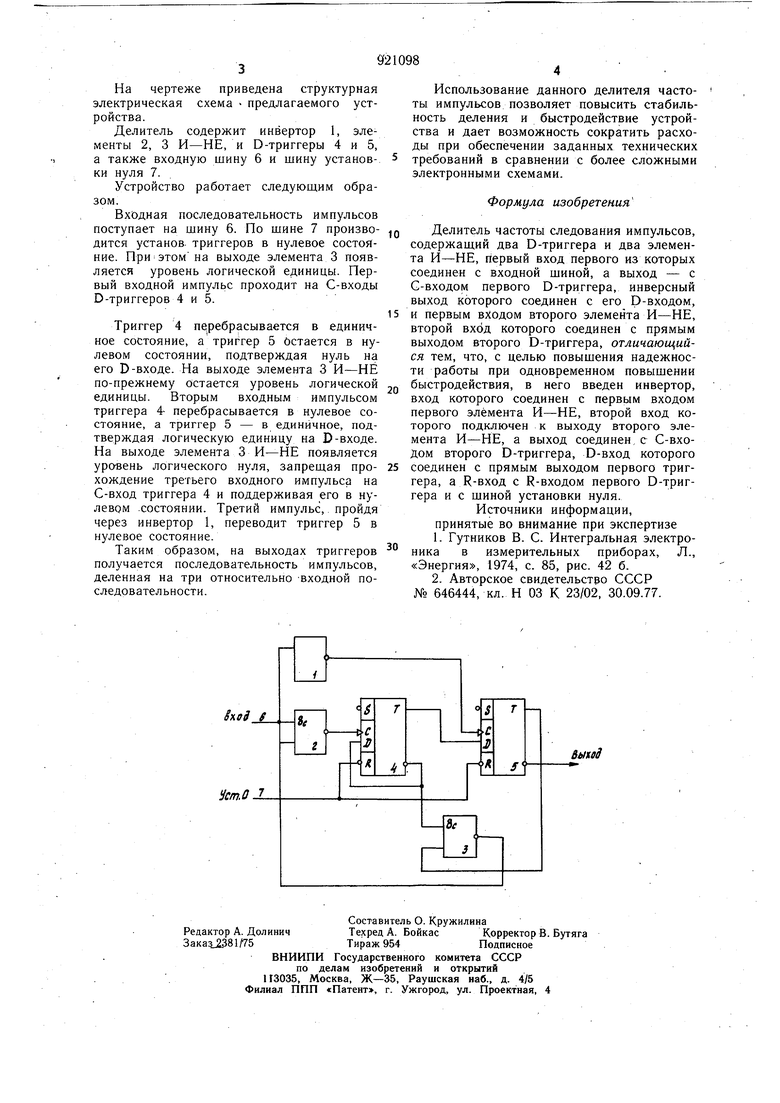

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Делитель содержит инвертор 1, элементы 2, 3 И-НЕ, и D-триггеры 4 и 5, а также входную шину 6 и шину установки нуля 7.

Устройство работает следующим образом.

Входная последовательность импульсов поступает на шину 6. По шине 7 производится установ. триггеров в нулевое состояние. Приiэтом на выходе элемента 3 появляется уровень логической единицы. Первый входной импульс проходит на С-входы D-триггеров 4 и 5.

Триггер 4 перебрасывается в единичное состояние, а триггер 5 Остается в нулевом состоянии, подтверждая нуль на его D-входе. На выходе элемента 3 И-НЕ по-прежнему остается уровень логической единицы. Вторым входным импульсом триггера 4- перебрасывается в нулевое состояние, а триггер 5 - в единичное, подтверждая логическую единицу на D-входе. На выходе элемента 3 появляется уровень логического нуля, запрещая прохождение третьего входного импульса на С-вход триггера 4 и поддерживая его в нулевом .состоянии. Третий импульс, пройдя через инвертор 1, переводит триггер 5 в нулевое состояние.

Таким образом, на выходах триггеров получается последовательность импульсов, деленная на три относительно -входной последовательности.

Использование данного делителя частоты импульсов позволяет повысить стабильность деления и быстродействие устройства и дает возможность сократить расходы при обеспечении заданных технических требований в сравнении с более сложными электронными схемами.

Формула изобретения

Делитель частоты следования импульсов, содержаш.ий два D-триггера и два элемента И-НЕ, первый вход первого из которых соединен с входной шиной, а выход - с G-входом первого D-триггера, инверсный выход которого соединен с его Р-ВХОДОМ, и первым входом второго элемента И-НЕ, второй вход которого соединен с прямым выходом второго D-триггера, отличающийся тем, что, с целью повышения надежности работы при одновременном повышении быстродействия, в него введен инвертор, вход которого соединен с первым входом первого элемента И-НЕ, второй вход которого подключен к выходу второго элемента И-НЕ, а выход соединен, с С-входом второго D-триггера, D-вход которого соединен с прямым выходом первого триггера, а R-вход с R-входом первого D-триггера и с шиной установки нуля.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-04-15—Публикация

1980-04-21—Подача